Fターム[5F038BE08]の内容

Fターム[5F038BE08]に分類される特許

1 - 20 / 177

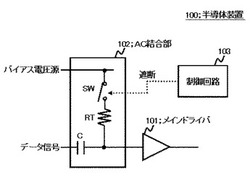

半導体装置及びそのテスト方法

【課題】データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置のDCテストの実施には、振幅を維持できないという問題がある。そのため、データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置であって、DCテストを可能にする半導体装置が、望まれる。

【解決手段】半導体装置は、データ信号を外部に出力するメインドライバと、データ信号が伝達する配線と接続されているコンデンサと、一端がコンデンサと接続され、他の一端がバイアス電圧源に接続されている終端抵抗と、バイアス電圧源と終端抵抗との間に接続されている第1のスイッチと、を含むAC結合部と、テストモード時にAC結合部のバイアス電圧源と終端抵抗との接続を、第1のスイッチにより遮断する制御回路と、を備える。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜の漏れ電流試験に影響を与えることなく、ゲート・ソース間に抵抗を挿入した半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置は、ゲート電極及びソース電極間に抵抗が挿入されたトランジスタを内蔵する半導体装置であって、ゲート電極及びソース電極間に、抵抗に対して直列に挿入されたダイオードを備えることを特徴とする。

(もっと読む)

半導体チップ

【課題】チップ面積が小さく低コストで誤動作が発生し難い半導体チップを提供する。

【解決手段】半導体チップ1をパッケージ3に搭載する場合は80個のパッドPAをパッケージ3の80個の端子TAに接続し、半導体チップ1をパッケージ5に搭載する場合は100個のパッドPA,PB,PCをパッケージ5の100個の端子TAに接続する。半導体チップ1の内部回路は、電極E1,E2が絶縁されている場合は80端子のマイクロコンピュータ4として動作し、電極E1,E2がボンディングワイヤWの端部によって短絡されている場合は100端子のマイクロコンピュータ4として動作する。したがって、パッケージの端子数を設定する専用パッドが不要となる。

(もっと読む)

半導体装置

【課題】未使用端子がオープンのままである場合においても、未使用端子とその隣に位置する端子が短絡したことを検出できるようにする。

【解決手段】抵抗素子62は、一端が端子200に接続している。電圧選択部64は、抵抗素子62の他端を電源及び接地の一方に選択的に接続させる。電圧測定回路70は、抵抗素子62の一端(すなわち端子200と接続する側の端部)の電圧を測定する。端子制御回路20は、スイッチ素子66のオン/オフを制御する。接続制御回路30は、電圧選択部64を制御する。

(もっと読む)

半導体装置

【課題】 本実施形態は、出力ドライバのドライブ能力のキャリブレーション精度を向上することが可能な半導体装置を提供する。

【解決手段】 第1、第2のプルアップドライバユニットPUDUa、PUDUbは、プルアップドライバを調整する。プルダウンドライバユニットPDDUbは、プルダウンドライバを調整する。キャリブレーション回路CBCは、プルアップドライバのキャリブレーション時、基準電圧VREFと、基準抵抗RZQに基づく第1のプルアップドライバの出力電圧を比較して第1、第2のプルアップドライバユニットのドライブ能力を決定し、プルダウンドライバのキャリブレーション時、基準電圧と、第2のプルアップドライバとプルダウンドライバの接続ノードの電圧を比較してプルダウンドライバのドライブ能力を決定する単一の比較器COMPを有している。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

半導体集積回路装置

【課題】内部コアエリアのトランジスタを犠牲にすることなく、周辺エリアのトランジスタを用いてリップルフィルタによる電源供給回路を構成する。

【解決手段】入出力回路を構成するためのトランジスタが配列されてなる周辺エリア(図2の12に相当)をチップ上に有する半導体集積回路装置であって、ドレインを電源に接続し、ソースを負荷側に接続し、ゲートを容量素子(図2のC1)を介して交流的に接地する第1のトランジスタ(図2のMN1)と、容量素子をゲート・基板間によって形成する第2のトランジスタと、を周辺エリアに備える。

(もっと読む)

半導体集積回路のテスト回路及び方法

【課題】ウェハ上の単一チップに形成された貫通ビアの不良の可否をテストすることができ、またパッケージングされた半導体集積回路に形成された貫通ビアの不良の可否をテストすることができる半導体集積回路のテスト回路及び方法を提供する。

【解決手段】半導体集積回路のテスト回路1は貫通ビア100、電圧駆動部200及び判定部300を含む。前記貫通ビア100は入力電圧V1を受信する。前記電圧駆動部200は前記貫通ビア100と連結されて前記入力電圧V1を受信し、テスト制御信号EN_P,EN_Nに応答して前記入力電圧V1のレベルを変化させてテスト電圧VTを生成する。前記判定部300は前記入力電圧V1及び前記テスト電圧VTを比較して結果信号を出力する。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

半導体装置

【課題】実行するプログラムの種類又は発生する異常の種類などの、動作開始後の状況に合わせて外部端子の状態をプログラマブルに設定する。

【解決手段】プログラム処理回路によるデータ処理状態、プログラム処理回路が実行するプログラム若しくはデータ処理の種類、あるいはデータ処理による異常の種別毎に、異常発生時の入出力端子の端子状態を制御する制御データを予め不揮発性記憶部(140)に保存する。プログラム実行前若しくはプログラムの実行時に逐次に不揮発性記憶部に制御データを特定する検索キーを設定し、異常が発生した場合は、当該検索キーに基づいて参照された制御データに従って、入出力端子の状態をプルアップ、プルダウン、ハイインピーダンス又は前値保持の状態に設定する。

(もっと読む)

半導体装置

【課題】複数の半導体チップの各々の信号端子が共通の外部端子に接続される場合であっても、半導体装置のオープン不良を検出する。

【解決手段】半導体装置は、複数の半導体チップと、外部と接続される電源端子、第1及び第2の外部端子と、を備え、複数の半導体チップのそれぞれは、第1の信号端子(第1の信号パッドT1)に供給される信号に基づくクロック信号によって計数を行うカウンタ部42と、複数の半導体チップの中で自己の半導体チップを固定的に識別し、識別情報を出力する識別情報認識部と、カウンタ部42の出力と識別情報を比較し、比較した比較結果に基づいて、第2の信号端子(第2の信号パッドT2)と電源端子との導通/非導通状態を制御する比較回路43と、を有し、複数の半導体チップの各々の第1の信号端子は、共通の第1の外部端子に接続され、複数の半導体チップの各々の第2の信号端子は、共通の第2の外部端子に接続される。

(もっと読む)

半導体装置

【課題】リーク電流を従来よりも抑えること。

【解決手段】本発明の半導体装置1は、外部から信号を供給可能な入力端子10と、内部回路30と、制御部40と、バッファ回路20とを具備している。制御部40は、起動時から所定時間が経過するまでの間にマスク解除信号MASK“H”を出力する。バッファ回路20は、入力端子10に供給される電圧VDD又は電圧GNDを表す信号をマスク解除信号MASK“H”に応じて内部回路30に出力する。本発明の半導体装置1では、外部から入力端子10に信号が供給されているときにノイズが発生しても、バッファ回路20が入力端子10から内部回路30への伝送を有効にする時間以外は無効にしている。このため、マスク回路26によるバッファ回路20と内部回路30との切り離しにより、内部回路30への貫通電流を防止することができる。

(もっと読む)

電子装置

【課題】大型化を招くことなく装置に関する情報を外部から好適に読み取り得る電子装置を提供する。

【解決手段】半導体チップ10は、装置に関する情報が外部から読み取り可能に記憶されるRFIDチップ30を搭載する回路ブロック11がモールド部材16によりモールドされてパッケージ化されている。このRFIDチップ30は、回路上に形成される複数のパッド13のうちモールド部材16によりモールドされた状態で外部に接続されていない検査用パッド20上に配置されている。

(もっと読む)

半導体装置

【課題】電源電圧の変動に対して高い効果が得られるデカップリングキャパシタを搭載可能な半導体装置を提供する。

【解決手段】半導体装置10は、半導体基板23と、半導体基板23を貫通し、かつ電源ライン12及び接地ライン13に電気的に接続された複数の貫通電極21と、半導体基板23の裏面に設けられ、かつ複数の貫通電極21に電気的に接続され、かつデカップリングキャパシタ40が実装される複数の端子22とを含む。

(もっと読む)

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

TSVベースの3次元積層ICのためのテストアーキテクチャ

入出力端子制御回路

【課題】フローティングかどうかの識別信号が不要な入出力端子制御回路を提供する。

【解決手段】フローティング検出回路51は、半導体チップの内部回路に対し外部信号を入出力する入出力端子Tに接続され、当該入出力端子Tの電気的なフローティング状態を検出する。電位固定スイッチSWは、フローティング検出回路51の検出結果に基づいて、当該入出力端子Tをハイレベルまたはローレベルの電源電圧で電位固定する。

(もっと読む)

1 - 20 / 177

[ Back to top ]