Fターム[5F038BH13]の内容

Fターム[5F038BH13]に分類される特許

201 - 220 / 1,330

静電気保護素子及びその製造方法

【課題】リーク電流の少ない静電気保護素子を提供する。

【解決手段】半導体基板100nと、半導体基板内に形成され、第1の導電型の不純物が拡散された第1のウェル101と、第1のウェル内に、第1のウェルの一部の領域を挟んで形成され、第2の導電型の不純物が拡散されたコレクタ領域110及びエミッタ領域112と、第1のウェル内に、前記エミッタ領域と分離する第1の分離領域102を挟んで形成され、第1のウェル内に拡散された不純物の濃度よりも高い濃度の、第1の導電型の不純物が拡散されたベース拡散領域114と、前記エミッタ領域下方から前記エミッタ領域と前記ベース拡散領域との間までの第1のウェル内の領域に形成され、第2の導電型の不純物が拡散された拡散領域103aとを備えた静電気保護素子。

(もっと読む)

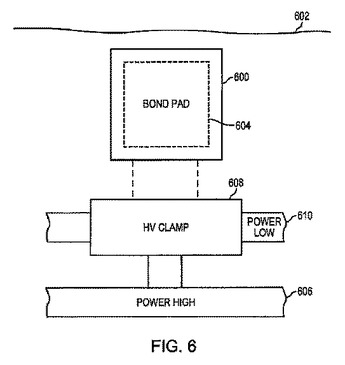

RFIC用の高電圧、高周波数ESD保護回路

高電圧および高周波数動作を必要とするRFICのための改良されたESD保護回路が開示される。プリチャージ回路およびダイオードネットにコンバインされたカスコード接地ゲートNFET(GGNFET)は低キャパシタンスおよび高ターンオン電圧の正のESD保護クランプをもたらす。正のESD保護クランプは正電圧のESDパルスの期間中にICに保護を提供する。負のESD保護クランプの例示的な実施形態が開示され、ここでは、負のESD電圧パルスに対して保護を提供するための、ダイオードネットと一緒にバイアス回路またはチャージポンプとカスコード接地スナップバックゲートNFETとの組合せを提供するように、プリチャージ回路の代わりにバイアス回路またはチャージポンプが使用される。正および負のESD保護クランプの組合せは、正または負電圧のESDパルスの期間中にICに保護を提供する。 (もっと読む)

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

ESD保護素子、半導体装置およびプラズマディスプレイ装置

【課題】 製造コストを上昇させることなくSOI構造の高耐圧半導体集積回路装置に組み込むことができるとともに、チップ面積の増大を抑制できるESD保護素子を提供する。

【解決手段】

ESD保護素子は、埋め込み絶縁膜2上に形成され、素子分離領域17で囲まれた第1導電型半導体層3、半導体層3に形成された第1導電型第1半導体領域8、第1導電型第1半導体領域8から離間して半導体層3に形成された第2導電型第1半導体領域16、第2導電型第1半導体領域16に形成され、それより高不純物濃度の第2導電型第2半導体領域10、第2導電型第2半導体領域10に形成された高不純物濃度の第1導電型第2半導体領域9からなる構造を有している。また、第1電極12および第2電極13は高耐圧半導体回路に電気的に接続され、第2導電型第1および第2半導体領域16、10は電気的にフローティング状態となっている。

(もっと読む)

半導体装置

【課題】 占有面積の増加もなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を得ることを目的とする。

【解決手段】 絶縁膜が埋め込まれたトレンチ素子分離領域と、凹部に周囲をゲート絶縁膜で覆われたゲート電極が埋め込まれたトレンチチャネル領域と、絶縁膜が埋め込まれた凹部の周囲を濃いN型の拡散層で覆ったトレンチドレイン領域とが形成されており、ESD保護用のN型MOSトランジスタのチャネル領域には、トレンチチャネル領域が形成され、なおかつESD保護用のN型MOSトランジスタのドレイン領域には、トレンチドレイン領域が形成されている。

(もっと読む)

半導体装置

【課題】 占有面積の増加を少なく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 ESD保護用のN型MOSトランジスタのドレイン領域は、トレンチ分離領域の側面および下面に設置されたドレイン領域と同一の導電型の不純物拡散領域によって形成されたドレイン延設領域を介して、ドレイン領域と同一の導電型の不純物拡散領域によって形成されたドレインコンタクト領域と電気的に接続している半導体装置とした。

(もっと読む)

半導体回路及び半導体回路装置

【課題】 外部から瞬間的なパルスが入力されてもレジスタ等を復旧することが可能な半

導体回路及び半導体回路装置を提供する。

【解決手段】 外部と入出力情報を受け渡す端子部21aと、前記端子部21aの入力電

圧と、第1の参照電圧とを比較し、前記端子部21aの入力電圧が前記第1の参照電圧よ

り高い場合に、第1の信号を送信する第1のI/Oディテクタ部21bと、前記第1の信

号を受信した場合に、リセット信号を送信するリセット部24と、I/Oディテクタ部2

1bからの信号をラッチするラッチ部を具備することを特徴とする半導体回路。

(もっと読む)

半導体装置

【課題】 占有面積の大きな増加なく、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護素子を得ることを目的とする。

【解決手段】 素子分離にシャロートレンチ構造を有するESD保護素子を有する半導体装置において、ESD保護素子は、中央に外部接続端子からの信号を受けるN型の領域が配置され、外部接続端子からの信号を受けるN型の領域の側面ならびに底面を囲むようにP型の領域が配置され、P型の領域の側面および底面を囲むように埋め込みN型の領域が配置され、埋め込みN型の領域の周囲にP型の基板端子領域が配置され、P型の基板端子領域の周囲にトレンチ分離領域が配置された半導体装置とした。

(もっと読む)

半導体装置

【課題】 バンプパッドおよびプローブテスト用パッドを介して流入する静電気から保護され得る半導体装置を提供すること。

【解決手段】 チップオンチップ(Chip On Chip)構造を有する半導体集積装置において、データ入力のためのバンプパッドと、バンプパッドを介して外部から流入する静電気を放電させる第1静電気放電部と、バンプパッドより大きいサイズを有し、データ入力のためのプローブテスト用パッドと、プローブテスト用パッドを介して外部から流入する静電気を放電させる第2静電気放電部と、バンプパッドまたはプローブテスト用パッドから伝達されるデータをバッファリングする入力バッファ部とを備える。

(もっと読む)

横型半導体装置

【課題】SOI基板のシリコン半導体層を薄膜化することによって横型の半導体装置の耐圧を高め、しかも大電流の通電時にシリコン半導体層が熱破壊されるまでの時間が短くなることを防止する。

【解決手段】IGBT1では、支持基板11と埋め込み酸化シリコン層12とシリコン半導体層13と絶縁層23とが順に形成されている。シリコン半導体層13は、エミッタ電極20に接しているエミッタ領域14と、コレクタ電極21に接しているコレクタ領域15と、ボディ領域17及びバッファ領域19の一部とドリフト領域16とからなる中央半導体領域とを備えている。絶縁層23の一部は、酸化シリコンよりも熱伝導性が高い材料で形成されているとともにドリフト領域16の真上に広がっている高熱伝導層27である。

(もっと読む)

半導体装置

【課題】ラッチアップを利用したESD保護のための半導体装置において、ラッチアップ発生電圧を任意の値に設定すること。

【解決手段】半導体装置300は、P型基板301と、P型基板301の表面に形成されたN型ウェル領域302と、N型ウェル領域302の表面上のP+型拡散領域303及びN+型拡散領域304と、P型基板301とN型ウェル領域302との境界上に配置された酸化膜305と、酸化膜305の一部の上に配置されたポリSi306と、P型基板301の表面上のP+型拡散領域307及びN+型拡散領域308とを備える。フローティング電極309は、ポリSi306及びN型ウェル領域302とそれぞれ容量結合するように配置されている。ポリSi306は接地されている。

(もっと読む)

トランジスタ型保護素子および半導体集積回路

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、エミッタ領域5B、第1コレクタ領域6B、第2コレクタ領域8Bおよび抵抗性接続領域9を有する。第1および第2コレクタ領域6B,8Bは、エミッタ領域5Bと所定の距離以上だけ離れ、お互いの間も互いに離れており、その間が抵抗性接続領域9によって接続されている。抵抗性接続領域9は薄膜抵抗層によって代替できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 アバランシェ耐量が高く、保護する高耐圧トランジスタと同製造工程を用いて形成できる高耐圧ESD保護ダイオードを提供する。

【解決手段】 カソード領域8を構成するN型低濃度半導体基板1とアノード領域7を構成するP型低濃度拡散領域14から形成されるPN接合部の基板表面上に、ゲート酸化膜12を形成し、ゲート酸化膜12とフィールド酸化膜4にまたがって設けられたゲート電極13をゲートプラグ28を介してアノード電極20と電気的に接続することを特徴とする構造により、アバランシェ降伏時にPN接合における電界が緩和し、高アバランシェ耐量を得る。またフィールド酸化膜4の長さを変化させることで、耐圧を調整できる。

(もっと読む)

半導体装置

【課題】保護対象回路に印加されるストレス電圧を緩和しつつ、低い動作電圧でESDサージの放電動作を行うことができる静電保護回路を提供する。

【解決手段】半導体装置が、電源線と、電源線に接続された電源線パッドと、接地線と、接地線に接続された接地線パッドと、信号入力パッドと、電源線パッド、接地線パッド、及び信号入力パッドのうちの第1パッドに印加されたESDサージを第1パッドと異なる第2パッドに放電するように構成されたメイン保護回路部と、保護対象回路と、保護対象回路に接続される接続ノードと、信号入力パッドと接続ノードとの間に接続された抵抗素子と、サブ保護回路部とを備えている。サブ保護回路部が、ソースが接続ノードに接続され、ドレインが接地線に接続され、ゲートとバックゲートが電源線に接続されたPMOSトランジスタと、ソースが接続ノードに接続され、ドレインが電源線に接続され、ゲートとバックゲートが接地線に接続されたNMOSトランジスタの少なくとも一方を備える。

(もっと読む)

半導体装置

【課題】工程の増加や占有面積の大きな増加なく、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】素子分離にシャロートレンチ構造を有するESD保護用のN型MOSトランジスタを有する半導体装置において、ESD保護用のN型MOSトランジスタのドレイン領域に接したP型の領域に側面および底面を囲まれた前記外部接続端子からの信号を受けるN型の領域を形成した。

(もっと読む)

半導体装置およびその電力供給方法

【課題】基板上に集積回路(半導体素子)を実装してなる半導体装置において、集積回路における発熱の抑制を行うと共に、静電気放電によるノイズから内部回路を保護する。

【解決手段】複数の出力セル101を有する液晶ドライバにおいて、出力セル101の構成要素であるオペアンプ105は、半導体素子である液晶ドライバ内に形成された電源配線109aに接続されている。また、半導体素子を実装する基板上にバイパス配線201が形成され、バイパス配線201は、電源配線109aに対して、全ての出力セルのオペアンプ105毎にバンプ203を介して接続される。さらに、バイパス配線201は、第1の部分201aと第2の部分201bとによって半導体素子の電源配線109上のESD保護素子205を挟んで配置される。

(もっと読む)

非線形素子、該非線形素子を有する表示装置および該表示装置を有する電子機器

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有するトランジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms>χ≧φmdの関係になるように構成し、トランジスタのゲートとドレインを電気的に接続することで、整流特性の良い非線形素子を実現することができる。

(もっと読む)

半導体集積装置

【課題】ダイオードと電流制限抵抗の配置関係を最適化することにより、半導体集積装置の短辺方向の縮小し、占有面積が狭く製造単価の安い半導体集積装置を実現する。

【解決手段】ダイオードを分割して個々のサイズを小さくし、横方向配置の分割ダイオード1,2間で、かつ横方向配置の分割ダイオード3,4間に電流制限抵抗6を横方向に配置することにより、半導体集積装置の短辺方向の寸法縮小が可能となる静電気保護回路10のレイアウトを得ることができる。

(もっと読む)

半導体装置

【課題】 半導体装置の内部回路をESD破壊から保護しつつ、電源電圧の瞬間的な変動による誤動作を防止する。

【解決手段】 第1の電源端子および第2の電源端子と、第1の電源端子と第2の電源端子との間に接続された内部回路と、第1の電源端子と第2の電源端子との間において内部回路と並列に接続された保護回路と、を備え、保護回路は、第1の電源端子と第2の電源端子との間において内部回路と並列に接続された抵抗及び第1のコンデンサの直列回路と、直列回路と並列に接続されるとともに、抵抗と第1のコンデンサとの接続点の電圧に応じて制御される第1のMOSトランジスタと、抵抗と並列に接続され、第1の電源端子と第2の電源端子との間に電源電圧が印加されてから遅延してオンとなり第1のMOSトランジスタをオフするように接続点の電圧を変化させるスイッチ回路と、を備える。

(もっと読む)

集積回路装置及び電子機器

【課題】スリムな細長の集積回路装置及びこれを含む電子機器の提供。

【解決手段】集積回路装置は、D1方向に沿って配置される第1〜第Nの回路ブロックCB1〜CBNと、CB1〜CBNのD2方向側に設けられる第1のインターフェース領域12と、CB1〜CBNのD4方向側に設けられる第2のインターフェース領域14を含む。回路ブロックCB1〜CBNはデータドライバブロックDBとそれ以外の回路ブロックを含み、第1のインターフェース領域12、回路ブロックCB1〜CBN、第2のインターフェース領域14のD2方向での幅を、各々、W1、WB、W2とした場合、集積回路装置のD2方向での幅WはW1+WB+W2≦W<W1+2×WB+W2となる。

(もっと読む)

201 - 220 / 1,330

[ Back to top ]