Fターム[5F038CA11]の内容

Fターム[5F038CA11]に分類される特許

1 - 17 / 17

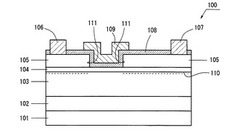

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】主面をm面とするIII 族窒化物半導体で構成されたHFETにおいて、正のしきい値電圧を高めること。

【解決手段】HFET100は、凹凸加工されたa面サファイア基板101上に、m面を主面とするGaNからなるバッファ層102、ノンドープのGaNからなるチャネル層103、ノンドープのAlGaNからなる障壁層104、酸素ドープのn−AlGaNからなるキャリア供給層105を有している。キャリア供給層105は2つの領域に分離して形成されている。キャリア供給層105は、障壁層104上に選択的に再成長させて形成した層である。ゲート電極109にバイアスを印加しない状態では、ゲート電極109直下に2DEGが形成されないため、正のしきい値電圧を高めることができる。

(もっと読む)

炭化珪素絶縁ゲート電界効果トランジスタを用いたインバータ回路および論理ゲート回路

【課題】動作速度を高速化できる SiC MISFETで構成された論理ゲート回路デバイスを得る。

【解決手段】nチャネルエンハンスメント型SiC MISFET(22)と、nチャネルデプリーション型SiC MISFET(22、22b)とでインバータ、NAND/NOR論理ゲート回路を構成する。

(もっと読む)

半導体集積回路装置

【課題】対称配置される回路の特性バラツキを低減する。

【解決手段】固体撮像装置70では、中央部に設けられる画素領域20の上端側に並列配置される複数の増幅回路が、画素領域20の下端側に並列配置される複数の増幅回路に対して対称配置される。増幅回路はゲート長寸法が同一で並列配置される第1及び第2のフィンガーを有するトランジスタから構成される。第2のフィンガーのチャネル長方向は、第1のフィンガーのチャネル方向の逆方向である。画素領域20の上端側の増幅回路のトランジスタのチャネル長方向は、画素領域20の下端側の増幅回路のトランジスタのチャネル長方向と同一に設定される。

(もっと読む)

ICチップの基板が薄くなった箇所を検出する装置

【課題】ICチップの基板が薄くなった箇所を検出する装置を提供する。

【解決手段】ICチップの基板が薄くなった箇所を検出する装置は、基板の活性領域に、ホイートストン・ブリッジとして接続された、棒形状の分散された複数の抵抗を備え、ブリッジの第1の対向する抵抗の組は、第1の方向に向いており、ブリッジの第2の対向する抵抗の組は、第2の方向に向いており、第1及び第2の方向は、基板が薄くなった箇所がブリッジの不均衡値を変化させる方向である。

(もっと読む)

キャパシタ構造及び半導体素子

【課題】キャパシタ構造において、電極間を流れる電流を抑制しつつ電極間の絶縁層を極限まで薄層化する。

【解決手段】ゲート電極Si層10と対向する電極としてのチャネルSi層30との間に所望の電圧を印加した際に、少なくともどちらか一方の電極物質でキャリアが存在しうるエネルギー範囲に存在する両電極物質の全エネルギーバンドについて、少なくとも片方の電極の該当エネルギーバンドの一部に関して、対向して配置した面の面方向の運動量の一致するエネルギーバンドがもう一方の電極の同一エネルギーのエネルギーバンドに存在しないように接合面及び接合面に垂直な軸に関する相対的回転角度を選択することで、電極間のキャリアの透過を抑制する。本発明のキャパシタ構造では、面方向の運動量が一致しないエネルギーバンドが存在するため、このエネルギーバンドが関与するキャリアの透過による電流を抑制することができる。

(もっと読む)

金属膜およびその製造方法、誘電体キャパシタおよびその製造方法ならびに半導体装置

【課題】 誘電体キャパシタを構成する電極として好適に用いることができる新規な金属薄膜およびその製造方法を提供する。

【解決手段】 本発明の金属薄膜は、

所与の基体の上方に設けられた面心立方型結晶構造を有する金属の薄膜であって、

前記薄膜は、(111)面が優先配向し、かつ、その表面には、前記基体の表面と平行ではない(100)面が表出している。また。本発明の金属薄膜において、前記面心立方型結晶構造を有する金属は、Pt、IrおよびRuの群から選ばれる少なくとも1つを含むことができる。

(もっと読む)

電子回路および電子回路の製造方法

【課題】ESDダメージが低いESDパワーレベルで発生するFinFET集積回路において、ESDから回路デバイスを保護することができる電子回路を提供する。

【解決手段】電子回路400’は、静電放電現象から保護される少なくとも1つの電界効果トランジスタと、少なくとも1つの保護される電界効果トランジスタ400aとを含む。保護電界効果トランジスタ400bは、保護される電界効果トランジスタ400aの結晶方位とは異なった結晶方位を含む。

(もっと読む)

半導体装置

【課題】ESD保護素子としてMISトランジスタを備えた半導体装置において、MISトランジスタの面積の増大を招くことなく、MISトランジスタ内の動作均一性を高める。

【解決手段】半導体基板10に形成されたMISトランジスタを備えた半導体装置であって、MISトランジスタは、半導体基板10に形成されたドレイン拡散層15と、半導体基板10上にチャネル幅方向に沿って互いに間隔を空けて配置され、ドレイン拡散層15をチャネル幅方向に沿って互いに分割する複数の分割体14と、半導体基板10上に分割体14を覆うように形成され、ドレイン拡散層15のチャネル幅方向に応力を生じさせる応力膜17とを備えている。

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置

【課題】炭化珪素半導体装置の、半導体基板と酸化膜との界面近傍における界面準位密度を低減して、チャネル移動度を向上させることのできる炭化珪素半導体装置とその製造方法とを提供すること。

【解決手段】炭化珪素の半導体基板1の表面にシリコン酸化膜を主成分とする酸化物層を形成する工程を含む炭化珪素半導体装置の製造方法において、酸化物層の、炭化珪素エピタキシャル層2と対向しない一方の主表面をIII族元素を含有するガスに加熱雰囲気中で曝露して、酸化物層にIII族原子を含有させる。そして、酸化物層と半導体基板1との界面近傍に拡散させたIII族原子により界面準位を終端させ、炭化珪素半導体装置のチャネル移動度を向上させる。

(もっと読む)

半導体装置

【課題】(0001)面や(11−20)面よりも優れた(000−1)面の炭化珪素基板を用いた半導体装置において、ゲート酸化後の熱処理方法を最適化することにより、高耐圧で高チャネル移動度を有するSiC半導体装置を提供する。

【解決手段】(000−1)面の炭化珪素からなる半導体領域にゲート絶縁膜と、そのゲート絶縁膜上にゲート電極と、上記半導体領域に電極を有する半導体装置において、ゲート絶縁膜中に1E19/cm3から1E20/cm3の範囲の水素あるいは水酸基(OH)を含む。或いは、ゲート絶縁膜と半導体領域の界面に1E20/cm3から1E22/cm3の範囲の水素あるいは水酸基(OH)が存在する。

(もっと読む)

半導体装置

【課題】 半導体パッケージの封止樹脂から半導体チップに対して応力がかかっても、特性値のシフトが少ない半導体装置を提供する。

【解決手段】 半導体チップの一辺に対し垂直方向のチャネルを形成するMOSトランジスタと水平方向のチャネルを形成するMOSトランジスタを組み合わせることで、応力に起因する特性値変動を相殺し、特性値のシフトが少ない半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】複数のチップ領域の電気的特性を検査する工程を含む半導体装置の製造技術において、製造歩留まりを向上させる。

【解決手段】ウェハの主面に配列した複数のチップ領域の中から、基準チップ領域を選定し(工程101)、その後、複数のチップ領域に複数の半導体素子および配線を形成する工程102および工程103の際に、基準チップ領域における最上の配線である基準導体膜を、そのパターン形状が、他の複数のチップ領域における最上の配線のパターン形状と異なるようにして形成し、その後、基準チップ領域の位置を半導体基板上の基準アドレスとして特定し(工程104)、その基準アドレスをもとに他の複数のチップ領域にそれぞれアドレスを決め(工程105)、電気的特性を順に検査し(工程106)、複数のチップ領域を選別する(工程106)。

(もっと読む)

半導体装置および半導体集積回路装置

【課題】半導体集積回路装置の高集積化及び低コスト化を可能にする複数のトランジスタセルを含む半導体装置を提供することを第1の目的とし、高密度に集積化された小型の半導体集積回路装置を安価に提供する。

【解決手段】基板上に、それぞれ第1層、ベース層、及び、第2層を順に有し、前記第1層、及び、前記第2層の一方がコレクタ層であり、他方がエミッタ層であるトランジスタセルを複数含み、前記各トランジスタセルの前記第1層に接続される第1電極が、前記第1層に形成されたエッチング溝に形成された半導体装置において、前記エッチング溝は、その長手方向に沿った側面が順メサ面となっており、複数のトランジスタセル間の前記第1電極が、前記各順メサ面に交差するように設けられた、まとめ配線によって接続される半導体装置である。

(もっと読む)

半導体装置

【課題】MOSトランジスタを有する半導体装置であって、エリアパッド下のMOSトランジスタの特性変動を抑制することが可能な半導体装置を提供する。

【解決手段】MOSトランジスタとエリアパッドを有する半導体装置10であって、結晶方位面<110>を表面とするシリコンを材料とする半導体チップ11と、ソース領域、ゲート領域及びドレイン領域がシリコンの結晶方位<110>の方向に並び、半導体チップ11内に形成される複数のMOSトランジスタ12と、半導体チップ11上のエリアパッドとして2次元状に形成された複数の接合用電極パッド13と、複数の接合用電極パッド13それぞれの上に形成された接合用バンプ14とを備え、複数の接合用電極パッド13は、その中心点が結晶方位<110>の方向に対して斜めの方向に並ぶことを特徴とする。

(もっと読む)

MOSトランジスタ及びこれを用いたMOSトランジスタ回路

【課題】本発明は、応力が加わっても、出力変動を防止でき、高精度の特性を保つことができるMOSトランジスタ及びこれを用いたMOSトランジスタ回路を提供することを目的とする。

【解決手段】ゲートの両側にソースとドレインが平行に延在して配置された複数の同一形状のトランジスタセルM1〜Mn、N1〜Nnを有するMOSトランジスタTr1、Tr2、Tr3、Tr3a、Tr4、Tr4aであって、

前記複数の同一形状のトランジスタセルは、同一方向に配置された第1の組に属する複数のトランジスタセルM1、M3、M11、M13、Mn−1、N1、N3、N11、N13、Nn−1と、同一方向に配置された第2の組に属する複数のトランジスタセルM2、M4、M12、M14、Mn、N2、N4、N12、N14、Nnとを有し、

前記第1の組に属するトランジスタセルと、前記第2の組に属するトランジスタセルは同数であって、配置方向が異なる。

(もっと読む)

半導体装置

【課題】 シリコン基板同一チップ上の半導体素子各々の特性を改善、または特性を損なう事なく、効率よく微細化を行う。

【解決手段】 各素子毎に三つ以上の異なるシリコン面方位を適用させる事で、各素子に要求される、少なくとも面方位が影響する特性を最良なものに決定づける。

(もっと読む)

集積回路製造時に方向性を表示するための方法と装置

集積回路(10)は、集積回路の視覚的に識別できない特徴の方向性を表示するために集積回路の一部として形成される、視覚的に識別できるインジケーター(128、130、132、又は134)を含んでいる。  (もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]