Fターム[5F038CD07]の内容

半導体集積回路 (75,215) | 配電、布線 (8,653) | 用途 (3,949) | 信号線(交差、クロス) (1,645) | バスライン (136)

Fターム[5F038CD07]に分類される特許

1 - 20 / 136

相互接続構造体及びその形成方法

【課題】 相互接続ラインを形成するための新規な方法を提供する。

【解決手段】 細線相互接続部(60)は基体(10)の表面内又はその上に形成された半導体回路(42)の上に位置する第1の誘電体層(12)内に設けられる。パシベーション層(18)は誘電体層の上に付着され、第2の厚い誘電体層(20)はパシベーション層の表面上に形成される。厚くて幅広い相互接続ラインは第2の厚い誘電体層内に形成される。第1の誘電体層はまた、基体の表面上に付着されたパシベーション層の表面上に幅広くて厚い相互接続ネットワークを形成するように、省略することができる。

(もっと読む)

半導体装置、システム装置、及び信号制御方法

【課題】処理装置の入出力パッドの端子数を低減することができる半導体装置を提供する。

【解決手段】処理装置21のバス制御回路34に含まれる入出力回路は、外部I/F22と接続されるパッドに接続される。入力部は、パッドから入力される信号に応じた入力信号を出力する。この入力信号は、処理回路31に供給される。パッドは、入力部の入力端子に接続され、出力端子は電源電圧VDDを伝達する電源配線に接続されている。入力部は、外部I/F22のバス制御回路44から入力されるHレベルの信号の電圧を出力端子から出力する。従って、電源配線には、外部I/F22から入力されるHレベルの信号による電圧が供給される。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

半導体装置

【課題】複数の半導体チップが積層された構造を有する半導体装置において、パンプ電極BP_0に接触せずに、かつ、貫通電極TSV_0の負荷容量を増やさずにテストできる半導体装置10を提供する。

【解決手段】積層された複数の半導体チップ21〜24のそれぞれが、バンプ電極BP_0と、テストパッドPAD_0と、テストパッドから供給される信号を受け取りバンプ電極に供給するテストバッファTD_0と、テストバッファの活性状態と非活性状態とを制御する制御信号を供給するバッファ制御部BCとを含む。

(もっと読む)

半導体装置

【課題】周辺回路領域を整形された形状とすることによりチップ面積を縮小する。

【解決手段】Y方向に延在する複数のデータバスDBがピッチP1でX方向に配列されたメモリセル領域40と、対応する複数のデータバスDBにそれぞれ接続された複数のバッファ回路BCが設けられたバッファ領域61とを備える。バッファ領域61上においては、Y方向に延在する複数のデータバスDBがピッチP2でX方向に配列され、ピッチP2はピッチP1よりも小さい。本発明によれば、データバスDBの配列ピッチをバッファ領域上において縮小していることから、他の回路ブロックに割当可能な面積を十分に確保することが可能となる。これにより、当該回路ブロックの幅拡大や形状の変形が不要となることから、無駄な空きスペースが生じにくく、チップ面積を縮小することが可能となる。

(もっと読む)

半導体集積回路

【課題】回路モジュール毎に電力供給のオン/オフを切り換える電源制御機能を有する半導体集積回路であって、回路規模及び配線規模の増加を極力抑えながら、ある回路モジュールへの電力供給のオン/オフを切り換える際に発生するインラッシュ電流による影響を根本的に除去する。

【解決手段】電源制御機能を有する半導体集積回路1は、回路モジュール11,12,21,22と電源制御回路3とを含む。回路モジュール21,22への電力供給は、電源制御回路3の制御下でオン/オフ制御される。電源制御回路3は、1つの回路モジュールへの電力供給のオン/オフを切り換えるとき、他の回路モジュールに、当該他の回路モジュールの内部におけるデータ転送を停止させるように制御する。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラム

【課題】長さが均一で直線的な配線を配置することができる半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラムを提供すること。

【解決手段】半導体集積回路のレイアウト設計方法は、第1の配線ピッチで配線を行う高速配線処理と、第1の配線ピッチより狭い第2の配線ピッチで配線を行う通常配線処理と、を有する。高速配線処理は、所定の高速バス配線上の複数のネットを第1の配線ピッチで略平行、かつ、略等長となるように自動配線を行う。通常配線処理は、高速配線処理より前に実行されない。

(もっと読む)

電力の島を使用した集積回路での電力の管理

【課題】集積回路において、消費電力を効率的に利用することを目的とする。

【解決手段】システム及び方法は、電力の島を使用して集積回路の電力を管理する。集積回路は、消費電力が電力の島のそれぞれで独立して制御される複数の電力の島を有する。電力マネージャは、電力の島のうち1つの目的の電力レベルを決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を実行する。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

半導体装置及び半導体装置のテスト方法

【課題】 ウエハ内にテスト専用チップを設けることなく、一度に測定できるチップ数を増加させてテスト時間の短縮化を図る。

【解決手段】 複数の半導体チップ11が形成された半導体ウエハ10と、複数の半導体チップ11の各々に形成された複数のボンディングパッド12と、複数のボンディングパッド12の各々に設けられた双方向バッファ20と、複数の半導体チップ11の双方向バッファ20を共通に接続する共通バス21を有する半導体装置のテスト方法である。複数の半導体チップの中からベース半導体チップ13を予め選択し、ベース半導体チップ13のボンディングパッド12にプローブ針を接触させ、複数の半導体チップ11に対して共通バス21を介して信号を供給し、複数の半導体チップ11の電気的特性を測定する。

(もっと読む)

保護装置

【課題】 USBコネクタと被保護部品間の信号ラインに接続されるESD破壊の保護装置として、双方向pn接合ダイオードが用いられるが、従来の構造では製造工程が複雑、煩雑で保護装置の低コスト化や耐圧の汎用性に限界があった。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面に互いに離間する第1n+型不純物領域および第2n+型不純物領域を設け、これらの周囲に互いに離間する第1p+型不純物領域と第2p+型不純物領域を設け、第1n+型不純物領域とコンタクトし、入力端子に電気的に接続する第1電極と、第2n+型不純物領域にコンタクトし、接地端子に電気的に接続する第2電極とを設ける。第1n+型不純物領域および第2n+型不純物領域は140μm以上離間され、それぞれ角丸四角形状でp+型半導体基板の対角線に沿って配置される。

(もっと読む)

保護装置

【課題】 USBコネクタと被保護部品間の信号ラインに接続されるESD破壊の保護装置として、双方向pn接合ダイオードが用いられるが、従来の構造では製造工程が複雑、煩雑で保護装置の低コスト化や汎用性に限界があった。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面にpn接合を形成し、互いに離間する第1n+型不純物領域および第2n+型不純物領域を設け、第1n+型不純物領域とコンタクトする第1導電層と、第1導電層にコンタクトし入力端子に電気的に接続する第1電極と、第2n+型不純物領域にコンタクトする第2導電層と、第2導電層にコンタクトし接地端子に電気的に接続する第2電極とを設けて横型の双方向pn接合ダイオードによる保護装置を提供する。

(もっと読む)

保護装置

【課題】 USBコネクタと被保護部品間の信号ラインに接続されるESD破壊の保護装置として、双方向pn接合ダイオードが用いられるが、従来の構造では製造工程が複雑、煩雑で保護装置の低コスト化や耐圧の汎用性に限界があった。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面に互いに離間する第1n+型不純物領域および第2n+型不純物領域を設け、これらの直下にこれらの底面より小さい第1p++型不純物領域と第2p++型不純物領域を設け、第1n+型不純物領域とコンタクトし、入力端子に電気的に接続する第1電極と、第2n+型不純物領域にコンタクトし、接地端子に電気的に接続する第2電極とを設ける。第1n+型不純物領域および第2n+型不純物領域は140μm以上離間され、それぞれ角丸四角形状でp+型半導体基板の対角線に沿って配置される。

(もっと読む)

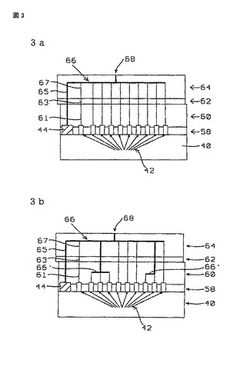

半導体装置、パターンレイアウト作成方法および露光マスク

【課題】 高集積化に有効な複数の配線パターンを含む配線パターン群を備えた半導体装置を提供すること。

【解決手段】 同一の配線用途のN(N≧3)本の配線パターンを含む配線パターン群を含む。N本の配線パターンの各々は別の層の配線郡内の配線パターンと電気的に接続するための接続領域を含む。N本の配線パターンは、配線パターンN1と、配線パターンN1の長手方向と異なる一方向に配置された二つ以上の配線パターンNi(i≧2)を含む。二つ以上の配線パターンNiはiの値が大きいほど配線パターンN1から離れた位置に配置され、二つ以上の配線パターンNiは少なくとも一つ以上のパターンNp(2≦p<N)と少なくとも一つ以上の配線パターンNq(p<q≦N)を含む。少なくとも一つ以上の配線パターンNpはpの値が大きいほど長手方向の寸法が長く、少なくとも一つ以上の配線パターンNqは、qの値が大きいほど、長手方向の寸法が短い。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】パッケージの端子数の増加と、ベースチップのI/O領域の増加を抑制する構造体を提供する。

【解決手段】複数の外部導出配線と、マスクROM領域、内部バス、複数のバス接続端子、および複数の外部接続端子を有する半導体集積回路基板と、この半導体集積回路基板上に積層され、複数のROM接続端子を持つプログラマブルROM15と、を備えた半導体集積回路装置において、複数の外部導出配線の一部、半導体集積回路基板、プログラマブルROM15、複数の外部接続端子と複数の外部導出配線との電気的接続、および複数のバス接続端子と複数のROM接続端子との電気的接続のそれぞれが同一半導体パッケージ内に封止されている。

(もっと読む)

半導体装置

【課題】従来と比較して低消費電力化を図ることが可能であると共に、外部制御装置の処理負荷の増大を回避可能な半導体装置を提供する。

【解決手段】複数の機能回路と、各機能回路による内部バスの使用を管理するバス管理回路とを備える半導体装置であって、前記バス管理回路は、各機能回路から通知されるデータ通信情報に基づいて各機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行する機能を有する。

(もっと読む)

集積回路及び集積回路の選別テスト方法

【課題】従来では外部機器にテストデータを保持、管理するため、管理精度の確実性に対する問題や管理コストが増大する問題があった。

【解決手段】不揮発性記憶回路と、第1の回路と、を備える集積回路の選別テスト方法であって、少なくとも前記第1の回路に対して第1の条件でテストを行い、前記第1の条件でのテストの第1の結果を前記不揮発性記憶回路に書き込み、前記第1の結果に応じて、前記第1の回路に対して第2の条件でのテストを行い、前記第2の条件でのテストが行われた場合の第2の結果を前記不揮発性記憶回路に書き込み、前記第1の結果もしくは前記第2の結果から前記集積回路を複数のグレードにランク分けする集積回路の選別テスト方法。

(もっと読む)

半導体集積回路、半導体集積回路の構成変更方法

【課題】再構成可能デバイスの回路面積を縮小する。

【解決手段】 本発明による半導体集積回路は、複数の機能ブロック10と、複数の構成情報が格納された複数の構成情報メモリ11と、自身に入力される構成情報に応じたスイッチング動作によって、機能ブロック10間の接続を制御する複数のプログラマブルスイッチ12、13とを具備する。複数のプログラマブルスイッチ12、13は、複数の構成情報メモリ11のうち、共通の構成情報メモリ11内に格納された構成情報を利用する。

(もっと読む)

IC端子のための低オーバヘッド・メモリ設計

【課題】出力に安全検査データを設定でき、かつ出力ピンに電圧競合の問題点を有しなく、かつ出力ピンに安定な検査データを維持できる、集積回路のメモリを提供する。

【解決手段】この集積回路は、集積回路の外部からアクセスすることが可能な端子と、前記端子に結合されかつ前記集積回路の外部の信号源により前記端子に加えられる信号を前記端子にラッチするように動作することができる回路とを有する。

(もっと読む)

1 - 20 / 136

[ Back to top ]