Fターム[5F038DT07]の内容

Fターム[5F038DT07]に分類される特許

1 - 20 / 234

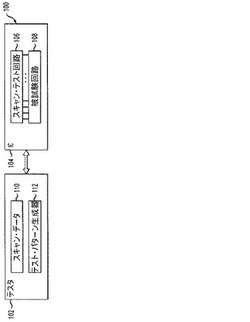

スキャン・チェーン用動的クロック領域バイパス

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

半導体テスト回路

【課題】スキャンチェーンを構成する回路でバーンイン試験を行う際に、シフトモードとキャプチャモードを切り替えるスキャンモードコントロール信号が接続された回路に対してもストレス印加を可能にする半導体テスト回路を提供する。

【解決手段】半導体テスト回路は、シフトモードとキャプチャモードを交互に切り替える内部スキャンモードコントロール信号と、スキャンチェーンのスキャンフリップフロップ回路に供給する内部クロック信号を生成するスキャンチェーン制御信号生成部を備える。スキャンチェーン制御信号生成部は、スキャンフリップフロップ回路の出力を遷移させる内部クロック信号のエッジのタイミングにおいて、内部スキャンモードコントロール信号がシフトモードになるように、内部スキャンモードコントロール信号と内部クロック信号の相互のタイミングを制御する。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

スキャンパタン作成手法、プログラム、スキャンパタン作成装置、テスタ、及びテスト方法

【課題】スキャンテストに要する時間を削減するテストパタン作成方法を提供する。

【解決手段】テストパタン作成方法は、組み合わせ論理回路と少なくとも一つのスキャンチェーンとに関する情報を、記録媒体から読み出し、少なくとも一つのスキャンチェーンの入力側に近いフリップフロップから順番に抽出し(ステップS21)、抽出したフリップフロップがスキャンキャプチャ動作によって組み合わせ論理回路から取り込むキャプチャデータと照合する期待値の必要性を判定し(ステップS22〜S25)、期待値が不要と判定されたフリップフロップが入力側から連続して存在するフリップフロップの数を取得し(ステップS27)、スキャンチェーンに含まれるフリップフロップの総数と、取得したフリップフロップの数との差分を、スキャンキャプチャ動作後のスキャンシフト回数として決定する(ステップS28)。

(もっと読む)

半導体装置

【課題】未使用端子がオープンのままである場合においても、未使用端子とその隣に位置する端子が短絡したことを検出できるようにする。

【解決手段】抵抗素子62は、一端が端子200に接続している。電圧選択部64は、抵抗素子62の他端を電源及び接地の一方に選択的に接続させる。電圧測定回路70は、抵抗素子62の一端(すなわち端子200と接続する側の端部)の電圧を測定する。端子制御回路20は、スイッチ素子66のオン/オフを制御する。接続制御回路30は、電圧選択部64を制御する。

(もっと読む)

半導体集積回路装置

【課題】部品点数を増加させることなく、低コストでかつ効率的に半導体集積回路装置の高信頼性化を実現させる。

【解決手段】ユーザプログラムの実行時において、周期タイマ2からタイマカウンタ信号が出力されると、CPUコア6,7はASEメモリ3に格納されたテスト用プログラムを実行し、そのチェック結果をトレースメモリ11に格納する。デバッグ回路10は、トレースメモリ11に格納されたチェック結果のコンペア処理を行い、CPUコア6,7が正常か否かを判定する。正常の場合、CPUコア6,7は、再びユーザプログラムを実行する。異常の場合、デバッグ回路10は、状態信号をシステム停止回路12に出力する。この状態信号を受けると、システム停止回路12は、動作制御信号をCPUコア6,7にそれぞれ出力し、半導体集積回路装置1の再起動処理が行われる。

(もっと読む)

ヒューズ回路及びトリミング良否判定方法

【課題】ヒューズ開口部の端部に必ず切断すべきヒューズを配設することにより、レーザー照射後のその切断/未切断をもって、端部のポリイミド膜の膜厚の良否を容易に判定する。

【解決手段】ヒューズ回路は、ヒューズ開口部FAの、ポリイミド膜の厚さが不本意に厚く残りやすい端部に配設された2つの切断確認用ヒューズ1a,1bと、ポリイミド膜の厚さ変動が端部に比べ少ない領域RAに配設された複数の実使用ヒューズ7a〜7dと、2つの切断確認用ヒューズ1a,1bからの信号を入力して当該ヒューズ1a,1bが確実に切断されているかを判定するヒューズ未切断判定回路2と、を備えている。なお、ヒューズ未切断判定回路2は、更にテストモード信号を入力すると共に、出力回路(例えばDQ回路)に判定結果を出力している。

(もっと読む)

半導体装置及びその評価方法

【課題】大規模な被測定素子の測定を短時間で行うことができ、且つ、高抵抗状態の短絡不良が発生した場合でも、不良の発生箇所を容易に特定することができるようにする。

【解決手段】直列接続された第1の被評価パターン101、及び該第1の評価パターンと隣接して配置された第2の被評価パターン102と、第2の被評価パターンとそれぞれ電気的に接続可能に設けられたノード情報伝達回路105とを備えている。第1の被評価パターンと第2の被評価パターンとは、互いに対向する領域により被測定素子103が構成されている。複数の第1の被評価パターンには、外部から所定の電圧が印加され、第2の被評価パターンとノード情報伝達回路とが電気的に接続されることにより、被測定素子の評価結果である第2の被評価パターンの電位がノード情報伝達回路に入力される。ノード情報伝達回路は入力された第2の被評価パターンの電位を外部へ順次出力する。

(もっと読む)

半導体集積回路および半導体集積回路のテスト方法

【課題】小さな回路規模で複数のパラレルシリアル変換回路を確実にテストすることが可能な半導体集積回路等を提供する。

【解決手段】第1および第2のパラレルシリアル変換回路と、第1および第2のテスト用パラレルデータ列を生成するテスト用パラレルデータ列生成回路と、第1および第2のパラレルシリアル変換回路が変換した第1および第2のシリアルデータビットの一致/不一致を検出する検出回路とを備えた半導体集積回路において、テスト用のパラレルデータ列生成回路が共通のテスト用パラレルデータ列を構成するそれぞれのパラレルデータのビットを第1のビット数だけシフトして第2のテスト用パラレルデータ列を生成するパラレルビットシフト回路を含み、検出回路が第1のシリアルデータと第2のシリアルデータとの一方のビットをシフトして比較回路に入力されるタイミングをそろえるシリアルビットシフト回路とを含む。

(もっと読む)

半導体装置

【課題】スキャンテストを可能にしながら内部データの漏洩及び改竄を防止する半導体装置を提供する。

【解決手段】複数のフリップフロップを有するユーザー回路と、テストモード時に、前記複数のフリップフロップを接続してスキャンチェーンを構成する接続経路とを有し、前記接続経路は、前記複数のフリップフロップのうちいずれかの前記フリップフロップの非反転出力値を論理演算して出力する論理演算回路、または、前記複数のフリップフロップのうちいずれかの前記フリップフロップの反転出力値を後段のフリップフロップに出力する反転値接続経路を有する。

(もっと読む)

半導体集積回路装置のテスト方法およびテストボード

【課題】半導体集積回路装置の入力端子数よりも少ない端子数のテスタを用いて半導体集積回路装置のテストを行うテスト方法を提供すること。

【解決手段】半導体集積回路装置のテスト方法は、半導体集積回路装置の複数の入力端子とテスタからのテスト信号を受信するテスタ端子とを、多対1に電気的に接続するテストボードを介して、該テスタから該半導体集積回路装置に所定のテストパタン信号を送信する工程と、前記半導体集積回路装置の出力端子から出力された出力信号と、前記所定のテストパタン信号に対応する期待値とを比較して、前記半導体集積回路装置の良否を判定する工程と、を含む。

(もっと読む)

半導体チップのクラックのチェックテスト構造を有する半導体装置

【課題】半導体チップ積層後に、チップごとにクラックの有無検出可能な半導体装置の提供。

【解決手段】積層半導体装置において、半導体チップ21〜24は、基板10とこの表裏面の対向する位置に形成した対のテスト端子と配線61を備える。これらは、一対の(表側)第1のテスト端子621h、(裏側)第1のテスト端子621t及び複数対の(表側)第2のテスト端子622〜625h、(裏側)第2のテスト端子622〜625tで、貫通電極TSVT1が(表側)第1のテスト端子と(裏側)第1のテスト端子を接続し、貫通電極TSVT2〜5が対の(表側)第2のテスト端子と(裏側)第2のテスト端子同士を接続し、配線は、一端が第1のテスト端子と、他端が第2のテスト端子の一つに接続され、基板の外周に沿って延びる。また異なる半導体チップの上下に隣接する第2のテスト端子同士も接続する。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】ジッタ耐性検査における検査コストの低減を図りつつ、入力される主信号の特性劣化を抑制できる半導体集積回路を提供する。

【解決手段】半導体集積回路101は、主信号にジッタ信号が付加されてなる検査信号を生成する機能を有し、ジッタ信号の基となる信号を生成するジッタ信号生成部50と、電源線Vccと接地線GNDとの間に介在し、電源線Vccからの電力供給を受けて外部からの主信号を増幅して出力するバッファ回路10と、電源線Vccとバッファ回路10との間およびバッファ回路10と接地線GNDとの間に介在し電源線Vccからバッファ回路10への供給電力をジッタ信号の基となる信号の大きさに基づいて変化させることにより主信号にジッタ信号を付加するジッタ信号付加部30とを備える。

(もっと読む)

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

集積回路テスト用の低電力で面積効率の良いスキャンセル

【課題】電力消費および面積要件の低減がもたらされる、スキャンテスト回路を有する集積回路を提供すること。

【解決手段】集積回路は、スキャンテスト回路と、スキャンテスト回路を使用してテストを受ける追加回路とを備える。スキャンテスト回路は、複数のスキャンセルを有する少なくとも1つのスキャンチェーンを備え、スキャンチェーンは、スキャンシフト動作モードではシリアル・シフトレジスタとして動作し、機能動作モードでは追加回路の少なくとも一部分からの機能データを捕捉するように構成される。スキャンチェーンのスキャンセルの少なくとも所与の1つは、スキャンシフト動作モードではスキャンセルの機能データ出力をディスエーブルし、機能動作モードではスキャンセルのスキャン出力をディスエーブルするように構成された出力制御回路を備える。

(もっと読む)

半導体集積回路、試験方法、情報処理装置、及びプログラム

【課題】テストパターンに対する出力応答に適用されるマスク情報の反転回数を削減すること。

【解決手段】半導体集積回路は、テストパターンが入力される複数のシフトレジスタと、前記テストパターンに応じた前記複数のシフトレジスタの出力応答に対するマスク情報として適用される擬似乱数を生成する生成部と、第一の制御信号の入力に応じ、該第一の制御信号が示す前記シフトレジスタに関して前記マスク情報を反転させる反転部と、前記擬似乱数の初期値を記憶する記憶部とを有し、前記生成部が生成する前記擬似乱数は、第二の制御信号の入力に応じて前記記憶部が記憶する前記初期値によって初期化される。

(もっと読む)

半導体集積回路、テスト方法、半導体集積回路の設計方法、半導体集積回路の設計支援プログラム

【課題】LogicBISTの解析TATを短縮する。

【解決手段】本発明による半導体集積回路は、複数のMISR回路M1、M2、M3と、複数のMISR回路M1、M2、M3に対応して接続される複数のスキャンチェーン群F1、F2、F3を具備する。第1モードにおいて、複数のMISR回路M1、M2、M3は、複数のスキャンチェーン群F1、F2、F3からの出力信号を圧縮演算する1つのMISR回路として機能し、第2モードにおいて、複数のMISR回路M1、M2、M3のそれぞれは、複数のスキャンチェーン群F1、F2、F3のそれぞれの出力を個別に圧縮演算するMISR回路として機能する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】アプリケーション実行効率をよりよくすることができる半導体集積回路及びその制御方法を提供すること

【解決手段】本発明にかかる半導体集積回路は、スキャンチェーンを有するプロセッサと、プロセッサにアプリケーションを実行させるプロセッサ制御部と、プロセッサのスキャンテストを制御するスキャンテスト制御部と、を有する。そして、スキャンテスト制御部がスキャンテストを実行している際に、プロセッサ制御部からのスキャンテスト中断要求があった場合、スキャンテストを中断し、アプリケーションの実行後に、スキャンテストを再開させるものである。

(もっと読む)

半導体集積回路、設計装置および設計方法

【課題】低消費電力で精度の良いスキャンテストを提供する。

【解決手段】一つ以上のスキャンチェイン2で共通して設けられ、各セグメントを駆動するための複数のクロック信号を生成するクロックゲーティング回路3と、内部回路の故障の影響が一つのセグメント内で伝搬され、かつ次の故障に対応するケアビットが対応するセグメントに設定されるように、クロック信号を生成する際に利用する制御信号を生成する制御信号生成部73とを備える。前記クロックゲーティング回路は、前記制御信号に基づいて、前記内部回路の故障の影響をいずれかのセグメント内で伝搬させるべく該セグメントに前記クロック信号を供給し、かつ故障を顕在化させるためのケアビットを対応するセグメントに取り込むべく該セグメントに前記クロック信号を供給し、かつ、前記ケアビットの設定と前記故障の影響の取り出しに関与しないセグメントへの前記クロック信号の供給を停止する。

(もっと読む)

半導体集積回路のテスト回路及び半導体集積回路のテストの制御方法

【課題】実動作周波数を用いて半導体集積回路をテストする際のテスト時間を短縮すること。

【解決手段】複数のテスト項目を含むテストにおけるテスト項目ごとの成否の判定結果について、所定数を単位とする複数のデータ群に組分けし、当該データ群内に判定結果がエラーを示すデータが含まれる場合、当該データ群内の全てのデータを当該エラー値に置換し、置換されたデータ群内の各データをシリアル出力する差分吸収部を備える半導体集積回路のテスト回路。

(もっと読む)

1 - 20 / 234

[ Back to top ]