Fターム[5F038DT09]の内容

Fターム[5F038DT09]に分類される特許

1 - 20 / 132

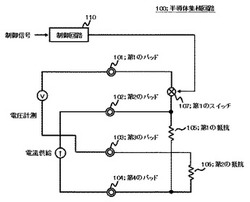

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体テスト回路

【課題】スキャンチェーンを構成する回路でバーンイン試験を行う際に、シフトモードとキャプチャモードを切り替えるスキャンモードコントロール信号が接続された回路に対してもストレス印加を可能にする半導体テスト回路を提供する。

【解決手段】半導体テスト回路は、シフトモードとキャプチャモードを交互に切り替える内部スキャンモードコントロール信号と、スキャンチェーンのスキャンフリップフロップ回路に供給する内部クロック信号を生成するスキャンチェーン制御信号生成部を備える。スキャンチェーン制御信号生成部は、スキャンフリップフロップ回路の出力を遷移させる内部クロック信号のエッジのタイミングにおいて、内部スキャンモードコントロール信号がシフトモードになるように、内部スキャンモードコントロール信号と内部クロック信号の相互のタイミングを制御する。

(もっと読む)

半導体装置

【課題】トリミング回路を備えた半導体装置において、内部電源の電圧レベルを半導体装置の外部から適切に制御できるようにすること。

【解決手段】半導体装置は、複数のレベルの間で遷移する第1のテストモード信号を受信し、第1のテストモード信号の遷移に応じてカウント動作を行うバイナリカウンタ回路と、バイナリカウンタ回路の所定のビットの値を示すビット信号、および、バイナリカウンタ回路のカウント動作を制御する第2のテストモード信号を受信し、ビット信号および第2のテストモード信号に応じて、第1のテストモード信号を遷移させるか否かを制御する制御回路と、バイナリカウンタ回路のカウント値に応じて、複数の基準電位の中からいずれかの基準電位を選択するセレクタと、セレクタにより選択された基準電位に応じて、内部電源を発生する内部電源発生回路と、を備える。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体装置および半導体装置の測定方法

【課題】半導体ウエハ上の半導体チップのアナログ特性の測定を精度良く行えるようにする。

【解決手段】半導体チップ1の被測定部3は半導体素子3a、回路3bである。被測定部3のアナログ特性を測定する測定回路4を設けている。測定回路4は、外部電源からプローブ針Pa、Pbを介して給電され、内部で測定用印加電圧を生成し、配線パターン5を介して被測定部3に印加する。測定回路4は、被測定部3の出力を配線パターン5から入力し、デジタルデータに変換する。測定回路4と配線パターン7を介して半導体チップ2の不揮発性メモリ6に接続され、デジタルデータが転送記憶される。一連の測定が終了した後に、不揮発性メモリ6からデジタルデータを取り出す。プローブ針の接触抵抗や浮遊容量の影響を低減して精度良いアナログ特性の測定ができる。

(もっと読む)

半導体集積回路及びBGAパッケージ

【課題】実使用時におけるクロストークの発生の抑制と、実使用時以外における信号用端子の確保とを半田ボールを増加させずに実現することが可能な半導体集積回路及びBGAパッケージが提供される。

【解決手段】半導体集積回路10が提供される。バッファ15は、マクロ11に接続される信号入力端子15aと、パッド21に接続される信号出力端子15bとを備える。バッファ15は、マクロ11が出力するバッファ制御信号41に基づいて、信号入力端子15aに入力される信号を信号出力端子15bから出力する動作状態と信号入力端子15aに入力される信号を信号出力端子15bから出力しない非動作状態とが切り替わる。バッファ16は、バッファ制御信号41に基づいて、パッド22とマクロ12とを接続するマクロ接続状態とパッド22とグラウンド電位14とを接続するグラウンド電位接続状態とが切り替わる。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

半導体装置

【課題】LSIチップの製造コストを低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板に形成され、第1の電源配線を含む第1の電源配線層を備える複数のLSI領域と、前記半導体基板に形成された第1の電源端子と、前記LSI領域の間のダイシングライン領域に、前記LSI領域と前記ダイシングライン領域とを区画するダイシングラインに沿って形成され、前記第1の電源配線と前記第1の電源端子とを電気的に接続する第2の電源配線を含む第2の電源配線層と、を備える。少なくとも前記LSI領域において、前記第1の電源配線と前記第2の電源配線との境界にバリアメタル膜が形成されている。

(もっと読む)

半導体装置

【課題】電源ノイズを一層効果的に解消する技術を提供する。

【解決手段】半導体装置1は、所定動作を実行するための内部回路6と、内部回路6に対して高電位電圧を供給するための電源ライン7と、内部回路6に対して低電位電圧を供給するためのグラウンドライン8と、ウェハテスト用電極パッド9と、ウェハテスト用電極パッド9を内部回路6に接続するための電気線10と、電気線10を内部回路6に対して非導通状態にすると共に、電気線10を電源ライン7とグラウンドライン8のうち何れか一方に対して選択的に導通状態とする接続切替部11と、を備える。

(もっと読む)

半導体集積回路およびその検査方法

【課題】半導体集積回路に内蔵されたアナログ/デジタル変換器をテストするためのテスト信号発生器として半導体集積回路に内蔵されたデジタル/アナログ変換器を使用する際に、デジタル/アナログ変換器が正常なデジタル/アナログ変換動作を実行可能であるか否か動作検証することを可能とすること。

【解決手段】半導体集積回路1は、アナログ/デジタル変換器(ADC)5とデジタル/アナログ変換器(DAC)6とを内蔵する。DAC6は、ADC5をテストするためのテスト信号生成器として使用可能とされる。半導体集積回路1は、DAC6の出力端子とADC5の入力端子の間に入力端子と出力端子とが接続されたバッファ増幅器7を更に具備する。バッファ増幅器7の出力端子とADC5の入力端子のいずれか一方は、半導体集積回路1の外部端子(T1、T2)として外部に導出される。

(もっと読む)

半導体装置

【課題】不良解析が容易な半導体装置を提供する。

【解決手段】実施形態によれば、待機状態と動作状態とを有する半導体装置が提供される。前記半導体装置は、機能素子部と、電荷供給部と、を備える。前記機能素子部は、前記動作状態において動作する第1機能素子を含む。前記電荷供給部は、前記第1機能素子に接続される。前記電荷供給部は、前記待機状態において第1制御信号が入力されたときに前記第1機能素子に電荷を供給する。

(もっと読む)

試験装置

【課題】プローブ検査においても、理想の電源環境を提供する。

【解決手段】試験装置は、ウエハ上に形成されたDUT1を試験する。電源補償回路20は、制御信号SCNT1、SCNT2に応じて制御されるソーススイッチSW1、シンクスイッチSW2を含み、それぞれがオンした状態において補償パルス電流ISRC、ISINKを生成し、補償パルス電流ISRCをメイン電源とは別経路からDUT1の電源端子P1に注入し、またはメイン電源からDUT1へ流れる電源電流から、補償パルス電流ISINKをDUT1とは別経路に引きこむ。電源補償回路20のうち、ソーススイッチSW1、シンクスイッチSW2を含む一部は、ウエハW上に形成される。ウエハには、ウエハ上に形成される電源補償回路20の一部に信号を印加するためのパッドP5〜P7が設けられる。

(もっと読む)

半導体装置

【課題】異なる電位に対応する複数の外部電源配線間に間隔部分を有する半導体装置に対して,所定電源ピン数のテスタにより短絡試験を行う場合において,より多くの半導体装置の短絡試験を同時に行うことができる半導体装置を提供する。

【解決手段】半導体装置は,コア回路と,該コア回路の周囲に配置され且つコア回路と外部装置間の信号を入出力する複数の入出力回路と,複数の入出力回路のうちの第一の入出力回路グループに第一の電位の電源を供給する第一の電源配線と,複数の入出力回路のうちの第二の入出力回路グループに第二の電位の電源を供給し且つ第一の電源配線と間隔をあけて直列に延びる第二の電源配線と,第三の電位の電源を供給する第三の電源配線とを備え,第三の電源配線から延びる配線パターンが,第一の電源配線と第二の電源配線間の間隔部分に設けられる。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、各前記回路ブロック毎に電源電圧を供給し、前記電源電圧を電圧調整回路により切り替える電圧供給回路を有し、前記電圧調整回路を切り替える電圧制御信号を記憶する電源電圧制御メモリを有する電圧設定回路を有し、前記半導体装置の回路の複数箇所に回路の電圧を検出する電圧検出スイッチを有し、前記電圧検出スイッチを指定することで電圧を検出する回路の位置を切り替え、且つ、前記電源電圧制御メモリにアドレスを指定して値を書き込む制御を行う回路スイッチ制御回路を有する半導体装置を用いる。

(もっと読む)

半導体装置の製造方法

【課題】前工程においてトランジスタごとに不純物の種類や量を変えることによる、製造コストや製造時間の増大を抑制する。

【解決手段】本発明による半導体装置の製造方法は、第1の閾値電圧及び第1のドレイン・ソース間電流を呈するようなデバイスパラメータをもって設計された第1のトランジスタを含む半導体回路を形成する半導体回路形成工程(ステップS11)と、第1のトランジスタにストレス電圧を印加して第1の閾値電圧とは異なる第2の閾値電圧及び前記第1のドレイン・ソース間電流とは異なる第2のドレイン・ソース間電流の少なくとも一方を第1のトランジスタが呈するようにする特性制御工程(ステップS14)と、第1のトランジスタが第2の閾値電圧及び第2のドレイン・ソース間電流の少なくとも一方を呈する状態で出荷する出荷工程(ステップS16)とを備える。

(もっと読む)

半導体集積回路

【課題】一部の回路領域の電源を遮断した時にその回路領域からの出力を固定化するアイソレータセルの回路規模の低減、動作の高速化および誤設定が発生の低減および修正可能なLSIの実現。

【解決手段】複数の回路領域12A,12B,12Cと、1つの回路領域へ電源供給するか否かを切り替える電源スイッチTrBと、電源スイッチの制御を行う電源制御回路13と、1つの回路領域から他の領域への出力が入力される複数のフリップフロップを有するクランプスキャンチェーンSFF21と、クランプスキャンチェーンのフリップフロップを所定の出力状態に設定するクランプデータ制御回路30,18,21,23と、を備える半導体集積回路。

(もっと読む)

電圧レギュレータを有する集積回路装置

【課題】集積回路装置のモード端子の数を低減する。

【解決手段】第1の電源端子VCCに接続され第1の電源電圧VDDEを供給する第1の電源配線11と,第1の電源電圧VDDEから第2の電源電圧VDDIを生成し第2の電源配線13に出力する電圧レギュレータ12と,電圧レギュレータの出力に接続され外部キャパシタが接続されるキャパシタ端子Cと,キャパシタ端子に印加される電圧に従い第1の状態と第2の状態とを判定する判定回路21とを有する。この判定回路は、キャパシタ端子Cに第3の電源電圧が印加されないで電圧レギュレータが動作する第1の動作モードと,キャパシタ端子Cに第3の電源電圧が印加されると共に電圧レギュレータが停止する第2の動作モードとを切り換えるので、モード端子数を削減することができる。

(もっと読む)

半導体装置およびその制御方法

【課題】電源遮断・復帰時に動作中の回路の誤動作を抑止しつつ、デバイスの製造ばらつきに応じて最適な速度での電源制御領域の電源遮断・復帰を可能とする半導体装置の制御技術を提供する。

【解決手段】半導体装置において、通常動作領域10と、電源制御領域20と、電源制御領域20に接続され、電源制御領域20への電源を供給または遮断する複数の電源スイッチSWとを有し、さらに、複数の電源スイッチSWのオンオフを制御し、半導体装置毎の製造後の性能に応じて電源遮断・復帰の遷移時間を変更し、電源遮断・復帰を行うスイッチ制御回路30を有する。さらに、半導体装置毎の製造後の性能を記録する記憶素子40を有する。

(もっと読む)

半導体装置、半導体ウエハおよびその電源制御方法

【課題】電源供給構造を備えた半導体装置において、外部測定装置のコストの増大を招くことなく、電源回路を正確に制御することが困難である。

【解決手段】本発明の半導体装置は、主回路部と、電源配線部と、無線信号を受信し制御信号を出力する無線回路部と、電源配線部と主回路部に接続され、無線回路部からの制御信号に基づき、主回路部への電源供給状態を制御する第一の電源回路部と、電源配線部と無線回路部に接続され、無線回路部への電源供給状態を制御する第二の電源回路部とを有する。

(もっと読む)

半導体集積回路及び半導体集積回路の電源スイッチ制御方法

【課題】電源スイッチを非導通状態から導通状態に遷移させる時間を最適化できる半導体集積回路及びその電源スイッチ制御方法を提供する。

【解決手段】共通電源配線と、第1の回路と、それぞれ電源スイッチ制御信号に基づいて導通、非導通が制御され共通電源配線と第1の回路との間を並列に接続する複数の電源スイッチと、電源スイッチ制御信号と複数の電源スイッチとの間に接続され電源スイッチ制御信号が非導通状態から導通状態に遷移するときに電源スイッチ制御信号の遷移をそれぞれ異なった遅延時間だけ遅延させて複数の電源スイッチに伝え複数の電源スイッチをそれぞれ時間をずらして非導通状態から導通状態に遷移させる遅延回路と、各遅延回路の遅延時間の増減を制御する遅延時間制御部と、を備える。

(もっと読む)

1 - 20 / 132

[ Back to top ]