Fターム[5F038DT17]の内容

Fターム[5F038DT17]に分類される特許

1 - 20 / 275

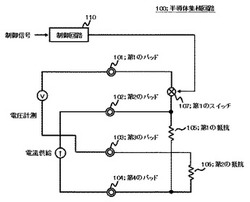

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

スキャン・チェーン用動的クロック領域バイパス

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

半導体装置および電源供給方法

【課題】消費電力を低減することが可能な半導体装置および電源供給方法を提供することである。

【解決手段】本発明にかかる半導体装置は、内部回路3に電源を供給する電源供給部4と、内部回路3の複数の場所における特性をモニタする複数のモニタ部1_1〜1_Nと、複数のモニタ部1_1〜1_Nから出力された信号C_1〜C_Nに基づき算出されたモニタ値C_AVEと、設定された比較値COMPとの比較結果に応じて電源供給部4を制御する制御部2と、を備える。制御部2は、複数のモニタ部1_1〜1_Nにおける特性のばらつきに応じて比較値COMPを設定する。

(もっと読む)

半導体装置

【課題】寿命が長い半導体装置を提供する。

【解決手段】このLSIは、2つのCPU1,2と、CPU1,2のうちのいずれか1つのCPUを示す論理レベルのデータ信号が書き込まれた記憶回路4と、リセット信号REが非活性化レベルにされてLSIのリセットが解除された場合、記憶回路4の記憶データの論理レベルに対応するCPUのみに電源電圧を供給するとともに、記憶回路4の記憶データを現在の論理レベルと異なる論理レベルのデータ信号に書き換える制御回路3,5とを備える。したがって、故障の検知や、厳密なタイミング制御を必要とせずに、CPUの長寿命化を図ることができる。

(もっと読む)

集積回路および集積回路の制御方法

【課題】タイミングエラーの種類を判別することができる集積回路を提供する。

【解決手段】エラー測定部は、同期動作回路に入力されているデータ信号が第1の期間内に変化した場合には同期動作回路における第1のタイミングエラーを検出する。また、エラー測定部は、第1の期間の前または後に所定の長さのエラー警告期間を加えた第2の期間内に前記データ信号が変化した場合には同期動作回路における第2のタイミングエラーを検出する。エラー補償制御部は、第1および第2のタイミングエラーがともに検出された場合には第1および第2のタイミングエラーの検出結果の履歴に基づいてタイミングの前後のいずれにおいて前記データ信号が変化したかを判断する。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

半導体回路及びテスト方法

【課題】スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する半導体回路及びテスト方法を提供する。

【解決手段】複数の被試験回路と、試験回路に対応して設けられた複数の第1のラッチ回路と、第2のラッチ回路と、パターンアドレスに対応して入力信号が規定されたテストパターンのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を第2のラッチ回路に出力する総合判定回路と、複数の第1のラッチ回路と第2のラッチ回路とを、第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

(もっと読む)

遅延スキャンテスト方法、半導体装置及び半導体装置の設計方法

【課題】従来のスキャンテスト方法では、電源電圧変動を抑制しながら動作クロックの周波数の高い半導体装置をテストできない問題があった。

【解決手段】本発明のスキャンテスト方法は、クロック信号SCLKをスキャンフリップフロップ21〜2nに入力して第1のテストパターンをスキャンフリップフロップ21〜2nに設定し、クロック信号SCLKよりも周波数の高いクロック信号RCLKをスキャンフリップフロップ21〜2nに入力すると共に、スキャンフリップフロップ21〜2nをクロック信号RCLKによらず保持する値を維持するホールドモードに制御し、ホールドモードを解除すると共にスキャンフリップフロップ21〜2nをテスト対象回路の出力に応じて保持する値を更新するテスト結果取得モードに制御し、テスト結果取得モードにおいてクロック信号RCLKを2パルス用いてスキャンフリップフロップ21〜2nに保持されている値を更新する。

(もっと読む)

半導体装置

【課題】未使用端子がオープンのままである場合においても、未使用端子とその隣に位置する端子が短絡したことを検出できるようにする。

【解決手段】抵抗素子62は、一端が端子200に接続している。電圧選択部64は、抵抗素子62の他端を電源及び接地の一方に選択的に接続させる。電圧測定回路70は、抵抗素子62の一端(すなわち端子200と接続する側の端部)の電圧を測定する。端子制御回路20は、スイッチ素子66のオン/オフを制御する。接続制御回路30は、電圧選択部64を制御する。

(もっと読む)

半導体集積回路装置

【課題】部品点数を増加させることなく、低コストでかつ効率的に半導体集積回路装置の高信頼性化を実現させる。

【解決手段】ユーザプログラムの実行時において、周期タイマ2からタイマカウンタ信号が出力されると、CPUコア6,7はASEメモリ3に格納されたテスト用プログラムを実行し、そのチェック結果をトレースメモリ11に格納する。デバッグ回路10は、トレースメモリ11に格納されたチェック結果のコンペア処理を行い、CPUコア6,7が正常か否かを判定する。正常の場合、CPUコア6,7は、再びユーザプログラムを実行する。異常の場合、デバッグ回路10は、状態信号をシステム停止回路12に出力する。この状態信号を受けると、システム停止回路12は、動作制御信号をCPUコア6,7にそれぞれ出力し、半導体集積回路装置1の再起動処理が行われる。

(もっと読む)

半導体集積回路装置の試験方法及び半導体集積回路装置

【課題】 半導体集積回路装置の試験方法及び半導体集積回路装置に関し、所定の回路動作を行った状態のまま半導体集積回路装置側の操作で所望の温度に制御する。

【解決手段】 スクリーニング試験前の工程にて測定された半導体集積回路装置の回路毎の電源電流値或いは電流ランクのいずれかにより、前記半導体集積回路装置全体毎または個別の回路動作毎に、適切な周波数に周波数設定し、所望の発熱量になるよう発熱量の制御を行い、スクリーニング試験時に、所定の回路動作を行った状態のまま所望の温度に制御する。

(もっと読む)

半導体装置及びその評価方法

【課題】大規模な被測定素子の測定を短時間で行うことができ、且つ、高抵抗状態の短絡不良が発生した場合でも、不良の発生箇所を容易に特定することができるようにする。

【解決手段】直列接続された第1の被評価パターン101、及び該第1の評価パターンと隣接して配置された第2の被評価パターン102と、第2の被評価パターンとそれぞれ電気的に接続可能に設けられたノード情報伝達回路105とを備えている。第1の被評価パターンと第2の被評価パターンとは、互いに対向する領域により被測定素子103が構成されている。複数の第1の被評価パターンには、外部から所定の電圧が印加され、第2の被評価パターンとノード情報伝達回路とが電気的に接続されることにより、被測定素子の評価結果である第2の被評価パターンの電位がノード情報伝達回路に入力される。ノード情報伝達回路は入力された第2の被評価パターンの電位を外部へ順次出力する。

(もっと読む)

半導体集積回路装置

【課題】 リングオシレータ回路を構成するインバータを切り替えることで変化する配線抵抗や配線容量などの変動をリングオシレータ回路の出力信号から得られる周波数変動から除去し、半導体回路の内部に実装されているトランジスタのランダムばらつきを検出する半導体回路装置を提供する。

【解決手段】 入力された信号の論理レベルを反転させる複数の回路素子を直列に接続した発振回路と、発振回路の出力周波数をカウントする信号処理部と、第1の回路素子に電源電圧を印加する電源端子と接地端子との間において互いに並列に接続された、互いの特性を比較した場合においてばらつきを持つ複数のトランジスタと、複数のトランジスタのうち、選択制御部によってそれぞれの1つが順番に選択されるようにタイミング信号を制御する。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

半導体装置および半導体装置の測定方法

【課題】半導体ウエハ上の半導体チップのアナログ特性の測定を精度良く行えるようにする。

【解決手段】半導体チップ1の被測定部3は半導体素子3a、回路3bである。被測定部3のアナログ特性を測定する測定回路4を設けている。測定回路4は、外部電源からプローブ針Pa、Pbを介して給電され、内部で測定用印加電圧を生成し、配線パターン5を介して被測定部3に印加する。測定回路4は、被測定部3の出力を配線パターン5から入力し、デジタルデータに変換する。測定回路4と配線パターン7を介して半導体チップ2の不揮発性メモリ6に接続され、デジタルデータが転送記憶される。一連の測定が終了した後に、不揮発性メモリ6からデジタルデータを取り出す。プローブ針の接触抵抗や浮遊容量の影響を低減して精度良いアナログ特性の測定ができる。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

半導体集積回路装置

【課題】 集積回路における時間的に変動するばらつきを検出する回路を提供する。

【解決手段】 集積回路内に検出回路100、演算回路101、ばらつき/電圧変換回路113とを設ける。検出回路100において集積回路の特性ばらつきを検出回路100の出力信号の発振周波数として検出する。演算回路101では、タイマ106にて規定した時間間隔毎に検出したばらつき情報をレジスタ111に格納し、統計演算回路112にて統計処理を施し、集積回路の時間的に変動する特性ばらつきを検出する。更に、ばらつき/電圧変換回路113は、検出された特性ばらつきに対応した電圧情報に変換する。

(もっと読む)

半導体集積回路、試験方法、情報処理装置、及びプログラム

【課題】テストパターンに対する出力応答に適用されるマスク情報の反転回数を削減すること。

【解決手段】半導体集積回路は、テストパターンが入力される複数のシフトレジスタと、前記テストパターンに応じた前記複数のシフトレジスタの出力応答に対するマスク情報として適用される擬似乱数を生成する生成部と、第一の制御信号の入力に応じ、該第一の制御信号が示す前記シフトレジスタに関して前記マスク情報を反転させる反転部と、前記擬似乱数の初期値を記憶する記憶部とを有し、前記生成部が生成する前記擬似乱数は、第二の制御信号の入力に応じて前記記憶部が記憶する前記初期値によって初期化される。

(もっと読む)

1 - 20 / 275

[ Back to top ]