Fターム[5F038EZ03]の内容

Fターム[5F038EZ03]に分類される特許

1 - 20 / 129

半導体装置

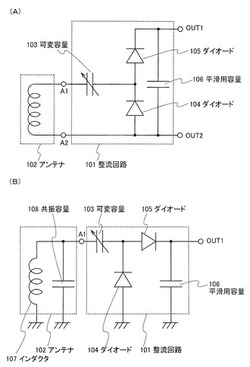

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

硬化性組成物および該組成物を用いた絶縁膜

【課題】本発明の目的は、特定の構造を有するポリシロキサン化合物を含有する高誘電率でありかつ絶縁性に優れた薄膜となる硬化性組成物に関するものである。本発明の硬化性組成物を硬化して得られる薄膜は、特に薄膜トランジスタのゲート絶縁膜やコンデンサ用材料として有用である。

【解決手段】アルケニル基を有する化合物(A)および特定の構造を有するポリシロキサン化合物(B)からなるヒドロシリル化反応性を有する硬化性組成物であり、得られる硬化物における1kHzでの比誘電率が3.5以上であることを特徴とする硬化性組成物により達成できる。

(もっと読む)

半導体装置とその動作方法

【課題】半導体装置において、消費電力を低減する。また、スタンバイ回路を少ない素子で構成し、半導体装置の回路面積の増大を防ぐ。

【解決手段】半導体装置に備えるスタンバイ回路をトランジスタ一つのみで構成し、該トランジスタに供給する電圧を切り替えることで、半導体装置の出力電流を制御する。これにより、スタンバイ状態での半導体装置の出力電流をほぼゼロにすることができるため、消費電力の低減が可能になる。なお、トランジスタの半導体層に酸化物半導体を用いることで、リーク電流を極小に抑えることができる。

(もっと読む)

半導体装置

【課題】コイル状のアンテナ部の内部に、占有面積が大きい導電層が設けられていると、電源を安定して供給することが困難になっていた。

【解決手段】記憶回路部とコイル状のアンテナ部とを積層して配置することにより、記憶回路部が含む占有面積の大きい導電層に電流が流れてしまうことを防止することができ、省電力化を図ることができる。また、記憶回路部とコイル状のアンテナ部とを積層して配置することにより、スペースを有効に利用することができる。従って、半導体装置の小型化を実現することができる。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

静電容量素子

【課題】 生産性に優れる温度補償型の静電容量素子を提供する。

【解決手段】 静電容量素子10は、基板20と、該基板20の上に位置する第1コンデンサ30と、基板20の上に位置し且つ第1コンデンサ30と電気的に並列接続されている第2コンデンサ40とを有する。第1コンデンサ30は、第1下部電極31と、第1誘電体32と、第1上部電極33とで構成される。第2コンデンサ40は、第1下部電極31と組成の異なる第2下部電極41と、第1誘電体32と同組成である第2誘電体42と、第2上部電極43とで構成される。第1コンデンサ30の温度が上昇する際に変化する静電容量と、第2コンデンサ40の温度が上昇する際に変化する静電容量とで正負が異なっている。

(もっと読む)

半導体装置

【課題】第1の半導体集積回路と第2の半導体集積回路とをフリップチップ工法で1つの基板上に搭載して半導体装置とする場合に、第1の半導体集積回路のパッド列を複数段としながら、第1の半導体集積回路から第2の半導体集積回路への配線をビアを介さずに行い得るようにする。

【解決手段】第1の半導体集積回路32と第2の半導体集積回路33とが基板31上に配置される。前記第1の半導体集積回路32には、その辺方向に延びる外側パッド列34Rが備えられる。また、前記第1の半導体集積回路32の外側パッド列34Rの内方には、前記外側パッド列34Rと並行に延びる内側パッド列35が備えられる。前記外側パッド列34Rのうち、前記内側パッド列35に対向する部分のパッド列34Raは、前記基板31に配置された金属配線36により、前記第2の半導体集積回路33の各パッド33aに電気的に接続される。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

半導体装置およびそれを用いた発光装置

【課題】 層間絶縁膜を挟んでゲート電極と容量電極が対向してできる容量の占有面積を小さくする。

【解決手段】 チャネル領域上の層間絶縁膜が周囲よりも膜厚が薄く、その部分で容量電極がゲート電極と対向して容量を形成している半導体装置。

(もっと読む)

システムインパッケージおよびソケット

【課題】サイズやコストを増大させることなく、テスト容易なシステムインパッケージを実現するとともに、そのシステムインパッケージをテストボードとして活用する。

【解決手段】テスト容易化回路内装SIP1cは、少なくともその1つに集積回路チップが搭載された複数のコア基板を、絶縁樹脂層を介して貼り合わせて構成するとともに、コア基板に形成された配線層を、スルーホールを介して接続して構成される。そのコア基板の1つであるテスト容易化回路内装基板10cには、テスト対象の集積回路であるDUT121を装着するソケット122が搭載されており、また、そのソケット122内に設けられたポゴピン1220には、インピーダンス整合用のチップ抵抗1224、インダクタ1225などの受動素子が設けられている。

(もっと読む)

半導体装置

【課題】電源配線と接地配線とを有する半導体装置において、配線の一部における電圧ドロップや、電圧ドロップに伴うマイグレーションの発生を抑制することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面に沿うように層状に広がる電源シート状配線PPWRと、主表面に沿うように、主表面に交差する方向に関して電源シート状配線と一定の距離を隔てて層状に広がる接地シート状配線PGNDと、上記主表面上に形成され、主表面内の一の方向に延在する電源配線PWRと、主表面上に形成され、一の方向に沿う方向に延在し、電源配線PPWRと一定の距離を隔てて形成された接地配線GNDとを備える。上記電源シート状配線PPWRは、電源配線PWRと電気的に接続されており、接地シート状配線PGNDは、接地配線GNDと電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】積層される半導体基板同士が、貫通孔の内部に埋め込まれる導電体により、電気的に良好に接続される半導体装置を提供する。

【解決手段】第1半導体基板SCPは、主表面を有する基板SUBと、基板SUB内および基板SUB上に形成された半導体素子TRと、半導体素子TRに電気的に接続された配線MTLと、基板SUBの主表面であり、互いに対向する第1主面と第2主面とを貫通し、配線MTLに達する貫通孔の内部に形成された導電層TSVとを有する。第1半導体基板SCPと第2半導体基板SCPとが積層され、導電層TSVは第2半導体基板SCPの配線MTLと電気的に接続される。導電層TSVの第2主面では、貫通孔の端部の周囲には凹部DUMが形成され、凹部DUMの底壁面は基板SUBの内部に存在する。導電層TSVを構成する導電材料CUが凹部DUMの内部に充填される。

(もっと読む)

システムインパッケージ

【課題】サイズやコストを増大させることなく、テスト容易なシステムインパッケージを実現する。

【解決手段】テスト容易化回路内装SIP1bは、少なくともその1つに集積回路チップ2が搭載された複数のコア基板3,4b,5を、絶縁樹脂層7を介して貼り合わせて構成するとともに、コア基板3,5に形成された配線層31,51を、スルーホール6を介して接続して構成される。このうち、コア基板4bには、半導体層が形成されており、コア基板4bには、その半導体層を用いたトランジスタ素子が形成され、さらに、そのトランジスタ素子がコア基板4bに含まれる配線層の配線で接続されることによって、集積回路チップ2のテストを容易化するためのテスト容易化回路が形成されている。

(もっと読む)

半導体装置

【課題】簡素な構成で製造安定性に優れた容量素子を提供する。

【解決手段】半導体装置100は、下部電極102、SiCN膜107および上部電極113からなる容量素子を備えた装置である。半導体基板上の絶縁膜101中に溝が設けられ、溝中に下部電極102が埋設されている。下部電極102は、第一下部電極103と第二下部電極105の二つの領域を有し、これらが絶縁膜101によって分離されている。

(もっと読む)

電圧調整回路

【課題】トランジスタにおけるオフ電流を低減し、電圧調整回路における出力電圧の変換効率を向上させる。

【解決手段】ゲート、ソース、及びドレインを有し、ソース及びドレインの一方に第1の信号が入力され、ゲートにクロック信号である第2の信号が入力され、チャネル形成層として酸化物半導体層を有し、オフ電流が10aA/μm以下であるトランジスタと、第1の電極及び第2の電極を有し、第1の電極がトランジスタのソース及びドレインの他方に電気的に接続され、第2の電極に高電源電圧及び低電源電圧が交互に与えられる容量素子と、を有し、第1の信号の電圧を昇圧又は降圧し、昇圧又は降圧した電圧である第3の信号を出力信号としてトランジスタのソース及びドレインの他方を介して出力する構成とする。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】高性能なフレキシブル半導体装置を提供すること。

【解決手段】可撓性を有するフレキシブル半導体装置であって、絶縁膜と、かかる絶縁膜の下面に位置する金属箔をエッチングすることによって形成されたソース電極およびドレイン電極と、絶縁膜の上面の一部に形成された半導体層と、ソース電極およびドレイン電極のそれぞれと、前記半導体層とを電気的に接続する取出し電極パターンと、取出し電極パターンおよび半導体層を封止する封止樹脂層と、封止樹脂層の面のうちソース電極およびドレイン電極が形成された面とは反対側の面に形成されたゲート電極とを備えたフレキシブル半導体装置。

(もっと読む)

レドックスキャパシタ及びその作製方法

【課題】室温で使用可能なレドックスキャパシタ及びその作製方法を提供する。

【解決手段】レドックスキャパシタの電解質として、水素を含む非晶質半導体を用いる。水素を含む非晶質半導体の代表例としては、非晶質シリコン、非晶質シリコンゲルマニウム、または非晶質ゲルマニウム等の半導体元素を有する非晶質半導体がある。また、水素を含む非晶質半導体の他の例としては、水素を含む酸化物半導体があり、代表例としては、酸化亜鉛、酸化チタン、酸化ニッケル、酸化バナジウム、または酸化インジウム等の一元系酸化物半導体を有する非晶質半導体がある。または、水素を含む酸化物半導体の他の例としては多元系酸化物半導体があり、代表的にはInMO3(ZnO)m(m>0、MはGa、Fe、Ni、Mn及びCoから選ばれた一の金属元素または複数の金属元素)がある。

(もっと読む)

半導体装置および電源装置

【課題】マルチフェーズ方式を用いた電源装置の小型化を実現する。

【解決手段】例えば、共通制御ユニットCCTLUと、複数のPWN搭載型駆動ユニットPSIP[1]〜PSIP[6]と、複数のインダクタL[1]〜L[6]を備える。CCTLUは、各PSIP[1]〜PSIP[6]に対してそれぞれ位相が異なるクロック信号CLK[1]〜CLK[6]を出力する。この各CLK[1]〜CLK[6]は、それぞれ個別に電圧状態を制御可能となっており、例えば、CLK[2]をハイインピーダンス状態にするなどが可能となっている。この場合、PSIP[2]は、このハイインピーダンス状態を検出し、自身の動作を停止する。これによって、別途イネーブル信号等を用いずに、マルチフェーズのフェーズ数を任意に設定可能となる。

(もっと読む)

薄膜集積回路装置及びその製造方法

【課題】商品の意匠性を低下させないICタグ等を形成することができる薄膜集積回路装置を提供する。

【解決手段】透明基板1上に少なくともTFT素子Aと容量素子B及び/又は抵抗素子Cとを有し、TFT素子Aを構成するゲート電極2A、ゲート絶縁膜3A、半導体膜4、ソース電極6S及びドレイン電極6Dがいずれも透明膜であり、容量素子Cを構成する誘電体膜3Bが前記ゲート絶縁膜3Aと同一材料であり、その誘電体膜3Bを積層方向Zに挟む一方の第1電極2Bが前記ゲート電極2Aと同一材料で、他方の第2電極6Bが前記ソース電極6S及びドレイン電極6Dと同一材料であり、抵抗素子Cを構成する抵抗体膜4Cが前記半導体膜4と同一材料であり、その抵抗体膜4Cを面内方向Xに挟む第3電極6Eと第4電極6Fが前記ソース電極6S及びドレイン電極6Fと同一材料であるようにした薄膜集積回路装置10Aを提供する。

(もっと読む)

薄膜キャパシタ

【課題】バンプ等の外部接続端子に働く鉛直方向の応力が電極層に集中しない構造を有するとともに、等価直列抵抗を所望の値に増加させることが容易な薄膜キャパシタとその製造方法を提供する。

【解決手段】基板と、前記基板上に形成され少なくとも1層の誘電体薄膜と少なくとも2層の電極層からなるキャパシタ部と、前記キャパシタ部の少なくとも一部を覆う保護層と、前記キャパシタ部のいずれかの電極層と電気的に接続する引き出し導体と、前記引き出し導体上に形成されたバンプと、を備え、前記引き出し導体は、前記保護層に形成された開口部内に形成されて前記キャパシタ部のいずれかの電極層と電気的に接続する接続部と、前記保護層上に延伸された引き回し部とからなり、前記バンプは前記引き回し部上に形成されている。

(もっと読む)

1 - 20 / 129

[ Back to top ]