Fターム[5F038EZ06]の内容

Fターム[5F038EZ06]に分類される特許

741 - 754 / 754

混合信号についての基板クロストークを低減する技術及びRF回路設計

集積回路は、半導体基板の上に形成された埋込絶縁層と、当該埋込絶縁層の上に形成された半導体メサとを有する。低抵抗率のガード・リングは、半導体メサを実質的に囲み、そして半導体基板と接触している。低抵抗率のガード・リングは、接地され、そして半導体メサをRF信号から分離する。  (もっと読む)

(もっと読む)

ソース/バルク・ポンピングを使用してゲート酸化膜を保護するための方法および装置

ESD事象の間、ソース・ポンプまたはバルク・ポンプを使用してバルクおよび/またはソースの電位レベルを高くし、それにより回路をESD事象から保護する方法および装置である。この装置は、ESD事象に応答して、トランジスタの2つの端子と端子の間に形成される電圧を第2の端子の電位レベルを調整することによって制限する保護回路を備えている。

(もっと読む)

(もっと読む)

SOI型マスタースレーブ回路における位相ノイズ削減方法

【課題】マスター区分およびスレーブ区分を含む電子回路の位相ノイズを削減する。

【解決手段】位相ノイズに寄与するトランジスタ(60、61)のフローティングボディ(64、65)の電位が適切な接続を用いて設定される回路であり、マスター区分およびスレーブ区分がSOI型トランジスタを内含しており、最初に位相ノイズの軽減に関与するフローティングボディトランジスタが配置され、次にフローティングボディが、前記回路の全体的位相ノイズに対するその寄与を局所的に削減するべく適切な接続を用いて一つの電位に設定される。

(もっと読む)

静電放電保護デバイスを備えた集積回路チップ

集積回路チップは、順に、基板材料から成る基板層、絶縁体から成る絶縁層、第1の導電体から成る第1導電層、誘電体からなる誘電層及び第2の導電体から成る第2導電層を有し、集積回路チップが少なくとも1つの集積回路及び少なくとも1つの集積静電放電保護デバイスを有し、静電放電保護デバイスが間隔を設けられた一対の中心電極及び周辺電極を有し、中心電極が第1導電層によって形成され、周辺電極が第2導電層によって形成され、電極対がステロイド・スパークギャップ空洞によって分離されており、ステロイド・スパークギャップ空洞の環状部が集積回路チップの絶縁層によって形成されたベース層、周辺電極によって形成された側壁、集積回路チップの誘電層によって形成されたカバー層、及び中心電極によって形成され絶縁層に接触するコンタクトパッドを有する環状部の中心部を有し、静電放電保護デバイスがまた、静電放電から保護されるべき入力回路パスに中心電極を電気接続する手段、及び回路グラウンド又は回路電源の何れかへの接続を有する静電放電パスに前記周辺電極を電気接続する手段を有する。本発明はまた上記集積回路チップの製造方法に関する。  (もっと読む)

(もっと読む)

集積回路製造をモニタするためのテスト構造体またはライン・アレイを接続するための方法および構成

テスト・チップは、各領域が少なくとも1つのテスト構造体を含むことができる複数領域のアレイを有する少なくとも1つのレベルを具える。その少なくとも幾つかの領域はそれぞれのテスト構造体を含む。そのレベルは、テスト構造体に入力信号を供給する複数のドライバ・ラインを有する。そのレベルは、テスト構造体から出力信号を受信する複数の受信機ラインを有する。そのレベルは、電流を制御するための複数のデバイスを有する。各テスト構造体は、ドライバ・ラインの中の少なくとも1本のラインに、その間にあるそのデバイスの中の第1のデバイスで接続される。各テスト構造体は、受信機ラインの中の少なくとも1本のラインにその間にあるそのデバイスの中の第2のデバイスで接続されていて、そのテスト構造体の各々がドライバ・ラインおよび受信機ラインを用いてテストを行うべく個々にアドレス可能である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

底部電極(11)及び又はキャパシタ誘電体上に導電性平滑化層(16、19)を形成することにより、幾何学的に高くされた電場を低下させると共に、電極を平滑化することで、形成されるMIMキャパシタの信頼性を向上させることができる。一実施形態において、難溶性窒化物で形成された第1のキャッピング層(14)上には、難溶性金属又は難溶性金属リッチ窒化物を含む第1の層(16)が形成される。更に、キャパシタ誘電体上には、難溶性金属(18)又は難溶性金属リッチ窒化物を含む第2の層(19)が形成される。導電性平滑化層(16、19)は、例えば、ゲート電極とゲート誘電体との間のトランジスタ等の他の半導体装置にも使用される。  (もっと読む)

(もっと読む)

電気コンタクトを対向する両側に有する半導体素子及びその形成方法

半導体(10)はトランジスタのような能動素子を有し、この能動素子はキャパシタ(75,77,79)のような受動素子の直下に位置し、能動素子及び受動素子はビアまたは導電領域(52)及び配線(68,99)によって接続される。ビアまたは導電領域(52)はトランジスタの拡散領域またはソース領域(22)の底面にコンタクトし、更にキャパシタ電極の内の第1電極(75)にコンタクトする。横方向に位置する縦型ビア(32,54,68)及び配線(99)はキャパシタ電極の内の第2電極(79)にコンタクトする。金属配線または導電材料(68)は電源プレーンとして使用することができ、この電源プレーンは、電源プレーンをトランジスタに隣接させるのではなくトランジスタの下に位置するように用いることによって回路面積を節約するように作用する。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

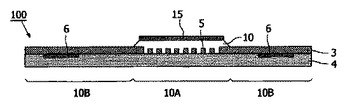

柔軟な半導体デバイス及び識別ラベル

集積回路(5)と、その集積回路(5)の相互接続構造に組み込まれ、又は直接結合されるアンテナ(6)とを備える柔軟なデバイス(100)が与えられる。相互接続構造は、アクティブ領域の外側に広がる。電気的に絶縁する又は誘電性のある層(4)がアンテナ(6)と集積回路(5)との両方に対する支持層として存在する。基板(10)は、集積回路(5)のアクティブ領域(10A)の外側の非シリコン領域(10B)で除去される。この除去は、単結晶シリコンの基板の使用に結び付けられることができる。柔軟なデバイスは、識別ラベル及びセキュリティペーパへの一体化にとても適しており、一時的に付けられたキャリア基板を用いて製造されることができる。  (もっと読む)

(もっと読む)

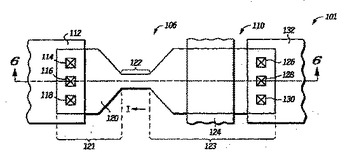

フューズ及びその形成方法

アクティブフューズはアクティブフューズ構造(120)を備え、この構造を使用して可変抵抗体(106)及び選択トランジスタ(110)の双方を形成する。一の実施形態では、アクティブフューズ構造は、半導体基板(140)の活性領域(160)の一部に形成され、選択ゲート(124)はアクティブフューズ構造の一方の端部(123)の上に配置されてアクティブフューズへの書き込みに使用する一体型選択トランジスタ(110)を形成する。共有型のアクティブフューズ構造を活性領域の内部に使用することによって、面積要件を縮小し、かつ検出マージンを大きくすることができる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】半導体素子の局所的な温度上昇を防止することが可能な半導体集積回路を提供する。

【解決手段】放熱セル2は、発熱セル1に対して隣接して配置され、電源電位配線3又は接地電位配線4と同じ第1配線層に放熱部材6及び放熱部材7を備え、さらに放熱部材6及び放熱部材7は、ビア9を介して第2配線層8に接続される。発熱セル1で発生した熱は、電源配線3、接地配線4に伝導し、放熱部材6及び放熱部材7で放熱される。また、放熱部材6及び放熱部材7からビア9を介して第2配線層8に熱が伝導することにより、更に放熱を促進し、発熱セル1が局部的に高温になることを防ぐ。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SOI層に形成された素子の誘電損失をより低減させることが可能な半導体装置およびその製造方法を提供することにある。

【解決手段】支持基板1の一部を除去して溝Gを形成する。溝Gは,支持基板1による誘電損失が想定される素子の直下に位置するように形成される。溝Gには,誘電体としてのシリコン結晶が薄くしか存在しないか,あるいは全く存在しないため,その上に位置する素子の誘電損失は極めて小さなものとなる。この素子が高周波回路の構成要素であるならば,この高周波回路は,高周波信号の処理に関して,高い応答性や安定性を発揮することになる。

(もっと読む)

D/A変換回路及び半導体装置

【課題】 高いビット数のデジタル信号に対応し、線形性が良く、占有面積の小さいD/A変換回路を提供する。

【解決手段】 複数の容量を有するD/A変換回路であって、複数の容量は、第1電極と、第1電極に接している第1誘電体と、第1誘電体に接している第2電極と、第2電極に接している第2誘電体と、第2誘電体に接している第3電極とをそれぞれ有しており、第2電極は、第1電極及び第3電極と重なっており、第2電極は、第1電極及び第3電極と重なっている部分において開口部を有しており、第2電極が有する開口部において、第1誘電体及び第2誘電体にコンタクトホールが形成されており、コンタクトホールを介して第1電極と第3電極が接続されていることを特徴とするD/A変換回路。

(もっと読む)

半導体装置

【課題】 アナログ・デジタル混載集積回路を形成した半導体装置において、クロストークの発生を防止する。

【解決手段】 N型シリコン基板101の表面にP型エピタキシャル薄膜102を形成する。このエピタキシャル薄膜102の領域103にはデジタル集積回路を、領域104にはアナログ集積回路領域を、それぞれ形成する。これらの領域103,104を、トレンチ構造の素子分離膜105で完全に分離することにより、ゲート電極107から導入されたノイズの大部分は、エピタキシャル薄膜102の領域103から基板101を介して領域104に伝搬し、N+ 拡散領域109に達する。ここで、N型シリコン基板101とP型エピタキシャル薄膜102との界面(すなわちPN接合面)には、空乏層が形成されるので、この界面付近の寄生容量C8 ,C9 は非常に小さくなり、このためノイズ伝搬経路全体の合成容量も小さくなる。したがって、ノイズの伝搬を抑え、クロストークの発生を抑制することができる。

(もっと読む)

741 - 754 / 754

[ Back to top ]