Fターム[5F038EZ16]の内容

Fターム[5F038EZ16]に分類される特許

321 - 340 / 340

半導体装置

【課題】 ゲート電極下の絶縁膜の実装時のストレスによるクラックの発生を防止できるようにした半導体装置及びその製造方法、半導体装置の設計方法を提供する。

【解決手段】 シリコン基板1に設けられたトランジスタと、このトランジスタを覆うようにシリコン基板1上に設けられた層間絶縁膜21と、層間絶縁膜21上にAlパッド31を介して設けられたバンプ電極41とを有し、バンプ電極41下方の領域のシリコン基板1には、トランジスタとしてゲート電極11の周縁部下のシリコン酸化膜が当該ゲート電極11の中央部下のシリコン酸化膜よりも厚いMOSトランジスタ10のみが設けられ、それ以外の領域のシリコン基板1には、トランジスタとしてゲート電極の中央部下からその周縁部下にかけてのシリコン酸化膜の厚さが均一なMOSトランジスタ70が設けられている。

(もっと読む)

半導体装置及びインバータ回路

【課題】しきい値制御可能なTFTを有する半導体装置及びインバータ回路を提供する。

【解決手段】本発明に係る半導体装置は、バックゲート電極と、前記バックゲート電極に、第1のゲート絶縁膜を介して接して設けられた半導体活性層と、前記半導体活性層に、第2のゲート絶縁膜を介して接して設けられたゲート電極と、を有する複数のTFTと、前記複数のTFTのしきい値を制御するしきい値制御回路と、を有し、前記バックゲート電極には、前記しきい値制御回路によって任意の電圧が印加されることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 キャパシタとMOSトランジスタとを同一半導体基板上に備えた半導体装置において、キャパシタの絶縁破壊を防止する。

【解決手段】 P型半導体基板1の全面に高耐圧MOSトランジスタのゲート絶縁膜となるSiO2膜11を形成する。高耐圧MOSトランジスタ形成領域R1及びキャパシタ形成領域R4に隣接したトレンチ絶縁膜7a,7bのエッジを覆うSiO2膜11aの部分上にホトレジスト層12を選択的に形成し、このホトレジスト層12をマスクとして、SiO2膜11をエッチングにより除去する。このエッチング時にホトレジスト層12がマスクとなるため、キャパシタに隣接するトレンチ絶縁膜7a,7bのエッジが過度にえぐられることがない。このエッチング時に残ったSiO2膜11aとその後に形成するSiO2膜とをキャパシタ絶縁膜とする。

(もっと読む)

ESD保護回路及びその製造方法

【課題】ラッチアップによる問題点を解決できるN−EDSCR素子を用いたESD保護回路及びその製造方法を提供すること。

【解決手段】半導体基板(110)と、半導体基板に形成された導電型ウェル(111)と、導電型ウェルと一部が重なるように形成された導電型ドリフト(117)と、導電型ウェル及び導電型ドリフト内に形成された第1導電型拡散層(113、114)と、導電型ウェル内で第1導電型拡散層から分離されて形成された第2導電型拡散層(115)、導電型ドリフト内で第1導電型拡散層に隣接して形成された第2導電型拡散層(116)と、第2導電型接続層(115)を覆うように形成された導電型ソース(122)と、導電型ソース及び導電型ドリフトの間の導電型ウェル上に形成された導電型電極(118)とを備える。

(もっと読む)

半導体素子及びその形成方法

【課題】MIMキャパシタを形成した後に金属配線を形成することにより無駄なマスク工程を省略し、キャパシタ形成時のエッチングでの金属配線の損傷を防止できる半導体素子及びその形成方法を提供すること。

【解決手段】層間絶縁膜100を貫通するコンタクトプラグ110を形成するステップと、層間絶縁膜100上にキャパシタを形成するための下部電極用導電層130、誘電層140、上部電極用導電層150を順次形成するステップと、上部電極用導電層150をパターニングして上部電極150を形成するステップと、誘電層140及び下部電極層130をパターニングして下部電極130を形成してキャパシタを形成するステップと、コンタクトプラグ110、キャパシタの上部電極150及び下部電極130に接続される第1金属配線120を形成するステップとを含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】半導体集積回路装置の高速化を図り、また、エレクトロマイグレーションやストレスマイグレーションの発生を抑え、配線寿命を長くする技術を提供する。

【解決手段】半導体基板1上に形成された酸化シリコン膜23および窒化シリコン膜22中の配線溝内を含む酸化シリコン膜23上にバリア層26aおよび銅膜26bを順次形成後、前記配線溝外部のバリア層26aおよび銅膜26bを除去することによって配線26を形成し、配線26上にタングステンを選択成長もしくは優先成長させることにより、配線26上にタングステン膜26cを形成する。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置の動作方法

【課題】容量変化率が大きく、かつ容量の制御がしやすい可変容量素子を提供する。

【解決手段】 半導体基板1に形成された第1導電型のウェルと、ウェル上に形成された絶縁膜3bと、絶縁膜3b上に形成された電極4bと、ウェルに接続する第1端子11cと、半導体基板1に形成され、第1電極4bの下方及びその周囲に位置する第2導電型不純物領域7bと、第2導電型不純物領域7bに接続する第2端子11bとを具備する。第1端子11cの下には第1導電型不純物領域が形成されており、第2端子11bの下には、高濃度第2導電型不純物領域が形成されている。

(もっと読む)

半導体装置

【課題】多層配線の層間絶縁膜として低誘電率絶縁膜を使用しても、配線と低誘電率絶縁膜との境界部分における応力集中を低減でき、絶縁膜の剥れを抑制でき、さらに放熱能力を向上した配線構造を具備した半導体装置を提供する。

【解決手段】上記の課題を解決した半導体装置は、半導体基板の上方に形成された絶縁膜ILDと、前記絶縁膜内に形成された配線Mと、前記低誘電率絶縁膜内に前記配線と離間して形成された網目状ダミー構造体NDとを具備する。

(もっと読む)

半導体装置

【課題】LDD構造のトランジスタ素子の特性に悪影響を与えることなく同一基板上に高抵抗体素子を形成する。

【解決手段】シリコン基板1にNウェル領域3、素子分離酸化膜5、ゲート酸化膜7、ポリサイドゲート電極9、低濃度拡散領域17,21を形成した後、シリコン基板1上全面にCVD酸化膜を形成し、さらにその上に抵抗値制御のための不純物としてBF2を導入した高抵抗体素子パターン25を形成し、CVD酸化膜のエッチバックを行なってサイドウォールスペーサ15a及びCVD酸化膜パターン15bを形成し、高抵抗体素子パターン25の両端側に低抵抗領域29を形成して抵抗体領域27を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 LOCOS酸化膜のバーズビークが短く、かつ半導体素子の抵抗値が低い半導体装置を提供する。

【解決手段】 LOCOS酸化膜により素子分離された半導体装置が、絶縁層と絶縁層上に設けられたシリコン層とを含むSOI基板と、シリコン層に形成された複数の半導体素子と、シリコン層の表面から絶縁層に達するように形成され、半導体素子の間を電気的に分離する素子分離領域とを含む。素子分離領域は、LOCOS酸化膜の積層構造よりなる。

(もっと読む)

混載型メモリ装置及びその製造方法

【課題】電気的特性に優れた、より高性能な混載型メモリ装置及びその製造方法。

【解決手段】混載型メモリ装置100は、強誘電体層44を含む複数のメモリセルがマトリクス状に設けられているメモリセルアレイ領域1、ロジック回路素子20が設けられているロジック回路領域2を含む複数の領域を有していて、メモリセルアレイ領域を除く領域を覆って設けられているライナー酸化膜80と、ライナー酸化膜が設けられている領域とメモリセルアレイ領域とにわたって設けられているカバー膜90とを具えている。

(もっと読む)

無線チップ

【課題】 無線チップは、アンテナ回路によって、その大きさが決まっていることが多く、無線チップに供給される電源電圧又は電力は、アンテナはサイズが大きいほうが確保しやすい。一方、無線チップの小型化への要望は強く、アンテナを小さくする必要がある。そこで本発明は、小型のアンテナであっても通信可能な無線チップ、つまり、通信可能距離を改善した小型の無線チップを実現することを課題とする。

【解決手段】 上記課題を鑑み本発明のIDチップが有する電源回路は、昇圧回路と整流回路を有する昇圧電源回路を用い、従来のIDチップ内部で生成される電源電圧よりも高い電源電圧を生成する。

(もっと読む)

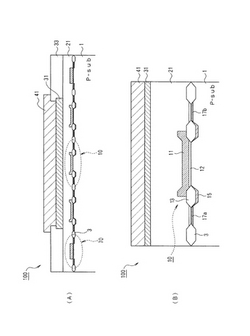

半導体デバイスにおける厚い酸化物領域およびその形成方法

【課題】半導体デバイス内に、低コストでデバイスの信頼性および性能を低下させることのない厚い酸化物領域などの酸化物領域を形成する新規な技法を提供すること。

【解決手段】半導体デバイス内に酸化物領域を形成する方法は、デバイスの半導体層内に互いに近接して複数のトレンチを形成する工程と、トレンチの少なくとも側壁および底壁上に絶縁層が形成されるように半導体層を酸化させる工程とを含む。トレンチは、酸化工程の結果形成された絶縁層がトレンチを実質的に充填し、対応する1対の隣接したトレンチ間の半導体層を実質的に消費するように構成される。このようにして、複数のトレンチ全体にわたって実質的に連続した酸化物領域が形成される。

(もっと読む)

薄膜コンデンサとその製造方法

【目的】 下部電極、高誘電体膜、上部電極それぞれにおける層間の密着性や他の層との間での高い密着性を有し、優れた高周波特性を有する薄膜コンデンサを実現することを目的とする。

【解決手段】 下部電極と、下部電極上に設けられた高誘電体膜と、高誘電体膜上に設けられた上部電極とを有する薄膜コンデンサにおいて、上部電極、高誘電体膜、及び下部電極の少なくとも1つに対して複数の開口部を設けるものとしているものである。特に、絶縁膜に覆われる上部電極に対して複数の開口部を設ける。

(もっと読む)

誘電体薄膜キャパシタの製造方法

【課題】キャパシタ部に悪影響を及ぼすこともなく誘電体薄膜キャパシタを高効率で製造することができ、かつキャパシタ部から分離された基板材料を容易に再利用することができるようにする。

【解決手段】キャパシタ部11及び第1の導電部6が形成されたSi基板14と、導通ビア1a、1bが形成されたセラミック基板2とを樹脂面同士(Si基板側の第1の樹脂層20、セラミック基板2側の第2の樹脂層25)が接するように位置合わせをしながら重ね合わせ、圧着して接合体26を作製する(h)。その後、接合体26に加熱・冷却処理を施して温度変化を付与し、Si基板14側の密着層16とセラミック基板2側の第1の電極膜9と間で界面剥離を生じさせ、Si基板14をキャパシタ部11から分離する。

(もっと読む)

半導体装置の絶縁膜形成方法

【課題】 本発明は、プラズマ窒化法を用いたシリコン酸化膜の窒化処理においてシリコン基板界面近傍に窒素を偏析させることなく、シリコン酸化膜表面近傍のみに高濃度の窒素を導入し、信頼性の高いゲート絶縁膜を形成することを目的とする。

【解決手段】 本発明の絶縁膜の形成方法は半導体基板上にシリコン酸化薄膜を有する基体表面を高真空に保持された真空容器内で真空紫外光を照射する工程と、真空紫外光照射後に基体を大気に暴露することなく、高真空状態に保持された真空容器内で窒化或いは酸窒化いずれかの処理を行う工程とを有することを特徴とする。

(もっと読む)

半導体回路装置

【課題】

チャージ・ポンプ回路の電流能力のばらつきを低減する。

【解決手段】

チャージ・ポンプ回路110の押し上げ容量素子C1と発振回路123の容量素子の容量膜(酸化絶縁膜)が実質的に同一となるように、チャージ・ポンプ回路110の押し上げ容量素子C1と発振回路123の容量素子が形成される。さらに好ましくは、容量素子C1と容量素子C2は、同一プロセスにおいて同時に形成される。各容量素子の容量膜をこのように形成することによって、容量素子C1と容量素子C2の容量膜のばらつきに起因する容量比のばらつきを大きく低減し、チャージ・ポンプ回路110の電流能力Icpのばらつきを低減することができる。

(もっと読む)

半導体デバイスおよびかかるデバイスを製造する方法

本発明は、導体線路を含む1つまたは複数の受動電子構成要素(20)がその上に設けられた、電荷を含む誘電体層(3、4)で覆われた、高抵抗半導体基板(2)を有する半導体本体(1)を備える半導体デバイス(10)であって、この受動素子(20)の位置で、ある領域(5)が半導体基板(2)と誘電体層(3、4)の間の境界面に存在し、その結果、この領域(5)の位置で、電荷によってデバイス(10)中に誘起された電気伝導チャネルの伝導度が制限される、半導体デバイス(10)に関する。本発明によれば、領域(5)は、堆積によって形成され、半絶縁材料を含む。その結果、反転チャネルが半絶縁領域(5)内に形成されるので、デバイス(10)は高周波電力損失が非常に低い。デバイス(10)はさらに、より高い温度バジェットを可能にし、したがって半導体本体(1)内への能動半導体素子(8)の集積化を可能にする。領域(5)に非常に適した半絶縁材料は、SiC、SIPOS、またはPOLYDOXである。  (もっと読む)

(もっと読む)

マイクロ波伝送線路

【課題】シリコン基板を信号伝播媒体とするマイクロ波伝送線路を長期安定性を維持しながら伝送損失の劣化を防止できるようにする。

【解決手段】高抵抗シリコンからなる基板1の主面上には、酸化シリコンからなる保護膜2、酸化アルミニウムからなる電位中和膜3及びストリップメタル4が順次形成されている。保護膜2は正の空間電荷を持ち、電位中和膜3は負の空間電荷を持ち、信号電界が基板1と保護膜2と電位中和とを伝播し、保護膜2及び電位中和膜3の各膜厚は、基板1の表面近傍における電位が中和されるように調整されている。

(もっと読む)

基板上に多機能誘電体層を形成する方法

本発明は、多機能誘電体層を基板上、特に基板上に露出している金属配線系上に形成する方法に関する。本発明の目的は、銅による配線を形成するための多機能パッシベーション層を容易に形成する方法を提供するとともに、エレクトロマイグレーション、ストレスマイグレーション、および接着性を向上させる方法を提供することにある。本発明によれば、更なる金属層(5)を、露出した金属配線(3)の表面上に堆積することによって、本発明の目的は達せられる。この金属層は少なくともその一部が非導電性の金属酸化物に変換され、誘電体層となっている。  (もっと読む)

(もっと読む)

321 - 340 / 340

[ Back to top ]