Fターム[5F044AA08]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | パッケージの配線部との接続 (63) | 配線部が多層のもの (10)

Fターム[5F044AA08]に分類される特許

1 - 10 / 10

半導体装置

【課題】ワイヤボンドの非有効エリアとされていた、傾斜部やビア上、ビアカバー上に安定に、かつ少ない接続面積でワイヤを接続できる半導体装置を提供する。

【解決手段】開口部と、開口部内に設けられたダイパッドと、開口部の周囲に設けられた傾斜部と、インナリードと、を有するパッケージと、第1の電極パッドを有し、かつ、ダイパッド上に搭載された半導体チップと、インナリードと第1の電極パッドとを接続する第1のワイヤと、を備え、インナリードの少なくとも一部は、傾斜部上に配置され、前記傾斜部上において、かつ、前記インナリード上には、第1の部材が配置され、前記第1の部材上には、前記第1のワイヤが接続されている半導体装置を提供する。

(もっと読む)

半導体チップ搭載用基板及びその製造方法

【課題】金めっき皮膜を薄くすることが可能で、半導体チップ搭載用基板の製造コストを低くすることが可能である。さらに、微細配線を形成する場合であっても、ブリッジの発生を低減でき、しかも優れたワイヤボンディング性及びはんだ接続信頼性を得ることが可能な半導体チップ搭載用基板及びその製造方法を提供する。

【解決手段】樹脂を主成分とする絶縁層21と、絶縁層21の上に形成された銅回路22、3、5と、銅回路22、3、5上の少なくとも一部に形成された電解ニッケルめっき皮膜7と、電解ニッケルめっき皮膜7の少なくとも一部に形成され、金めっき皮膜8を形成したワイヤボンディング用端子と、を有する半導体チップ搭載用基板であって、金めっき皮膜8のニッケルめっき皮膜7とは反対側の面の結晶粒径の平均値が、5μm以上である。

(もっと読む)

プリント配線板に付いた半導体

【課題】既存の半導体に合わせてプリント配線板を設計しなくても対応可能としたプリント配線板に付いた半導体を提供する。

【解決手段】ワイヤボンディングは絶縁して交差も可能なように組み合わせるとともに、ボンディングパットに関してもチップ上に組み替え可能とする。また、積層基板のボンディングも上下層に絶縁交差可能とする。これにより、ピン間スペースを広くもつことができ設計の自由度が増す。また、交流信号のあるピン同士の場合電極を広くとれ高品質な配線板になる。積層基板のボンディングも上下層に絶縁交差するものになる。また、大きなリードフレームにチップを複数搭載した場合は、金銀ワイヤ毎まとめて回収することができる。これにより複数のチップ間も設計が楽になり設計の選択肢が増える。

(もっと読む)

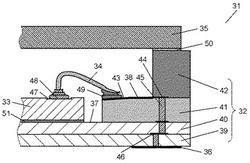

ワイヤボンドの接合構造及び接合方法

【課題】接合機との干渉を防止し、半導体モジュールの小型化を図ること。

【解決手段】ワイヤボンドの接合構造は、バスバ11,13を多段構造に構成し、バスバ11,13にワイヤ15,16を接合する。詳しくは、上段バスバ13及びそれを支持する上段支持部14を含む上段バスバ部材6が、下段バスバ11及びそれを支持する下段支持部12を含む下段バスバ部材5と別体に構成される。下段バスバ11と下段ワイヤ15とが接合され、上段バスバ部材6が下段バスバ部材5に固定され、その後に、上段バスバ13と上段ワイヤ16とが接合される。下段バスバ部材5の上面であって、下段バスバ11と下段ワイヤ15との接合部15aの近傍を除く領域に、上段バスバ部材6が固定される。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子の破損を抑制すること。

【解決手段】上面に凹部18を備える基板10の前記凹部18内に第1半導体素子30を実装する工程と、前記第1半導体素子30の上面上に弾性体40を配置する工程と、第2半導体素子50の下面が前記弾性体40の上面に接するように前記第2半導体素子50の上面に荷重をかけて前記第2半導体素子50を前記基板10に接合する工程と、を含む半導体装置の製造方法。

(もっと読む)

集積回路基板及びマルチチップ集積回路素子パッケージ

【課題】電気抵抗及び信号遅延を相対的に改善することができるボンドフィンガを採用した集積回路基板及び集積回路素子パッケージを提供する。

【解決手段】表面に複数の導電性パッドを有する集積回路チップと、集積回路チップが搭載される印刷回路基板とを有し、印刷回路基板は、複数の導電性パッドに対応して互いに異なる第1及び第2高さを有して交互に配列される複数の第1及び第2導電性ボンドフィンガと、第1導電性ボンドフィンガ114を第2導電性ボンドフィンガ113と比べて相対的に高い高さを有するように支持する複数の第1絶縁支持体112とを含み、さらに、複数の導電性パッドの内の複数の第1導電性パッドと、対応する第1導電性ボンドフィンガとを各々電気的に接続する複数の第1電気接続体と、複数の導電性パッドの内の複数の第2導電性パッドと、対応する第2導電性ボンドフィンガとを各々電気的に接続する複数の第2電気接続体とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

半導体装置

【課題】プリント配線板に実装された半導体チップの集積回路に安定した電源を供給する。

【解決手段】半導体チップ1を実装した第1のプリント配線板2の上に、分岐された電源の第2のプリント配線板として第2のプリント配線板3を配置する。半導体チップ1の集積回路を囲むように配置されたボンディングパッド6よりも内側に、電源用のボンディングパッド7を配置し、ボンディングワイヤ8bによって第2のプリント配線板3のボンディングパッド5に接続する。電源用のボンディングワイヤ8bを短くすることで、電源の供給を安定化する。

(もっと読む)

リードフレーム基盤及び基板基盤半導体パッケージ用ボンディング構造とその製造方法

【課題】 リードフレーム基盤及び基板基盤半導体パッケージ用ボンディング構造とその製造方法を提供する。

【解決手段】 本発明は、半導体素子パッケージのボンディング構造において、チップダイのサイズが増加されないながらボンディングワイヤーのボンディング角が許容限界内に維持されるダイ−対−パッケージボンディング構造に関するものである。これにより、隣接したボンディングワイヤーの間の短絡発生が緩和されるか、或いは除去され、製造中の素子ネットダイカウント(ネットダイ数)を増加することができる

(もっと読む)

多層ボンディング構造の半導体デバイスのワイヤスイープを低減又は除去する方法とその方法によって製造された装置

【課題】 低い製造コストと高い信頼性で半導体デバイスを製作する方法を提供する。

【解決手段】 多層ワイヤボンディング半導体デバイスをパッケージ化する方法は、多層ワイヤボンディング半導体デバイスにおいて各層で素子間の接続をする複数の導線の少なくとも2本の一部のみを横切って絶縁材料を適用することを含む。その方法は、又、導線と素子を封止することにより、半導体デバイスをパッケージ化することを含む。

(もっと読む)

1 - 10 / 10

[ Back to top ]