Fターム[5F045DA68]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の物性 (649) | 水素含有量・結合水素量 (37)

Fターム[5F045DA68]に分類される特許

1 - 20 / 37

半導体装置の製造方法及び半導体装置

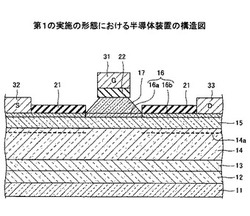

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に、第1の半導体層14、第2の半導体層15及びp型の不純物元素が含まれている半導体キャップ層16を順次形成する工程と、前記半導体キャップ層を形成した後、開口部を有する誘電体層21を形成する工程と、前記開口部において露出している前記半導体キャップ層の上に、p型の不純物元素が含まれている第3の半導体層17を形成する工程と、前記第3の半導体層の上にゲート電極31を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

表示装置およびその製造方法

【課題】微結晶シリコンを用いたボトムゲート型の薄膜トランジスタのオン電流に対するオフ電流の割合を減少させること。

【解決手段】表示装置に含まれる薄膜トランジスタは、ゲート電極が設けられた導電層と、前記導電層の上に設けられたゲート絶縁層と、前記ゲート絶縁層の上面に接するとともに前記ゲート電極の上方に設けられ、微結晶シリコンを含む第1の半導体膜と、前記第1の半導体膜の上面に接する第2の半導体膜と、前記第2の半導体膜に電気的に接続される第1の電極と、前記第2の半導体膜に電気的に接続される第2の電極と、を含む。前記第1の半導体膜における水素濃度は、前記ゲート絶縁層との界面と前記第2の半導体膜との界面との中間で最小となり、前記第1の半導体膜と前記第2の半導体膜との境界における酸素濃度は、前記第1の半導体膜の中央および前記第2の半導体膜の中央のうち少なくとも一方の酸素濃度以下である。

(もっと読む)

微結晶シリコン膜形成方法、微結晶シリコン膜成膜装置および表示装置

【課題】微結晶シリコン膜の移動度を高める。

【解決手段】高密度プラズマを用いて少なくとも(220)の結晶方位配列に成長させるように微結晶シリコン膜を形成する第1の工程を有し、第1の工程時、微結晶シリコン膜の結晶方位配列(111)に対する結晶方位配列(220)への成長比率が高くなるように、被処理体近傍の温度を300〜350℃の範囲内に設定し、総流量に対する水素ガスの流量比を高めた成膜ガスを供給する。これにより、ダングリングボンドの少ない微結晶シリコン膜20を形成して、移動度を高めることができる。

(もっと読む)

プラズマCVD装置及びアモルファス膜の形成方法

【課題】基体の温度を高くしなくも緻密なSi系アモルファス膜を形成でき安定性に優れるプラズマCVD装置及びSi系アモルファス膜の形成方法を提供する。

【解決手段】プラズマCVD装置1004において、誘導エネルギー蓄積型のパルス電源1028からチャンバの内部に収容された電極対1012,1016へ直流パルス電圧を印加する。

(もっと読む)

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

半導体基板、半導体基板の製造方法および垂直共振器面発光レーザ

【課題】垂直共振器面発光レーザ用の半導体基板におけるp型結晶層をV/III比が小さいエピタキシャル条件で形成するとともにp型結晶層の電気抵抗を低減する。

【解決手段】垂直共振器面発光レーザ用の半導体基板であって、半導体基板はコンタクト層として機能するp型結晶層を有し、p型結晶層が、3−5族化合物半導体からなり、2×1018cm−3以上、1×1019cm−3以下の濃度の水素原子を含む半導体基板を提供する。p型結晶層として、p型GaAs層が挙げられる。p型結晶層が、p型不純物原子として炭素原子を含んでもよい。

(もっと読む)

結晶性半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性半導体の核生成を均一にする。

【解決手段】ガス管から導入された成膜ガスを拡散する第2のガス拡散室と、前記第2のガス拡散室と分散板を隔てて設けられ、該分散板のガス孔から成膜ガスが導入される第1のガス拡散室と、を介して、前記第1のガス拡散室とシャワー板を隔てて設けられた処理室内に該シャワー板のガス孔から成膜ガスを供給し、前記成膜ガスを導入することによって前記処理室内の圧力を2000Pa以上100000Pa以下とし、前記処理室内に電界を生じさせる一対の電極のうち、一方の電極面から電界強度が均一な高周波電力を供給することでグロー放電プラズマを生成させ、前記対向する電極の他方に配された基板上に結晶核を生じさせ、その後、該結晶核を成長させて結晶性半導体膜を作製する。

(もっと読む)

III族窒化物半導体光素子、III族窒化物半導体光素子を形成する方法、III族窒化物半導体膜を成長する方法及びエピタキシャル基板

【課題】p型III族窒化物半導体の電気特性を向上できるIII族窒化物半導体光素子を提供する。

【解決手段】窒化ガリウム系半導体領域15及び窒化ガリウム系半導体領域19は、基板13の主面13a上に設けられる。窒化ガリウム系半導体領域19は、p型ドーパントとしてマグネシウムを含むIII族窒化物半導体膜21を有しており、III族窒化物半導体膜21は、III族構成元素としてアルミニウムを含む。III族窒化物半導体膜21の酸素濃度は、1.0×1017cm−3以上の範囲にあり、III族窒化物半導体膜21の酸素濃度は、1.5×1018cm−3以下の範囲にある。また、III族窒化物半導体膜21の水素濃度は1.0×1017cm−3以上の範囲にあり、III族窒化物半導体膜21の水素濃度は1.5×1018cm−3以下の範囲にある。

(もっと読む)

半導体膜の製造方法および半導体膜の製造装置

【課題】大面積の良質な半導体膜を安定して簡便に作製することが可能な半導体膜の製造方法を得ること。

【解決手段】前記カソード電極上に堆積した半導体膜を前記カソード電極を加熱することにより加熱する工程と、前記加熱された半導体膜中から離脱した脱離水素原子量を前記カソード電極の温度に応じて複数回測定する工程と、前記脱離水素原子量の測定結果を分析して前記半導体膜の膜質を反映させて製膜条件を調整するための指標となる膜質情報を取得する工程と、前記膜質情報に基づいて前記半導体膜の製膜条件を第2の製膜条件に再設定する工程とを含む。

(もっと読む)

光起電力装置

【課題】 この発明は、プラズマCVD法による非晶質系半導体薄膜層を形成した以降の加熱工程で太陽電池の出力特性の低下を抑制することを課題とする。

【解決手段】 この発明は、n型単結晶シリコン基板と水素を含有するp型非晶質シリコン層との間に、水素を含有する実質的に真性な非晶質シリコン層を設けた光起電力装置において、前記p型非晶質シリコン層と前記真性な非晶質シリコン層との間に、前記真性な非晶質シリコン層の水素濃度より水素濃度が低いトラップ層を設ける。このトラップ層により、真性な非晶質シリコン層からp型非晶質シリコン層への水素拡散を抑制する。

(もっと読む)

薄膜半導体装置及びその製造方法

【課題】電流の立ち上り特性、リーク電流特性に優れた結晶性シリコン薄膜半導体装置を提供する。

【解決手段】基板100上に、アモルファスシリコン層101、パタンニングされたソース及びドレイン電極層102、基板100側でアモルファスシリコン層101に接触しかつソースおよびドレイン電極層102にオーミック接触した結晶性シリコン層104、ならびにアモルファスシリコン層101に接触した結晶性シリコン層104の基板100とは反対側にゲート絶縁層105を挟んで配置されたゲート電極層106、を有することを特徴とする薄膜半導体装置。

(もっと読む)

III−V族化合物半導体素子

【課題】III−V族化合物半導体素子において、長時間駆動時のオン抵抗増大による不良を抑制し、良品率を高めて生産歩留まりを向上させる。

【解決手段】III−V族化合物半導体素子は、基板(102)の上方に設けられたチャネル層(104)と、このチャネル層上にヘテロ界面を形成するように設けられたバリア層(105)と、このバリア層上に設けられた複数の電極(106、107、108)と、これらの電極の少なくとも一部の領域を除いてバリア層の全表面を覆うように設けられた絶縁層(109)と、この絶縁層上に積層された水素吸着層(110)、または絶縁層と水素吸着層とが一体化された一体化層を含んでいる。

ここで、水素吸着層(110)または一体化層がその水素を吸い寄せる力によって、その層内に存在する水素原子が半導体層側へ拡散することを抑制し得る。

(もっと読む)

アモルファスカーボン及びその製造方法

【課題】電気抵抗率の低いアモルファスカーボン及びその製造方法を提供する。

【解決手段】アモルファスカーボンは、水素濃度が5〜30%(atm)であり、ドーピング元素を含有している。P型ドーピングにはホウ素、N型ドーピングには窒素を10%(atm)以下の濃度で含有させる。これによって、電気抵抗率が低く導電型を制御可能な、太陽電池などの光電変換素子用アモルファスカーボンが実現可能となる。

(もっと読む)

高品質半導体材料

水素化シリコン系半導体合金は、1016cm−3未満の欠陥密度を有する。その合金は、水素化シリコン合金または水素化シリコンゲルマニウム合金を含み得る。合金の水素含有量は、一般に15%未満であり、或る例では11%未満である。その合金を組入れたタンデム光発電装置は、低いレベルの光劣化を示す。或る例では、その材料は高速VHF堆積プロセスで作製される。 (もっと読む)

ダイヤモンド電界効果トランジスタ及びその作製方法

【課題】最高動作温度が高くドレイン電流密度が大きい、かつ、長時間の大電力動作にも耐える信頼性のある、実用的なダイヤモンドFETを提供すること。

【解決手段】ダイヤモンド結晶1を用意し、マイクロ波CVD装置のリアクター内で水素プラズマ(Hで表す)を照射し、水素を含む表面層2を形成する(図1(a))。第1の表面層2上の一部の領域に、空間的に分離して、厚さ600nmの金薄膜31、32を蒸着する。これは、各ソース電極31、ドレイン電極32になる。ソース電極31とドレイン電極32との間に、空間的に分離して、Al薄膜4を蒸着する(図1(c))。このAl薄膜4はゲート電極4になる。試料にNO2を供給し、第1の表面層2上に第2の表面層5を形成する(図1(d))。露出した第2の表面層5全体を覆うように保護層6を第2の表面層5上に堆積させる(図1(e))。

(もっと読む)

成膜装置

【課題】材料溶液を完全に気化し、基板に安定供給することができる成膜装置を提供する。

【解決手段】気化器409は、内部空間を有する容器900と、容器900内の空間を加熱し、霧状の材料溶液を気化させる加熱部907とを備える。霧化部408は、内部空間に向かって材料溶液と霧化支援ガスを噴出し、ヒーター908を内蔵するフィン907により霧化した材料溶液を加熱する。これにより、溶液材料を効率よく気化することができる。

(もっと読む)

プラズマCVD装置及びプラズマCVD法

【課題】欠陥が低く、高次シランの混入のない高品質なアモルファスシリコン薄膜を得ることができるプラズマCVD装置、及びプラズマCVD法を提供する。

【解決手段】プラズマCVD装置は、真空容器2と、該真空容器2内の真空度を保持する排気系と、被成膜基板5を置くための接地電極4と、該被成膜基板5を加熱するための加熱機構7と、原料ガスを供給可能な放電電極3と、該原料ガスにプラズマを発生させるために該放電電極3に高周波電力を印加する高周波電源9と、を備えた平行平板型プラズマCVD装置1において、該放電電極3には該真空容器2内に原料ガスを供給するための凹部8が設けられており、該凹部8の壁面には原料ガスを凹部内に供給するための原料ガス供給孔が設けられており、該原料ガス供給孔は原料ガスを該凹部8内に凹部の壁面の方向に向けて放出するように形成する。

(もっと読む)

半導体層とこの半導体層を用いた半導体装置および表示装置

【課題】水素終端化された高品質な多結晶Si膜を含む半導体薄膜を低温、高速成膜することで、良好な特性のTFTを安定して実現し、高品質、高画質の半導体装置および表示装置を提供する。

【解決手段】絶縁性基板上に形成したSi、Ge、F、Hを含有する半導体層4を、良好な結晶性が得られる反応熱CVD法で形成した多結晶SiGe膜または多結晶Si膜を第一層4aとその上層の第二層4bとの複数層の連続成膜で積層構造に構成し、該半導体層4中のH濃度を絶縁性基板1側に対して表面側にある第二層4bで高くした。

(もっと読む)

半導体素子、エピタキシャルウエハおよびそれらの製造方法

【課題】水素濃度を減らしながら、半導体素子を容易に得ることができる、製造方法およびその方法で製造された半導体素子を提供する。

【解決手段】InP基板1上にN含有InGaAs系層3をMBE法で成長させ、その後、600℃以上800℃未満の熱処理を施し、上記の熱処理により、N含有InGaAs系層3の平均水素濃度を2×1017個/cm3以下とする。

(もっと読む)

表示装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する表示装置を量産高く作製する方法を提案することを課題とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する表示装置において、逆スタガ型薄膜トランジスタは、ゲート電極上にゲート絶縁膜が形成され、ゲート絶縁膜上にチャネル形成領域として機能する微結晶半導体膜(セミアモルファス半導体膜ともいう。)が形成され、微結晶半導体膜上にバッファー層が形成され、バッファー層上に一対のソース領域及びドレイン領域が形成され、ソース領域及びドレイン領域に接する一対のソース電極及びドレイン電極が形成される。上記において、微結晶半導体膜を表面に水素プラズマを作用させたゲート絶縁膜上に形成する。

(もっと読む)

1 - 20 / 37

[ Back to top ]