Fターム[5F046FC01]の内容

半導体の露光(電子、イオン線露光を除く) (57,085) | 位置合わせマークの検出一般及び検出の補助 (970) | ウェハマーク部の保護、保存 (21)

Fターム[5F046FC01]に分類される特許

1 - 20 / 21

半導体装置の製造方法

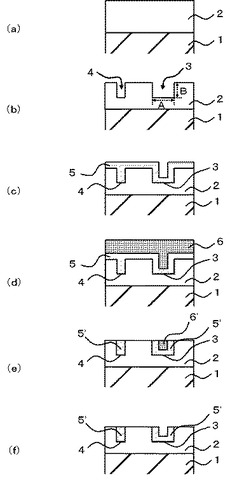

【課題】フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる位置合わせ用の目合わせパターンを形成することを課題とする。

【解決手段】基板1上に第1絶縁層2を形成する工程と、第1絶縁層2に、1つ以上の接続孔4と、接続孔4よりも幅が広い位置合わせ用の目合わせパターンを形成するための目合わせ孔3と、を形成する工程と、第1絶縁層2の上に、接続孔4が金属で完全に埋まり、かつ、目合わせ孔3が金属で完全に埋まらないよう金属膜5を形成する工程と、金属膜5の上に、少なくとも目合わせ孔3が完全に埋まるように第1フォトレジスト膜6を形成する工程と、第1絶縁層2をストッパーとしてCMP処理を行うことで、第1フォトレジスト膜6及び金属膜5の一部を除去する工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

重ね合わせ精度評価方法

【課題】パターンの重ね形成における重ね合わせ精度を正確且つ簡便に評価する。

【解決手段】予めアライメントマークが設けられ、表面にレジスト層が形成されたテストウエハをステージ上にロードする(ステップS1)。そのテストウエハに対し、アライメントマークの検出を伴うアライメント(EGA)を行い(ステップS2)、その結果に基づいて1回目の露光を行いレジスト層にテストパターンの潜像を形成する(ステップS3)。そして、テストウエハをステージ上に載せ直し(ステップS4,S5)、現像することなく、再度アライメント(EGA)を行い(ステップS6)、その結果に基づいて2回目の露光を行いレジスト層にテストパターンの潜像を形成する(ステップS7)。テストウエハを現像後得られる、2つのパターン(レジスト像)の位置関係に基づいて重ね合わせ精度を評価する(ステップS8)。

(もっと読む)

アライメントマーク構造およびこれを用いた位置合わせ方法

【課題】高精度な位置合わせ座標が得られ、高精度で位置合わせを行うことのできるアライメントマーク構造を提供する。

【解決手段】第1の方向に延在する第1溝1cと、第1の方向と直交する方向に延在する第2溝1dとを備えた凹部1aからなり、第1溝1cおよび第2溝1dの側壁の上端部1bが、研磨により除去されており、第1溝1cの延在方向および第2溝1dの延在方向と交差するデータ検出直線13aの延在方向における第1溝1cの側壁の上端部の一方側および他方側の位置座標Xa、Xbと、データ検出直線13aの延在方向における第2溝1dの側壁の上端部の一方側および他方側の位置座標Xc、Xdとのそれぞれと、特定位置座標P0とのデータ検出直線13aの延在方向における距離の平均値が、特定位置座標P0と凹部1aとの距離として検出されるものであるアライメントマーク構造1とする。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ形成工程を有する半導体装置の製造方法において、並列pn構造の形成と同時に位置合わせマーカを形成し、製造プロセスの効率化を図ること。

【解決手段】n型シリコン基板21の表面にn型半導体22を形成し、n型半導体22の表面にマスク酸化膜を形成する。次いで、フォトリソグラフィおよびエッチングによってマスク酸化膜を開口し、シリコン基板21に達する第1のトレンチを形成する。同時に、第1のトレンチよりも深い第2のトレンチが形成される。次いで、第1のトレンチをp型半導体27で埋める。同時に、第2のトレンチがp型半導体28で埋められる。次いで、n型半導体22の表面を研磨し平坦化する。ここまでのプロセスで、並列pn構造が形成される。このとき、第2のトレンチの上部はp型半導体28で埋まらずに残り、並列pn構造の表面に窪みが形成される。この窪みが、後の工程において位置合わせマーカとして機能する。

(もっと読む)

露光方法及び露光装置

【課題】露光領域にのみ感光するレジストを付与できる露光方法を提供する。

【解決手段】吐出装置40と基板Wとを相対移動させたとき、エンコーダ41からの情報と記憶したパターンデータとに基づいて、判別手段を兼ねる吐出装置40が、吐出ヘッドに正対する位置に非パターン領域が到達したと判断した場合、吐出装置40は遮光材を塗布する。これにより任意の形状・大きさでレジストを残すことができ、図3にハッチングで示すようにレジストを塗布されたパターン領域Pと、その間のレジストを塗布されない非パターン領域NPとを形成できる。

(もっと読む)

フォトマスク及び半導体装置の製造方法

【課題】下地基板上に複数の層が積層された半導体装置を製造するに当たり、同一のパターンが形成される場合に、一つのマスクを共通して用いる。

【解決手段】下地用マスク11は、マーク領域34に第1アウターマーク用パターン41と、第1アウターマーク用パターンを行方向にs×(X1+dX)、又は、−(n−s)×(X1+dX)移動し、かつ、列方向にt×(Y1+dY)、又は、−(m−t)×(Y1+dY)移動した位置に第2アウターマーク用パターン46とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁膜表面のCMPのアライメントマークへの影響を排除し、アライメントマークの検出を精度良く確実に行うことができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、素子分離絶縁膜3上に位置するアライメントマーク部31内のゲート積層膜35を選択的に除去する工程と、周囲がゲート積層膜35で囲まれたアライメントマーク部31内にアライメントマーク32を形成する工程と、半導体基板2の上面に第1の層間絶縁膜15を形成する工程と、アライメントマーク部31内の第1の層間絶縁膜15を選択的に除去する工程と、アライメントマーク32周囲の素子分離絶縁膜3を除去もしくは薄膜化する工程と、アライメントマーク32を用いてフォトリソグラフィーのアライメントを行い、第1の層間絶縁膜15上にパターンを形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】選択エピタキシャル法を用いてソース・ドレイン領域を形成する半導体装置の製造方法において、位置検出精度が高い重ね合わせ位置検出マークを作成する。

【解決手段】SOI基板101のマーク形成領域120内に溝106を形成し、基板全面にゲート絶縁膜用の絶縁膜107およびゲート電極用の導電膜108を形成し、ゲート絶縁膜およびゲート電極を形成すべき領域とマーク形成領域120とを覆うマスクパターン109を形成する。これにより、エッチングによってゲート絶縁膜201とゲート電極202とを形成したとき、マーク形成領域120には導電膜108による阻止膜が形成される。その後、基板110にシリコンを選択エピタキシャル成長させることにより、ソース・ドレイン領域を形成する。このとき、マーク形成領域120には、阻止膜があるためにシリコンが堆積せず、これにより重ね合わせ位置の検出精度が向上する。

(もっと読む)

改良されたリソグラフィ用アライメント方法及びシステム

【課題】アライメントマークを保護、再生する。

【解決手段】アライメントマーク401下部構造上方に位置するハードマスク414の部位が選択的に所定照射線量で露光される。この照射線量が照射されたハードマスクコーティングの表面領域421はハードマスク表面の他の領域に対して上昇する。ハードマスクの上昇領域416は下層のアライメントマーク401のトレンチ406に対応する位置に形成されており、この上昇領域416は下層のアライメントマーク401の水平位置が保存された新たなアライメントマークとなる。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】 FRAMの強誘電体容量素子を形成する際に強誘電体を酸素雰囲気中で熱処理しても位置合わせマークの溝に埋設するW膜の酸化を防止することができる

【解決手段】 強誘電体容量をメモリとして用いた半導体装置の製造に際して、溝状に掘って形成した位置合わせマーク1に埋設したW膜2が酸化することを防止した半導体装置の製造方法において、該強誘電体容量を形成する前に、該W膜2をP−SiN(SiON)からなる酸化防止膜3によって覆い、次いで、該酸化防止膜3に熱処理を行って予め熱収縮させるように構成する。

(もっと読む)

重ね合わせ測定マーク及びそのパターン形成方法

【課題】 半導体素子の微細化にともない重ね合わせ測定マークにおける基準マークの膜剥れが発生する。この膜剥れにより重ね合わせの位置ずれを精確に測定できなくなり所望の重ね合わせ精度が得られないという問題がある。

【解決手段】 重ね合わせ測定マークの基本マークパターンの各辺に微小な突起パターンを付加することで、重ね合わせ測定マークの膜剥れを防止できる。膜剥れがない重ね合わせ測定マークにより重ね合わせの位置ずれを精確に測定し、露光機にフィードバックすることで更に重ね合わせ精度の良いパターン形成結果が得られる。

(もっと読む)

整列マーク膜を備える半導体素子及びその製造方法

【課題】整列マーク膜を備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上のパッド電極膜と、半導体基板上に形成され、組立工程の整列キーとして利用される整列マーク膜と、半導体基板上に形成され、パッド電極膜の上部の少なくとも一部分及び整列マーク膜の上部の少なくとも一部分をそれぞれ露出するパッシベーション膜と、パッシベーション膜の少なくとも一部分を覆い、パッシベーション膜から露出されたパッド電極膜の上部を露出し、パッシベーション膜から露出された整列マーク膜を覆っている透光性保護膜と、を備える半導体素子である。

(もっと読む)

加工方法及び半導体装置の製造方法

【課題】 被加工膜上に保護膜を形成して光加工を行う技術において、保護膜の除去を容易にする。

【解決手段】 被加工膜107上に有機樹脂で構成された有機膜149を形成する工程と、有機膜149の内部応力を小さくする工程と、有機膜149に加工光を照射し、加工領域の有機膜149を選択除去する工程と、有機膜149をマスクとして、被加工膜107をエッチングする工程を有する。

(もっと読む)

アライメントマークの形成方法

【課題】 配線膜のフォトリソグラフィを高精度に行うためのアライメントマークの形成方法を提供することを目的とする。

【解決手段】 基板101の上に、アライメントマークの溝105となる領域を囲むように、該アライメントマークを形成する領域のディッシングを防止するためのディッシング防止膜103を形成する。ディッシング防止膜103を覆うように基板の上に層間絶縁膜104を形成する。層間絶縁膜104の表面を化学的機械的研磨法により研磨する。層間絶縁膜104中に、アライメントマークの溝105を形成する。アライメントマークの溝105の部分で、その表面にマークである溝ができるように、層間絶縁膜104の上に配線膜107を形成する。これにより、配線膜107の表面に、溝であるアライメントマークが形成される。

(もっと読む)

露光装置、マスク及びデバイスの製造方法

【課題】 基準部材における表面の撥液性の劣化状態を容易に把握可能な露光装置、及び高集積度のデバイスを歩留まりよく製造可能なデバイスの製造方法を提供する。

【解決手段】 投影光学系の像面側に配置されるウエハステージ上に設けられた基準部材44上の各基準マークFM、AISマークAM毎の使用頻度、使用時間、照射されたパルス紫外光のエネルギー量等の計測光の特性が、主制御系に入力される。主制御系は、これらの情報から、各基準マークFM、AISマークAM毎のパルス紫外光の累積エネルギー量を算出し、記憶するとともに、予め記憶されている被曝エネルギー量と撥水層47の劣化度との相関関係から、各基準マークFM、AISマークAM毎の撥水層47の劣化状態を推定する。

(もっと読む)

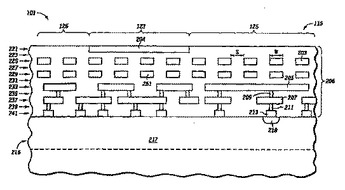

垂直構造体でのフォトマスクの再使用を可能にするための、繰り返される重ね合わせマークおよび繰り返される位置合わせマークの隠蔽

モノリシックな三次元メモリアレイの作成に際し、フォトマスクを複数回使うことができる。フォトマスクの再使用により、第2、第3またはそれ以降の基準マーク例が形成される。ステッパはこれらの基準マーク例を用いて位置合わせ(位置合わせマーク)を達成しかつ同じ基準マークの先行例の真上に達成された位置合わせ(重ね合わせマーク)を測定する。同じ基準マークの先行例が、基準マークの現在例との干渉の原因となることがあり、位置合わせおよび測定が複雑化する場合があるが、本発明の方法を用いると、遮光構造が同じ基準マークの後続例間に垂直に介設され、干渉が防止される。  (もっと読む)

(もっと読む)

レジストパターン形成方法

【課題】 パターンの重ね合わせ精度を向上させたレジストパターン形成方法を提供する。

【解決手段】 アライメントマークを用いてフォトマスクと半導体基板との位置合わせを行ってフォトマスクを転写したレジストパターンを形成する方法であって、アライメントマークが設けられた半導体基板または層に対してその上にまたは他の層を介して形成された被加工膜上のアライメントマークの形成領域に光透過性膜を形成する工程と、光透過性膜を覆う反射防止膜を被加工膜上に形成する工程と、光透過性膜上の反射防止膜の膜厚が所定の厚さになるまで反射防止膜を削る工程と、反射防止膜上にレジストパターンを形成する工程とを有する。

(もっと読む)

半導体製造工程のアライメント測定方法

【課題】半導体製造工程のアライメント測定方法を提供する。

【解決手段】この方法は、基板上に第1アライメントキーを形成する段階と、前記第1アライメントキーを覆う物質膜を形成する段階と、前記物質膜上に不透明膜を形成する段階と、前記不透明膜にイオン注入工程を実施して不透明膜の吸光係数を低くする段階とを含む。前記不透明膜上にフォトレジスト膜を形成し、前記吸光係数が低くなった不透明膜を透過する光を照射して前記第1アライメントキーの位置を測定する。

(もっと読む)

露光方法

【課題】 ワークに形成されるパターンの数が、マスクに形成されたパターンの数で割り切れないような場合であっても、本来使用を想定した個数のアライメントマークを使用して位置合せし、露光できるようにすること。

【解決手段】 マスクMには複数の同一パターンが形成されている。マスクMとワークWを相対的に移動させ、アライメント顕微鏡2により、マスクMのアライメントマークと、ワークWのアライメントマークを検出し、マスクMとワークWの位置合わせを行い、マスクM上の複数の同一パターンをワークW上に繰り返し露光する。マスクMと光照射部1の間には、マスキングブレード6が設けられ、マスクMに形成されたパターンをワークW上に露光する際、予め設定された手順でマスキングブレード6により、マスクMに形成された複数の同一パターンのうちの一部のパターンを遮光して露光する。

(もっと読む)

半導体の整合補助部

半導体デバイス用の整合補助部(115)に関する。整合補助部は、高い反射度を有する領域(123)と、低い反射度を有する隣接領域(125)とを備える。低い反射度を有する領域には、半導体デバイスの相互接続層(225)に配置され、かつ半導体デバイスの能動回路(218)の上方に配置されている、1層以上のタイル(203)が含まれる。一部の例では、整合補助部のタイルの走査方向への間隔は、整合補助部の走査に使用される光(例えば、レーザ光)の波長より短い。他の例では、整合補助部のタイルの走査方向への幅が、整合補助部の走査に使用される光の波長より短い。  (もっと読む)

(もっと読む)

1 - 20 / 21

[ Back to top ]