Fターム[5F047CA02]の内容

ダイボンディング (10,903) | ダイ(材料) (151) | 半導体(Siを除く) (52) | 3−5族 (22)

Fターム[5F047CA02]に分類される特許

1 - 20 / 22

半導体装置およびその製造方法

【課題】耐イオンマイグレーションに優れた半導体装置およびその製造方法を提供する。

【解決手段】実施の形態に係る半導体装置は、導体ベースプレートと、導体ベースプレートに配置された第1接着剤と、第1接着剤上に配置され、導体ベースプレートと接着される半導体チップと、導体ベースプレート上において、半導体チップと導体ベースプレートとの接合面の外周に配置され、第1接着剤を被覆する第2接着剤とを備え、第1接着剤は、導電性金属成分を含有し、前記第2接着剤は、導電性金属成分を含有していない。

(もっと読む)

接続材料付き半導体素子およびその製造方法

【課題】はんだ接続時の接続不良を低減し、パワー半導体素子を歩留りよく接続することができる接続材料付き半導体素子およびその製造方法を提供する。

【解決手段】半導体材料1の表面に設けられた電極2となる金属層と、前記金属層の表面であって前記半導体材料の表面に接する面とは異なる面上に設けられた、前記金属層を被接続部材に接続させるための接続金属層5と、を備え、前記接続金属層5は、Al濃度が0mass%より大きく10mass%以下であるZn−Al合金、またはZnとAlとを積層させて形成された積層体からなるものである。

(もっと読む)

接合体

【課題】接合強度が高く、放熱特性および耐熱性にも優れる接合体を提供する。

【解決手段】本発明は、半導体素子30と、半導体素子30を実装する回路層20が形成された絶縁性を有するセラミックス基板10と、を備え、半導体素子30と回路層20は、アルミニウムを主成分とし、ゲルマニウム、マグネシウム、珪素、銅からなる群より選択される少なくも1種類を含有するアルミニウム系ろう材60により、真空中または不活性雰囲気中でろう付けすることにより接合されている。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】回路基板やリードフレームのステージなどの支持板上に半導体チップを実装する際に、半導体チップが移動や回転等の位置ずれを生じないようにする。

【解決手段】半導体装置の製造方法であって、支持板2の半導体チップ実装領域2A及び半導体チップ1の裏面の一方に、第1金属を含む層5及び第2金属を含む層6の一方を形成し、半導体チップ実装領域及び半導体チップの裏面の他方の、第1金属を含む層及び第2金属を含む層の一方が形成された領域の一部に相当する領域に、第1金属を含む層及び第2金属を含む層の他方を形成し、半導体チップ実装領域に半導体チップを位置合わせし、第1金属及び第2金属を含む合金を含む層9を形成して、半導体チップを半導体チップ実装領域に接合する。

(もっと読む)

半導体素子の接合構造体および半導体素子の接合構造体の製造方法

【課題】 半導体素子の使用時の250℃程度の発熱に対しても放熱性が優れ、また半導体素子と電極とを品質良く接合すること。

【解決手段】 半導体素子102と電極103との間に形成され、それらを接合する接合部204を備え、接合部204は、Al層105と、その両側に形成された各金属間化合物層109−1、109−2とを有し、接合部204は、箔状のAl105の外層に、NiまたはZnよりなる中間層106−1、106−2と、CuまたはNiまたはAgよりなる第1金属層107−1、107−2と、Snよりなる第2金属層108−1、108−2とをこの順で有する接合材料104を利用して形成される、半導体素子の接合構造体。

(もっと読む)

素子部品搭載装置

【課題】 素子部品の搭載を容易にする。

【解決手段】 素子部品が収納されたパレットから導電性接着剤が設けられた素子搭載部材ウェハに素子部品を搭載する素子部品搭載装置であって、パレットから移動された素子部品を仮置きするトレーと、パレットに収納された複数の素子部品を吸引する複数の吸着部を有し、吸着部で素子部品をトレーに仮置きし、仮置きした素子部品をトレーから素子搭載部材ウェハの所定の位置に搭載する吸引移動手段とを備え、トレーが素子部品を個別に仮置きさする複数の凹部を有し凹部の壁面が傾斜しつつ凹部の開口側に露出しており、吸引移動手段がトレーの凹部に素子部品を仮置きした場合に、素子部品が凹部の傾斜した壁面を滑り凹部の底面に位置したところで、再度、素子部品を吸引して素子搭載部材ウェハの搭載位置まで移動して吸引した素子部品を所定の位置に搭載することを特徴とする。

(もっと読む)

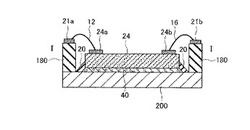

半導体装置

【課題】良好な信頼性を維持しつつ、レーザバーとサブマウントを面接合させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板18と、該基板の表面に形成されたエピタキシャル層20と、該エピタキシャル層の表面に形成された表面電極22と、該表面電極に形成されたエピタキシャル面めっき24と、該基板の裏面に形成された裏面電極26と、該裏面電極に形成された基板面めっき28と、を有するレーザバー12と、該エピタキシャル面めっき又は該基板面めっきにはんだにより固定されたサブマウント16と、を備える。該エピタキシャル面めっき24は該基板面めっき28よりも厚く形成され、該エピタキシャル面めっき又は該基板面めっきの全面が、該はんだ14により該サブマウントと面接合する。

(もっと読む)

半導体装置

【課題】半導体素子の温度勾配を低減するとともに、半導体装置における放熱性能を向上すること。

【解決手段】電気回路に実装されるIGBT(半導体素子)11と、電気回路100に形成されIGBT11との間で電気的に接続される回路パターン21と、IGBT11と回路パターン21との間に介在して両者を電気的に接続する接続層30と、を備える。接続層30は、IGBT11と回路パターン21とを機械的に接合するはんだ層32と、駆動時に温度が最大になるIGBT11の一部に臨んで設けられはんだ層32と比較して電気抵抗が高いダイオード31と、を有する。

(もっと読む)

半導体装置

【課題】半導体素子と基板との接合部に発生する気泡を低減させた半導体装置の製造方法を提供すること。

【解決手段】ダイマウント接合電極13を有するLEDチップ10をセラミック基板20に実装する実装工程を備えた半導体装置の製造方法において、前記実装工程は、前記セラミック基板上に、Au−Sn共晶はんだ粒子41を有するはんだペースト40を供給する工程と、前記はんだペースト上に、前記ダイマウント接合電極上にSn膜14が形成された前記LEDチップをマウントする工程と、前記Au−Sn共晶はんだ粒子、及び前記Sn膜を溶融させて、前記セラミック基板とLEDチップを接合する工程とを具備している。

(もっと読む)

接合構造体

【課題】接合材料の主成分であるBiは、延性が低いことから、パワー半導体素子とリードフレームとの間の接合部の接合材料に用い、ヒートサイクルによる繰り返し応力が加わると、モールド樹脂と接合部との界面で剥離が発生しやすくなる。

【解決手段】接合構造体200は、半導体素子101と、半導体素子101に対向して配置される電極103と、半導体素子101の裏面電極201に対向する側の表面のバリア層204と、半導体素子101と電極103とを接続するBiを主成分とする接合材料からなる接合部105とを有し、半導体素子101、バリア層204、電極103及び接合部105の外周をモールド樹脂206により封止されている接合構造体200であって、接合材料が有機物由来の官能基207を含有していることを特徴とする。

(もっと読む)

トランジスタ実装体及びその製造方法

【課題】チャネル抵抗を大幅に低減した電界効果トランジスタ実装体を実現できるようにする。

【解決手段】トランジスタ実装体の製造方法は、トランジスタ100を形成する工程(a)と、形成基板101を研磨する工程(b)と、形成基板101を研磨したトランジスタ100を保持基板200に固定する工程(c)とを備えている。工程(a)は、形成基板101の主面上に第1の半導体層及び該第1の半導体層よりもバンドギャップが大きい第2の半導体層を順次形成する。工程(b)は、形成基板101における主面と反対側の面を研磨する。工程(c)は、形成基板101の反りが小さくなる方向の応力を形成基板101に印加した状態でトランジスタ100を保持基板200の上に固定する。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップの中央部での半田の厚さを増すことなく、半導体チップ全面を容易にベースプレートにマウントできる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、ベースプレート1の所定位置及び該所定位置の近傍にそれぞれマウント用ロウ材2及び予備ロウ材3を供給する工程と、マウント用ロウ材2及び予備ロウ材3を溶融する工程と、所定位置のマウント用ロウ材2上に半導体チップ10を搭載する工程と、予備ロウ材3の少なくとも一部を、ベースプレート1上で半導体チップ10に向かって移動させて、マウント用ロウ材2と一体化させる工程と、を有する。

(もっと読む)

化合物半導体MMICにおける信頼性の改良

半導体パッケージ(M)が、第一の側面または上面(120)および第一の側面(120)とは反対の第二の側面または下面(背面)(104)を有する。熱生成領域(120)が半導体基板層(100)の第一の側面(120)に関連して形成される。ダイ接着部材(106)が半導体基板層(100)の第二の側面(104)に接して形成され、半導体基板層(100)の第二の側面(104)の全体よりも小さい範囲にわたって伸張する。ダイ接着部材(106)は半導体基板層(100)に関して熱生成領域(102)と反対側に一様に位置する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】装置のマザーボードへの実装時の高い信頼性および小型で良好な放熱性を兼ね備え、かつ半導体素子とダイパッドとの間に良好な導電性を得ることができ、半導体素子の裏面で電気的な接続が必要な製品にも適用させることができる半導体装置及びその製造方法を提供する。

【解決手段】樹脂基板1上のダイパッド2と、ダイパッド2に接着剤3にて固着された半導体素子4と、半導体素子4と電気的に接続された複数の電極端子6と、ダイパッド2と半導体素子4と電極端子6とを封止する樹脂封止体7と、電極端子6とビアを通じて各々電気的に接続された外部端子8とを備え、ダイパッド2の表面に酸化ケイ素(SiO2)18bが形成され、酸化ケイ素上に半導体素子4を接着剤3にて固着する。

(もっと読む)

半導体装置

【課題】一部の機能端子に対してワイヤボンディングを用いる必要がなく、配線接続本数を縮小することができ、サイズを縮小可能な半導体装置を提供する。

【解決手段】半導体チップ20の表面には、半導体集積回路が形成され、ボンディング用の第1の表面電極21と、裏面電極24と接続する第2の表面電極22が設けられている。半導体チップ20の第2の表面電極22と裏面電極24は、ビアホールに金属を充填した貫通ビア部23により電気的に接続されている。リードフレーム30のダイパッド部は、半導体チップ20を電気的に接続して固定する。半導体チップ20の第1の表面電極21とインナーリード部32をワイヤボンディングする。実装基板60とはアウターリード部33,34により接続する。

(もっと読む)

半導体素子の接合構造、及び半導体素子の接合方法。

【課題】半導体素子側面へのろう材の濡れ上がりを防止するとともに、半導体素子を高い位置精度で基台に接合することが可能な半導体素子の接合構造、及び半導体素子の接合方法を提供することを目的とする。

【解決手段】先ず第1接合部Aにより半導体素子に形成された脚状部18と基台とを高い位置精度で接合した後に、第2接合部Bにより十分な強度の接合を行うため、高い位置精度で半導体素子を基台に接合することができる。また、第4電極23のろう材層は脚状部18の間に位置するため、脚状部18が障壁となって溶融したろう材層が半導体素子側面への濡れ上がりを防止する。このため、ろう材の濡れ上がりによる半導体素子への悪影響も生じることはない。

(もっと読む)

半導体パワーモジュール

【課題】III族窒化物半導体パワートランジスタをパッケージに収納する構造を有する半導体パワーモジュールについて、ハンダにより基板上に固定されるIII族窒化物半導体パワートランジスタのクラック発生を抑制すること。

【解決手段】厚さ300μm以上のサファイア基板21上に成長されたIII族窒化物半導体からなるIII族窒化物半導体素子20と、III族窒化物半導体素子20が搭載されるヒートシンク11と、ヒートシンク11とIII族窒化物半導体素子20とを接合する融点300℃以上のハンダ13と備えることにより、III族窒化物半導体素子20のクラック発生は防止される。

(もっと読む)

Au−Sn合金はんだペーストを用いて素子の接合面全面を基板に接合する方法

【課題】特にAu−Sn合金はんだペーストを用いてLED(発光ダイオード)素子などの素子を基板に接合する方法を提供する。

【解決手段】素子1の接合面を上向きにしてその上にAu−Sn合金はんだペースト6を搭載または塗布し、この状態のまま非酸化性雰囲気中でリフロー処理してAu−Sn合金はんだペースト6を溶融し、素子1の接合面全面に拡がって溶融Au−Sn合金はんだ層を冷却し凝固して凝固Au−Sn合金はんだ層7を形成し、この凝固Au−Sn合金はんだ層7を有する素子1を反転させて、凝固Au−Sn合金はんだ層7が基板4に接するように素子1を基板4の上に載置し、この状態で非酸化性雰囲気中でリフロー処理することによりボイドのないAu−Sn合金はんだ接合部9を介して素子1を基板4に接合する。

(もっと読む)

Au−Sn合金はんだペーストを用いた基板と素子の接合方法

【課題】特にAu−Sn合金はんだペーストを用いてLED(発光ダイオード)素子などの素子を基板に接合する方法を提供する。

【解決手段】Au−Sn合金はんだペースト2を基板1に搭載または塗布し、前記基板1に搭載または塗布したAu−Sn合金はんだペースト2の表面に素子3の一部が接しかつ素子の一端が基板1に接するように素子3をAu−Sn合金はんだペースト2上に載置し、かかる状態でAu−Sn合金はんだペースト2を搭載または塗布しかつ素子3を載置した基板1を非酸化性雰囲気中でリフロー処理する。

(もっと読む)

窒化物半導体レーザ装置の製造方法

【課題】 マウント時にサブマウントと窒化物半導体レーザチップとの間からはみ出したハンダが窒化物半導体レーザチップの側面に這い上がるのを抑制する窒化物半導体レーザ装置の製造方法を提供する。

【解決手段】 チップ用コレット42が吸着した窒化物半導体レーザチップ20を、サブマウント15の窒化物半導体レーザチップ20を搭載する面に対して垂直に移動させる時のチップ搬送速度を、少なくとも窒化物半導体レーザチップ20とサブマウント15上のチップ接合用ハンダ17とが接触する瞬間に2000μm/秒以下とする。これにより、窒化物半導体レーザチップ20とサブマウント15との間からはみ出したチップ接合用ハンダ17が窒化物半導体レーザチップの側面に這い上がるのを抑制することができる。

(もっと読む)

1 - 20 / 22

[ Back to top ]