Fターム[5F048BA06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 多層基板(2層) (997) | 基板と直上の層が同型 (184)

Fターム[5F048BA06]に分類される特許

1 - 20 / 184

半導体装置の製造方法

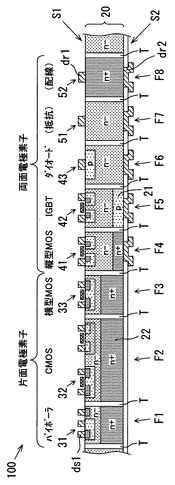

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

CMOS垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、CMOS垂直置換ゲート(VRG)トランジスタを提供する。

【解決手段】集積回路構造は平面に沿って形成された主表面を有する半導体領域及び表面中に形成された第1及び第2のソース/ドレインドープ領域を含む。絶縁トレンチが第1及び第2のソース/ドレイン領域間に形成される。第1のソース/ドレイン領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1のソース/ドレイン領域上に配置される。第4のドープ領域が第2のソース/ドレイン領域上に形成され、第2のソース/ドレイン領域とは相対する伝導形をもち、チャネル領域を形成する。第5及び第6のソース/ドレイン領域が、それぞれ第3及び第4のドープ領域上に形成される。

(もっと読む)

半導体装置

【課題】注入元素子から被注入素子への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】第1および第2の主表面を有する半導体基板SUB内にはエピタキシャル層EPPと、n型不純物領域NRを含む注入元素子と、注入元素子と間隔を隔てて形成された被注入素子と、注入元素子と被注入素子との間の領域の少なくとも一部に形成され、注入元素子と被注入素子とを結ぶ方向に対して交差する方向に延在する接地電位が印加されたn型領域GNNおよびp型領域GPPを有するバリア層BRとを備える。さらに半導体基板SUB内でエピタキシャル層EPPに接するように形成されたフローティングp型裏面領域FLPを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】スイッチング用のパワーMOSFETと、そのパワーMOSFETよりも小面積でかつそのパワーMOSFETに流れる電流を検知するためのセンスMOSFETとが1つの半導体チップCPH内に形成され、この半導体チップCPHはチップ搭載部上に導電性の接合材を介して搭載され、樹脂封止されている。半導体チップCPHの主面において、センスMOSFETが形成されたセンスMOS領域RG2は、センスMOSのソース用のパッドPDHS4よりも内側にある。また、半導体チップCPHの主面において、センスMOS領域RG2は、パワーMOSFETが形成された領域に囲まれている。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子装置

【課題】縦型トランジスタのTDDB耐性を向上させ、かつ、閾値電圧がばらつくことも抑制する。

【解決手段】ゲート電極120の上端は、半導体基板100の表面よりも下に位置している。絶縁層340は、ゲート電極120上及びその周囲に位置する半導体基板100上に形成されている。絶縁層340は、第1絶縁膜342及び低酸素透過性絶縁膜344を有している。第1絶縁膜342は、例えばNSG膜であり、低酸素透過性絶縁膜344は、例えばSiN膜である。さらに、低酸素透過性絶縁膜344上には、第2絶縁膜346が形成されている。第2絶縁膜346は、例えばBPSG膜である。絶縁層340を形成した後、酸化雰囲気で処理することにより、縦型MOSトランジスタ20のTDDB耐性が向上する。また、絶縁層340が低酸素透過性絶縁膜344を有することにより、縦型MOSトランジスタ20の閾値電圧がばらつくことを抑制できる。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 基板表面にパターンニングされたポリシリコン層(ゲート配線や保護ダイオード)が閉ループ状の場合、特にウエハの周辺部分に配置されるチップでは、層間絶縁膜形成時にSOG膜のスピンコートでチップコーナー部分などにおいてSOG液の液だまりが生じ、層間絶縁膜の膜厚が不均一となり、厚膜化した箇所ではコンタクトホールの形成不良が発生する問題があった。

【解決手段】 ゲート配線と保護ダイオードが連続した閉ループ状とならないように、ゲート配線のコーナー部と、ゲート配線および保護ダイオードの隣接部分に開放部を設ける。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

半導体装置、半導体パッケージ、および半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】N型基板10と、N型基板10の一面側に設けられたP型ウェル40と、P型ウェル40に設けられたP型高濃度不純物領域42と、P型ウェル40に設けられたN型のソース・ドレイン領域を有するMOSトランジスタ20と、N型基板10の一面側に設けられ、かつ一方がP型高濃度不純物領域42と電気的に接続し、他方が接地されているソース・ドレイン領域を有するMOSトランジスタ30と、を備える。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 MOSFETの素子領域の外側の周辺領域において、ドレイン‐ソース間にpn接合ダイオードを形成し、逆起電力による電流の経路を確保してアバランシェ破壊を防止している。しかし、チップサイズの小型化や素子領域の面積の拡大を目的として周辺領域の面積を縮小した場合、pn接合ダイオードの配置領域が縮小し、電流経路が少なくなるためアバランシェ破壊に弱くなる問題があった。

【解決手段】 ゲート引き出し配線8で区画される周辺ゲート領域25において、p+型不純物領域24とソース電極17を接続する第2コンタクト部10の単位面積当たりの合計面積を、素子領域20のソース領域15とソース電極17とを接続する第1コンタクト部9の単位面積当たりの合計面積より大きくする。周辺領域の面積を縮小した場合であっても逆起電力による電流の経路を確保できアバランシェ耐量の劣化を防げる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

シンクロナス整流器或いは電圧クランプ用の3端子パワーMOSFETスイッチ

【課題】パワー変換器に於けるシンクロナス整流器として適するMOSFETスイッチを提供する。

【解決手段】互いに接続されソース及びボディが、ドレンよりはより正の側に高い電圧にバイアスされたN−チャネルパワーMOSFETを製造する。ゲートはスイッチ(1184)により制御され、ゲートを、ソース及び当該MOSFETのチャネルを完全にオンにするのに十分な電圧(VCP)のいずれか一方に選択的に接続する。ゲートがソースに接続されたとき、デバイスは、比較的低い電圧でオンし、従来のPN接合よりは低い導通抵抗を有する「擬似ショットキー」ダイオードとして機能する。ゲートが、前記した正の電圧に接続されたとき、MOSFETのチャネルは完全にオンとなる。このMOSFETスイッチは、電力損及び“break-before-make”時間に於ける蓄積電荷を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】DRAMの微細化及び高集積化により、プロセス低温化が進み、400〜500℃熱処理による基板内の酸素ドナー化による電子発生量が多くなってきた。そのため、基板深くに形成されるウェル同士の分離耐圧が厳しくなり、デバイス劣化を引き起こしてしまう。

【解決手段】P型半導体基板11の表面から0.2〜1μmの範囲の深さに2E+17atom/cm3以上のピーク濃度を有するNウェル層12の下方に、P型半導体基板11中に発生するキャリア電子濃度より高濃度のP型不純物を含有する空乏層拡大防止層17を有する半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

半導体チップ、半導体装置、及び半導体チップの製造方法

【課題】2次電池パックの保護回路を更に小型化すること。

【解決手段】本発明に係る半導体チップは、双方向スイッチを構成する2個のパワートランジスタと、抵抗素子とを備える。2個のパワートランジスタのドレイン同士は接続されている。抵抗素子の一端は、2個のパワートランジスタのうち一方のソース電極と電気的に接続され、その他端は、第1外部パッドと電気的に接続されている。それら2個のパワートランジスタと抵抗素子とは、同一の半導体チップ上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲート電極を備えるトレンチゲート構成のパワーMISFETにおいて、MISFETの性能向上を図りながら、ゲート絶縁膜の静電破壊を防止することができる技術を提供する。

【解決手段】ダミーゲート電極9aを備えるトレンチゲート構成のパワーMISFETと保護ダイオードとを同一の半導体基板1上に形成する。そして、保護ダイオードをソース電極24とゲート配線25の間に設ける。このような半導体装置の製造方法において、ダミーゲート電極9a用のポリシリコン膜と保護ダイオード用のポリシリコン膜を同時に形成する。また、パワーMISFETのソース領域と保護ダイオードのn+型半導体領域15を同一工程で形成する。

(もっと読む)

半導体装置

【課題】トレンチゲートをゲート電極で完全に埋め込むトレンチゲート型MOSFETにおいて、パフォーマンスに優れた半導体回路装置を提供する。

【解決手段】第1の導電型のウェル層4内に形成された第2の導電型のウェル層5が、ゲート電極材料9で埋設された格子状のトレンチ溝7で囲まれたトレンチゲート型MOSFETであって、トレンチ溝7の側面と第2の導電型のウェル層5との間に形成される第1の絶縁膜8は、トレンチ溝7の側面と前記第1の導電型のウェル層4との間に形成される第2の絶縁膜14よりも薄くしてある。

(もっと読む)

トレンチゲートMISデバイスの構造及び製造方法

【課題】より単純に製造でき、かつ平坦なトポロジを得ることができ、更にトレンチの上部曲がり部における降伏電圧の問題が解消されたトレンチゲートMISデバイスを提供すること。

【解決手段】トランジスタセルを含む活性領域と、トランジスタセルを含まないゲート金属領域と、ゲート金属層とを含み、半導体チップの表面のパターンに、活性領域からゲート金属領域に至るトレンチが形成されており、このトレンチが絶縁材料の層で裏打ちされた壁部を有し、導電性ゲート材料がトレンチ内に設けられており、導電性ゲート材料の上面が半導体チップの上面より下側に位置し、非導電層が活性領域及びゲート金属領域の上に位置し、ゲート金属領域におけるトレンチの一部の上側の非導電層に開口が形成されており、ゲート金属がトレンチ内の接触領域のゲート材料と接触するように、開口が前記ゲート金属で満たされているトレンチゲートMISデバイス。

(もっと読む)

CMOSイメージセンサの製造方法

【課題】スペーサ形成用絶縁膜のドライエッチングによるフォトダイオード領域の損傷を抑え、駆動時の暗電流特性を改善可能なCMOSイメージセンサの製造方法を提供すること。

【解決手段】フィールド絶縁膜32及びゲート電極33aを形成した基板30上のエピタキシャル層31上面にイオン注入用酸化膜35を形成し、フォトダイオード領域37、38を形成し、フォトダイオード領域形成マスク36を除去した後、窒化膜39、酸化膜40の順で積層したスペーサ形成用絶縁膜を形成し、酸化膜40をドライエッチングして、ゲート電極33aの両側壁の窒化膜39上に酸化膜スペーサ41を形成した後、ドライエッチングによって露出された窒化膜39を、ウェットエッチングにより除去し、フォトダイオード領域37、38と反対側のゲート電極33a片側のエピタキシャル層31表層部にフローティング拡散領域43を形成する。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

1 - 20 / 184

[ Back to top ]