Fターム[5F048BB15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB15]の下位に属するFターム

絶縁膜厚が異なるもの (781)

絶縁材料が異なるもの (340)

注入量、注入物質が異なるもの (323)

Fターム[5F048BB15]に分類される特許

321 - 334 / 334

半導体製造装置の製造方法

【課題】

簡易な方法で同一半導体基板上に、ゲート絶縁膜の膜厚、又は閾値電圧が異なる3種類のMOSトランジスタを製造する方法を提供すること。

【解決手段】

本発明の半導体装置の製造方法は、同一半導体基板上に、所定厚さの第1ゲート絶縁膜を有する第1のMOSトランジスタと、第1ゲート絶縁膜よりも薄い第2ゲート絶縁膜を共通に有する第2及び第3のMOSトランジスタとを備え、第3のMOSトランジスタは、その閾値電圧が第2のMOSトランジスタより低い半導体装置の製造方法において、第1及び第3のMOSトランジスタの閾値電圧調整のために第1のイオン注入を行う工程と、第2のMOSトランジスタの閾値電圧調整のために第1のイオン注入とは注入条件の異なる第2のイオン注入を行う工程を備えることを特徴とする。

(もっと読む)

相補型金属酸化膜半導体集積回路のNMOS及びPMOSトランジスタを用いた異なる複数のゲート誘電体の使用方法

【解決手段】相補型金属酸化膜半導体集積回路が、異なる複数のゲート誘電体を有するNMOS及びPMOSトランジスタで形成される。複数の異なるゲート誘電体は、例えば、サブトラクティブ法によって形成される。複数のゲート誘電体は、いくつかの例において、材料、厚さ、あるいは形成手法が異なる。  (もっと読む)

(もっと読む)

半導体装置

【課題】ゲート電極の空乏化を抑制しながら、ゲート電極を形成する際の製造プロセスを簡略化することが可能な半導体装置を提供する。

【解決手段】この半導体装置は、一対のn型のソース/ドレイン領域6aと、チャネル領域5a上にゲート絶縁膜7aを介して形成されたゲート電極8aと、一対のp型のソース/ドレイン領域6bと、チャネル領域5b上にゲート絶縁膜7bを介して形成されたゲート電極8bとを備えている。そして、ゲート電極8aは、ゲート絶縁膜7a上に形成されたTaN層9aと、TaN層9a上に形成されたポリシリコン層10aとを含み、ゲート電極8bは、ゲート絶縁膜7b上に形成されたTaN層9bと、TaN層9b上に形成されたポリシリコン層10bとを含み、TaN層9aおよび9bは、同じ層からなる。

(もっと読む)

半導体装置及びその製造方法

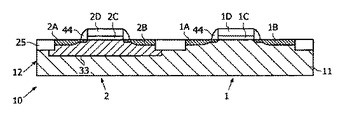

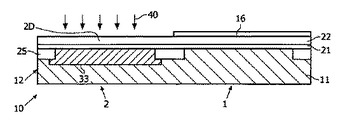

本発明は、それぞれ金属及びさらなる元素の両方を含む化合物の第1及び第2の導電材料を有するゲート領域(1D,2D)を持つNMOST1及びPMOST2を備えるCMOS装置(10)に関する。本発明によれば第1及び第2の導電材料は共に前記金属としてモリブデンとタングステンとを含む群から選択される金属を含む化合物を有し、前記第1の導電材料は前記さらなる元素として酸素を有し、前記第2の導電材料は前記さらなる元素としてカルコゲナイドを有する。本発明はこのような装置の魅力的な製造方法を提供する。  (もっと読む)

(もっと読む)

相補型金属−酸化膜−半導体電界効果トランジスタ構造

相補型金属−酸化膜−半導体電界効果トランジスタ構造(100)はイオン注入領域(126,128)を2つの相補型素子の内の一方のみに含む。トランジスタ構造(100)は通常、化合物半導体基板(102)と、そしてエピタキシャル層構造(104)と、を含み、エピタキシャル層構造は、エピタキシャル層構造の導電型を決定する一つ以上のドナー層を含む。イオン注入領域は、これらの相補型素子の内の一方に位置するエピタキシャル層構造(104)の導電型を「反転する」または「逆にする」ように作用する。例示として実施形態では、p型アクセプターをドープしたイオン注入領域がpチャネル素子(122)において使用され、nチャネル素子(120)はイオン注入されない状態のままである。  (もっと読む)

(もっと読む)

半導体装置及びかかる半導体装置の製造方法

本発明は、金属及び更なる元素の両方を含有する化合物を含むゲート領域(1D、2D)を有するNMOST1及びPMOST2を備えるCMOSデバイス(10)に関する。本発明によれば、第1及び第2導電材料はいずれも、モリブデン及びタングステンを含むグループから選択される金属を前記金属として含む化合物を備えると共に、炭素、酸素、カルコゲナイドを含むグループから選択される元素を前記更なる元素として含んでいる。第1及び第2導電材料はいずれも、モリブデン及び炭素または酸素から成る化合物を含むことが好ましい。また本発明は、かかるデバイスを製造する魅力的な方法も提供する。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】 MOSトランジスターのきめ細かなマルチVth化により、複雑な信号処理が可能であるアナログ半導体集積回路装置の製造方法を提供する。

【問題解決手段】 MOSトランジスターのソ−スとゲート電極にオーバラップするように選択的に窒化膜を配する製造方法により、かつそのチャネル幅方向の窒化膜のゲート電極へのオーバラップ量をパターン設計値で可変することによりきめ細かなマルチVth化を実現する。

(もっと読む)

デュアル・ゲートCMOSの製造

本発明は、CMOS素子を製造する方法に関し、その方法は、絶縁材料層(102)をその中に有する半導体基板(101)を準備するステップと、絶縁層(102)の上に第1の材料層(106)を形成するステップとを備え、第1の材料層(106)の厚さが、第1の能動素子を担持する第1の領域(103)では、第2の能動素子を担持する第2の領域(104)より薄い。次いで、第2の材料層(107)が、第1の材料層(106)上に形成され、次いで、その構造体に熱処理が行われて、第1と第2の材料が合金化される。第1の領域上の両層部分は全体が合金化されるが、第2の領域上の両層部分はそうはならず、その結果、第1の材料層(106)の一部分(109)が残留する。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】 MOSトランジスターのきめ細かなマルチVth化により、複雑な信号処理が可能であるアナログ半導体集積回路装置を提供する。

【解決手段】 MOSトランジスターのソ−スとゲート電極にオーバラップするように窒化膜を配し、かつそのチャネル幅方向の窒化膜のゲート電極へのオーバラップ量をパターン設計値で可変することによりきめ細かなマルチVth化を実現する。

(もっと読む)

半導体装置及びその製造方法

【課題】 SOI部の素子に対して閾値電圧の制御及び短チャネル効果の改善を比較的簡単に行うことのできる素子構造及びその製造方法を提供する。

【解決手段】 半導体装置10は、支持基板13と、前記支持基板上に設けられ、5−10nmの厚さを有する埋め込み絶縁膜14と、前記埋め込み絶縁膜上に設けられたシリコン層15と、前記シリコン層に設けられたMOSFET11と、前記MOSFET11の下部にあって前記支持基板13中に局所的に設けられたトリプルウエル領域17、18とからなる。

(もっと読む)

トランジスタの製造プロセス評価方法及び、トランジスタの製造プロセス評価素子

【課題】 トランジスタの電気的特性に異常がある場合に、その不良解析に要する時間を短縮することができるようにしたトランジスタの製造プロセス評価方法及び、トランジスタの製造プロセス評価素子を提供する。

【解決手段】 ウエーハWに形成されたICチップ100に含まれる代表的なMOSトランジスタ1の製造プロセスを評価するための評価素子10であって、MOSトランジスタ1と同一の製造プロセスによってウエーハWに形成された通常のMOSトランジスタ10aと、この製造プロセスからチャネルドープ工程だけを除いた不完全製造プロセスによって当該ウエーハWに形成されたネイティブトランジスタ10bと、を備えたものである。通常のMOSトランジスタ10aの閾値等に異常があった場合に、その値とネイティブトランジスタ10bの閾値等とを比較することで、その原因がチャネルドープ工程に有るか否かを容易に判断することができる。

(もっと読む)

低電圧CMOSトランジスタを用いた高電圧スイッチ

本発明は、スイッチのスイッチ素子が実現される或る技術の定格電圧を越える線ごとの入力電圧振幅の可能な電気スイッチに関する。例えば、スイッチ素子は、CMOS技術においてnMOS及びpMOSトランジスタの相補結合された対とすることができる。2つの分圧器は、フローティング電源電圧を電源電圧からスイッチ素子へ供給するために用いられる。このフローティング電源電圧は、常に、入力電圧から独立して電源電圧内にあり、これにより、フローティング電源電圧をスイッチ素子の臨界絶縁破壊電圧内に維持しつつ、スイッチの入力端子において線ごとの電圧を許容する。本発明によるスイッチは、標準的なCMOS技術により形成可能であり、少なくとも50MHzまでのスイッチング周波数で機能するように実現することが可能である。本発明によるスイッチ素子は、カスケード接続されることができ、これにより、1つのスイッチのときよりも遥かに高い最大差動入出力電圧を得ることができる。

(もっと読む)

(もっと読む)

調整可能なゲート電極の仕事関数を備えたデュアルメタルのCMOSトランジスタおよびその製造方法

デュアルメタルのCMOSの配列とその形成方法は、基板(10)と、その基板(10)上に形成された複数のNMOSデバイス(44)およびPMOSデバイス(46)を提供する。複数のNMOSデバイス(44)およびPMOSデバイス(46)の各々は、ゲート電極を有する。各NMOSゲート電極は、基板(10)上に第1シリサイド領域(50)を含み、その第1シリサイド領域(50)上に第1金属領域(48)を含む。NMOSゲート電極の第1シリサイド領域(50)は、シリコンの伝導帯に近い仕事関数を有する第1シリサイド(50)からなる。PMOSゲート電極の各々は、基板上に第2シリサイド領域(54)を含み、その第2シリサイド領域(54)上に第2金属領域(52)を含む。PMOSゲート電極の第2シリサイド領域(54)は、シリコンの価電子帯に近い仕事関数を有する第2シリサイド(54)からなる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

321 - 334 / 334

[ Back to top ]