Fターム[5F048BB15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB15]の下位に属するFターム

絶縁膜厚が異なるもの (781)

絶縁材料が異なるもの (340)

注入量、注入物質が異なるもの (323)

Fターム[5F048BB15]に分類される特許

201 - 220 / 334

集積回路および集積回路の形成方法

【課題】同一半導体基板内に、高いしきい値電圧、または低いしきい値電圧を有する複数のトランジスタを有用な集積回路、およびその製造方法を提供すること。

【解決手段】第1ゲート電極を有する第1タイプのトランジスタと、第2ゲート電極181を有する第2タイプのトランジスタ183とを含む。上記第1ゲート電極は、半導体基板内に設定された第1ゲート用溝内に形成され、上記第2ゲート電極は、上記半導体基板内に設定された第2ゲート用溝180内に形成されている。上記第1ゲート電極は、2つの互いに隣り合う各第1分離用トレンチ間のスペースを完全に充填している。上記第2ゲート電極は、2つの互いに隣り合う各第2分離用トレンチ間のスペースを部分的に充填している。上記第2ゲート電極と、上記互いに隣り合う各第2分離用トレンチとのそれぞれの間に、各基板部分がそれぞれ配置されている。

(もっと読む)

半導体集積回路およびその製造方法

【課題】高い製造歩留を可能とすると伴に、小さなオーバーヘッドでMOSトランジスタのしきい値電圧のバラツキを補償すること。

【解決手段】半導体集積回路Chipは、アクティブモードの間に入力信号Inを処理するCMOS回路Coreと、制御スイッチCnt_SWと、制御メモリCnt_MMとを含む。制御スイッチCnt_SWは、CMOS回路のPMOSQp1のNウェルN_WellとNMOSQn1のPウェルP_WellとにPMOS基板バイアス電圧VbpとNMOS基板バイアス電圧Vbnとをそれぞれ供給する。制御メモリCnt_MMは、前記アクティブモードの間に前記制御スイッチから前記CMOS回路の前記PMOSの前記Nウェルと前記NMOSの前記Pウェルとに前記PMOS基板バイアス電圧と前記NMOS基板バイアス電圧とをそれぞれ供給するか否かを示す制御情報Cnt_Sgを格納する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜上にpMOS電極材料として金属電極を形成する際に金属膜中からゲート絶縁膜へ拡散する炭素成分を抑制し、固定電荷要因を下げることができる半導体装置及びその製造方法を提供することである。

【解決手段】半導体装置の製造方法は、半導体基板100上にゲート絶縁膜101を形成する工程と、ゲート絶縁膜上に薄いシリコン層102を形成する工程と、この薄いシリコン層上にゲート絶縁膜界面での仕事関数が所定範囲内の値となる金属膜103を形成する工程と、を備えたものである。

(もっと読む)

半導体装置の製造方法

【課題】p型MOSFETとn型MOSFETとの間で異なる所望のしきい値を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上にHf、 Zrの少なくとも1つと、Si、O、Nを含むゲート絶縁膜を形成し、第1、第2のゲート電極層を形成し、第1のゲート電極層上および第2のゲート電極層上に、第1の金属含有層を形成し、第2の金属含有層を形成し、保護膜を形成し、保護膜を選択的に除去し、残存する保護膜をマスクとして、第1の金属含有層および第2の金属含有層を選択的に除去し、第1の金属含有層および第2の金属含有層が選択的に除去された第2のゲート電極層上に、第3の金属含有層を成膜し、加熱処理により、第1のゲート電極層を合金化するとともに、第2のゲート電極層を合金化し、異なる組成のゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】FUSIゲートCMOSトランジスタにおいて、不純物層上シリサイド膜の高抵抗化及び浅接合破壊を共に抑制する。

【解決手段】半導体装置の製造方法は、基板50上に、シリコンからなるゲート電極7及び基板50におけるゲート電極7の両側に位置する不純物層10を備えるトランジスタを形成する工程と、少なくとも不純物層10を覆う第1の金属膜14を形成する工程と、第1の金属膜14を覆い且つゲート電極7に開口を有する絶縁膜16を形成する工程と、ゲート電極7上を含む絶縁膜16上に第2の金属膜17を形成する工程と、第1の金属膜14及び第2の金属膜17に対して熱処理を行なうことにより、不純物層10の上部と、ゲート電極7とを同時にシリサイド化する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MOSFET及びp型MOSFETの閾値電圧を安定化でき、且つ信頼性の劣化を防ぐことのできるフルシリサイドゲート電極を有する半導体装置を実現できるようにする。

【解決手段】半導体基板11と、半導体基板11に形成されたn型トランジスタ形成領域13Aに形成され、フルシリサイドゲート電極24を有するn型MOSFETと、半導体基板に形成されたp型トランジスタ形成領域13Bに形成され、フルシリサイドゲート電極24と同一の膜厚を有するフルシリサイドゲート電極23を有するp型MOSFETとを備え、フルシリサイドゲート電極23及び24は、それぞれ金属シリサイドからなることを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法及び半導体装置

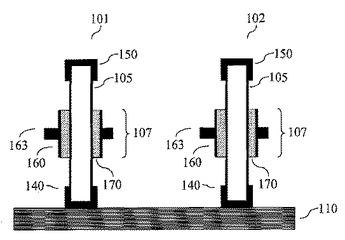

【課題】用途に応じてゲート幅を設計変更することが可能なフィン型FETを含む半導体装置及びその製造方法を実現する。

【解決手段】半導体基板11上面に、第1高さを有するフィン12aと、第1高さよりも低い第2高さを有するフィン12bとを形成する工程と、フィン12a及び12bそれぞれの上面及び側面にシリコン酸化膜を形成する工程と、シリコン酸化膜上に導電性を有するポリシリコン膜を形成する工程と、シリコン酸化膜及びポリシリコン膜をパターニングすることで、フィン12a及び12bそれぞれの上面から側面にかけてゲート絶縁膜15及びゲート電極16を形成する工程と、フィン12a及び12bそれぞれにおけるゲート電極16下を挟む2つの領域に一対の拡散領域14を形成する工程とを備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】 ダマシンゲート技術等を用いてゲート電極が作製される半導体装置において、半導体装置の微細化等を可能にする。

【解決手段】 N型MISトランジスタ及びP型MISトランジスタそれぞれのゲート電極が半導体基板に形成された凹部内にゲート絶縁膜を介して形成されている半導体装置であって、N型MISトランジスタ及びP型MISトランジスタの一方のゲート電極は第1の金属含有膜F1及び第1の金属含有膜上の第2の金属含有膜F2の積層構造によって構成され、N型MISトランジスタ及びP型MISトランジスタの他方のゲート電極は第3の金属含有膜F3及び第3の金属含有膜上の第2の金属含有膜F2の積層構造によって構成されている。

(もっと読む)

半導体装置

【課題】同期整流方式の電源装置において、ドライブ損失の増加を招くことなく、MOSFETのセルフターンオンを抑制し、電源効率を向上する。

【解決手段】本発明の電源装置は、同期整流回路を構成する整流用MOSFET(2)のゲートサイズは転流用MOSFET(3)のゲートサイズより小さくされる。更に、転流用MOSFETのしきい値が整流用MOSFETのしきい値より高くする。例えば転流用MOSFETのしきい値を整流用MOSFETより、0.5V 以上高くし、整流用MOSFETのしきい値を1.5V 以下、転流用MOSFETのしきい値は2.0V 以上とする。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル幅やチャンネル長が異なるにも係らずほぼ同じ閾値電圧が要求される複数種類のトランジスタを有する半導体装置において、工程数を削減する。

【解決手段】半導体装置は、少なくともチャネル幅が互いに異なる複数のトランジスタを有しており、これらトランジスタの閾値電圧が、これらトランジスタへの実質的に等しいチャネルドーズ量と、これらトランジスタのゲート絶縁膜への所定金属の付着および/またはこれらトランジスタのゲート電極材料による仕事関数制御(すなわち、これらトランジスタのチャネル領域に対するゲート構造(ゲート絶縁膜および/またはゲート電極)に基づく仕事関数制御)との両方を用いて、ほぼ同じに設定されている。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】金属ゲート電極のエッチング条件が、閾値電極を構成する材料が異なっても同一となる金属ゲート電極MOSFETを提供すること。

【解決手段】ゲート酸化膜に接して形成された第1の金属層と第1の金属層の上に形成された第1の低抵抗層とからなる第1のゲート電極を有するnチャネルMOSFETとゲート酸化膜に接して形成された第2の金属層と第2の金属層の上に形成された第2の低抵抗層とからなる第2のゲート電極を有するpチャネルMOSFETとを有する半導体集積回路において、第1の金属層と第2の金属層が異なった仕事関数を有する金属によって構成され、第1の低抵抗層と第2の低抵抗層とが同一の材料からなる多結晶で構成され、第1の金属層と第1の低抵抗層の間に第1の中間層を有し、且つ第2の金属層と第2の低抵抗層の間に第2の中間層を有し、第1の中間層および第2の中間層が組成、粒径、結晶構造、及び配向方向が同一の導電性多結晶膜からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート長の異なるMISFET間のしきい値のばらつきを抑制した半導体装置及びその製造方法を提供すること。

【解決手段】 半導体基板100の第一及び第二領域112、113上にゲート絶縁膜103及びダミー層111を形成し、ダミー層111を加工して第一のダミーゲート114と第一のダミーゲート114よりゲート長の長い第二のダミーゲート115を形成。第一及び第二のダミーゲート114、115を利用してダミー絶縁層116を形成し、第一及び第二のダミーゲート114、115を除去してダミー絶縁層116に第一と第二の開口部117、118を形成し、第一の開口部117全体及び第二の開口部118の一部に第一の導電膜107を形成し、第二の開口部118に第一の導電膜107とは異なる仕事関数の第二の導電膜108を、第一領域112上に第一のMISFET105、第二領域113上に第二のMISFET106とを形成する。

(もっと読む)

ナノスケール電界効果トランジスタの構体

本発明は、ラップゲート構造を有する縦型ナノワイヤトランジスタに関する。縦型ナノワイヤトランジスタの閾値電圧は、ナノワイヤの直径、ナノワイヤの不純物添加レベル、ナノワイヤへのヘテロ構造のセグメントの導入、ナノワイヤを取り囲むシェル構造における不純物添加、ゲートスタックの仕事関数の適応、歪み調整、誘電体材料の制御又はナノワイヤ材料の選択により制御される。異なる閾値電圧を有するトランジスタが同一の基板上に形成されることにより、直接結合フィールドロジックと同様に、閾値電圧の変化を利用する最先端回路の設計が可能になる。  (もっと読む)

(もっと読む)

トライステートバッファ回路

【課題】LSIの高集積化に適したトライステートバッファ回路を提供する。

【解決手段】半導体基板100に第1のFin106および第2のFin108を形成されている。第1のFinの一方の側面にpFET1、pFET3、nFET1を設け、それぞれのMISFETに対向するように他方の側面にpFET4、nFET4およびnFET3が設けられている。第2のFinの両側面にpFET2およびnFET2を設けられている。以上のように3次元構造を有するMISFETによって要部を構成したトライステートバッファ回路を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】仕事関数の値及び閾値が安定したフルシリサイドゲート電極を有する半導体装置を実現できるようにする。

【解決手段】本発明に係る半導体装置は、半導体基板の上に形成されたゲート絶縁膜15aと、ゲート絶縁膜の上に形成されたゲート電極23とを備えている。ゲート電極23は、層状の複数の結晶粒が積層されてなる金属シリサイド膜を有するフルシリサイドゲート電極である。

(もっと読む)

半導体装置及びその製造方法

【課題】同一基板上において誘電率の異なる複数種類のゲート絶縁膜を必要性に応じて使い分けた半導体装置の構造、及び当該構造を実現する簡便な製造方法を提供する。

【解決手段】基板1の活性領域1a上に高誘電率ゲート絶縁膜4を介してゲート電極7Aが形成されている。基板1の活性領域1b上にゲート酸化膜6を介してゲート電極7Bが形成されている。ゲート電極7A及び7Bのそれぞれの側面に同一構造の絶縁性サイドウォールスペーサ8A及び8Bが形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】電極の接触抵抗、電極自身の抵抗の低減によって高性能化した電界効果トランジスタを含む半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板200に形成されたチャネル領域106と、ゲート絶縁膜101を介して形成されたゲート電極と、チャネル領域106の両側に形成されたソース電極およびドレイン電極を具備するn型電界効果トランジスタを含み、ソース電極およびドレイン電極が第1の金属のシリサイド110aで形成され、半導体基板200と第1の金属のシリサイド110aとの界面に、第2の金属120aを含有する界面層が形成され、第2の金属120aの仕事関数が第1の金属のシリサイド110aの仕事関数よりも小さく、かつ、第2の金属120aのシリサイドの仕事関数が第1の金属のシリサイド110aの仕事関数よりも小さいことを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置の製造方法

【課題】金属窒化膜からなるゲート電極を有するMOSFETにおいて、ゲート電極の窒素組成を容易に制御することを可能とする半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板11の上に絶縁膜15を形成する工程(a)と、絶縁膜15の上に窒素を含まない材料かなる膜である第1の導電膜16を形成する工程(b)と、第1の導電膜16の上に窒素を含む材料からなる膜である第2の導電膜18を形成する工程(c)と、第2の導電膜18及び第1の導電膜16をパターニングしてゲート電極を形成すると共に、絶縁膜15をパターニングしてゲート絶縁膜を形成する工程(d)とを備えている。

(もっと読む)

半導体記憶装置

【課題】微細化に伴いトランジスタの特性ばらつきが増加するのを抑制することが可能な半導体記憶装置を提供する。

【解決手段】本発明のメモリセルMCにおいては、アクセストランジスタNQ3とドライバトランジスタNQ1とのチャネル幅WdrおよびWacの関係をアクセストランジスタのチャネル幅Wacをドライバトランジスタのチャネル幅Wdrよりも大きくする。すなわち、アクセストランジスタNQ3は、最小設計寸法で設計されたドライバトランジスタNQ1よりもチャネル面積を増加させることができるためすなわちLWの面積を増加させることができるためアクセストランジスタNQ3の特性ばらつきの増加を抑制することが可能となる。

(もっと読む)

半導体装置

【課題】 ゲート電極を構成する材料とSOI層の仕事関数差によって閾値が定まるアキュムレーション型MOSトランジスタでは、閾値を低下させ、小型化することが困難であった。

【解決手段】 SOI層を支持するシリコン基板の不純物濃度を調整すると共に、SOI層と接するシリコン基板表面に形成された埋込絶縁層の厚さを制御することにより、閾値を調整できるトランジスタが得られる。

(もっと読む)

201 - 220 / 334

[ Back to top ]