Fターム[5F048BB15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB15]の下位に属するFターム

絶縁膜厚が異なるもの (781)

絶縁材料が異なるもの (340)

注入量、注入物質が異なるもの (323)

Fターム[5F048BB15]に分類される特許

141 - 160 / 334

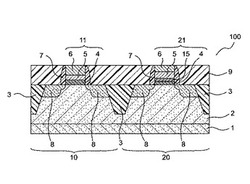

半導体装置およびその製造方法

【課題】同一導電型のチャネル領域を有し、かつ閾値電圧の異なる複数の半導体素子を有する半導体装置を提供する。

【解決手段】閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置において、トランジスタのゲート電極は、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、更に、一方のトランジスタが、ゲート絶縁膜と金属層との間に、第2金属の酸化膜を含む。

(もっと読む)

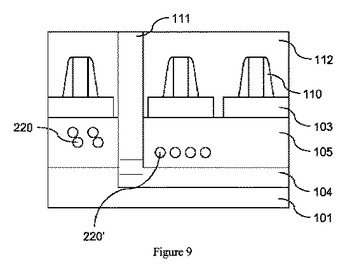

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】組成の安定したゲート電極を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板11に、ゲート長に加工された、ゲート絶縁膜21、シリコン材料膜23a、ストッパ膜25、及びシリコン材料膜23bを順に有する第1の積層膜を備えたpMOS領域1、離間して、ゲート長に加工された、ゲート絶縁膜21、シリコン材料膜23a、及びシリコン材料膜23bを順に有する第2の積層膜を備えたnMOS領域2を形成し、第1及び第2の積層膜の側壁にオフセット膜33、サイドウォール35の形成、及びソース・ドレイン領域15の形成を行い、pMOS領域1のシリコン材料膜23b及びストッパ膜25を除去し、シリコン材料膜23a上、及びnMOS領域2のシリコン材料膜23b上にNiを堆積し、pMOS領域1にNi3Siを形成し、nMOS領域2にNiSi2を形成する。

(もっと読む)

半導体装置

【課題】集積回路を構成するMISFETの処理速度の向上とリーク電流の低減を両立させ、かつ、半導体装置の小型化を達成することができる技術を提供する。

【解決手段】単体のMISFETから構成される回路素子に代えて、しきい値電圧の異なる複数のMISFETからなる同一ノードトランジスタから回路素子を構成する。例えば、図2に示すように、nチャネル型MISFET1aとnチャネル型MISFET1bを並列接続しかつ、それぞれのゲート電極Gを電気的に接続する。このとき、例えば、nチャネル型MISFET1aを高VthMISFETから構成し、nチャネル型MISFET1bを低VthMISFETから構成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】NMOSとPMOSとの境界を明確化して更なる微細化を可能とし、NMOSとPMOSとの閾値電圧を共に実用レベルの低い値に設定できる半導体装置を提供する。

【解決手段】 この半導体装置1は、ゲート電極Gnが金属シリサイド層111/La含有層105/ゲート絶縁膜103の積層構造のNMOSトランジスタと、ゲート電極Gpが前記金属シリサイド層111と同一組成の金属シリサイド層111/前記La含有層105と同一組成のLa含有層105/メタル層104/ゲート絶縁膜103の積層構造のPMOSトランジスタとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】パストランジスタにおける出力信号の低下を抑制し得る半導体装置及びその製造方法を提供する。

【解決手段】第1のゲート電極30aを有する第1のトランジスタ20と、第2のゲート電極30bを有する第2のトランジスタ14と、第3のゲート電極30cを有し第2のトランジスタより閾値電圧が低い第3のトランジスタ16とを有し、第1のゲート電極の中心部の直下における第1導電型の不純物のピーク濃度は、第2のゲート電極の中心部の直下における第1導電型の不純物のピーク濃度より低く、且つ、第3のゲート電極の中心部の直下における第1導電型の不純物のピーク濃度以下であり、第1のゲート電極の縁部の直下における第1導電型の不純物のピーク濃度は、第2のゲート電極の縁部の直下における第1導電型の不純物のピーク濃度より高く、且つ、第3のゲート電極の縁部の直下における第1導電型の不純物のピーク濃度より高い。

(もっと読む)

半導体回路

【課題】高速のスイッチング特性と小サブスレッショルド電流特性とが両立可能なMOS−FETで構成される半導体回路を提供する。

【解決手段】MOS−FETQ1,Q2により構成される論理回路1を有した半導体回路において、MOS−FETQ1,Q2のバックゲートバイアス電圧Vcc,VSSとは異なる電圧Vpp,Vbbを供給する電圧供給手段15,13と、MOS−FETQ1,Q2のバックゲートバイアス電圧を、電圧Vcc,VSSと電圧Vcc,VSSとは異なる電圧Vpp,Vbbとに切り換えるスイッチング手段10とを備えた構成となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

半導体装置

【課題】サージ耐圧の高い半導体装置を提供する。

【解決手段】半導体層からなる複数のフィン15a〜15fと、複数のフィン15a〜15fの側面上にゲート絶縁膜16を介して設けられたゲートG1〜G6が、互いに電気的に接続されたゲート電極17と、ゲート電極17を挟むように、複数のフィン15a〜15f内に設けられたソースS1〜S6およびドレインD1〜D6と、複数のソースS1〜S6を電気的に接続するソース電極19と、複数のドレインD1〜D6を電気的に接続するドレイン電極18と、ゲート電極17に外部から電気を供給するためのゲートコンタクト20と、を備え、複数のフィン15a〜15fのうち、ゲートコンタクト20との距離が小さい方にあるフィン15a、15bの幅W1、W2が、ゲートコンタクト20との距離が大きい方にあるフィン15c〜15fの幅W3〜W6よりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】pMOSFETとnMOSFETとの間で異なる所望のしきい値を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】第1のゲート電極層上および第2のゲート電極層上に、第1の金属含有層9を形成し、この第1の金属含有層上方に感光性有機膜を含む膜10を形成し、第1のゲート電極層上方に位置する感光性有機膜を含む膜を選択的に除去することにより、第1の金属含有層のうち第1のゲート電極層上方に位置する部分を露出させ、感光性有機膜を含む膜上および第1の金属含有層上に第2の金属含有層19を形成し、加熱処理により、第1の金属含有層および第2の金属含有層に含有された金属と第2のゲート電極層とを反応させて、第2のゲート電極層を合金化するとともに、加熱処理により、第1の金属含有層に含有された金属と第2のゲート電極層とを反応させて、第2のゲート電極層を合金化する。

(もっと読む)

半導体装置

【課題】LSIのメモリマクロ部におけるMISFETの特性ばらつきを抑制する。

【解決手段】メモリセル部110を構成するMISFETのゲート長は、ロジック部200を構成するMISFETのゲート長より長く、センスアンプ部120を構成するMISFETのゲート長はメモリセル部110を構成するMISFETのゲート長より長くなるように調整されている。ここで、メモリセル部110を構成するMISFETは、ロジック部200を構成するMISFETのポケット注入領域7aに対して、不純物濃度が薄く、かつ広く分布したポケット注入領域7bを有している。一方、センスアンプ部120を構成するMISFETはポケット注入領域を有していない。

(もっと読む)

電源回路及び携帯機器

【課題】昇圧動作を行う電源回路においてバックゲートにかかる電圧の影響を抑制することである。

【解決手段】電源回路10において、入力電源の他方側端子GNDと一方側端子VCCとの間に直列に第1のスイッチングトランジスタ20、第2のスイッチングトランジスタ22を、入力電源の一方側端子VCCと昇圧出力端子OUTとの間に直列に第3のスイッチングトランジスタ24、第4のスイッチングトランジスタ26をそれぞれ設け、第1と第2のスイッチングトランジスタの接続点と、第3と第4のスイッチングトランジスタの接続点との間にシフト用コンデンサ40を設け、昇圧出力端子OUTに保持用コンデンサ42を接続する。第3のスイッチングトランジスタ24にはバックゲートにかかる電圧を切り換えるバックゲート切換回路30が設けられる。

(もっと読む)

相補型半導体装置及びその製造方法

【課題】 メタルゲート電極及び高誘電率ゲート絶縁膜を用いたn型MISトランジスタとp型MISトランジスタの双方において適正なしきい値電圧を得る。

【解決手段】 半導体基板30の表面部に形成された第1及び第2の半導体領域10,20と、第1の半導体領域10上に形成された、La及びAlを含む第1のゲート絶縁膜11及び第1のゲート電極12を有するn型MISトランジスタと、第2の半導体領域20上に形成された、La及びAlを含む第2のゲート絶縁膜21及び第2のゲート電極22を有するp型MISトランジスタと、を備えた相補型半導体装置であって、第2のゲート絶縁膜22における原子濃度比Al/Laが、第1のゲート絶縁膜11における原子濃度比Al/Laよりも大きい。

(もっと読む)

デュアル仕事関数半導体デバイスおよびその製造方法

【課題】CMOSを製造するにおいて、1つまたは2つの誘電体を有するデュアル金属ゲートを形成する場合の、本質的な製造プロセスの複雑さや費用が増加しない、製造が容易で信頼性のある、デュアル仕事関数を有する半導体デバイスの製造方法を提供する。

【解決手段】1つの金属電極から開始するデュアル仕事関数デバイスの簡単な製造方法およびそのデバイスを開示する。シングル金属シングル誘電体(SMSD)CMOS集積スキームが開示される。ゲート誘電体層1と誘電体キャップ層2および誘電体キャップ層2’’とを含む1つの誘電体スタックと、誘電体スタックを覆う1つの金属層とが、最初に形成され、金属−誘電体界面を形成する。誘電体スタックと金属層を形成した後、誘電体キャップ層2’’の、金属−誘電体界面に隣接する少なくとも一部が、仕事関数変調元素6を加えることにより選択的に変調される。

(もっと読む)

パターンデータ作成方法、設計レイアウト作成方法及びパターンデータ検証方法

【課題】パターンデータの補正処理及び検証処理を精度よく行うことができるとともに、マスクパターンの開発期間を短縮でき、さらには、半導体装置の製造歩留まりを向上できる。

【解決手段】本発明の例に関わるパターンデータ作成方法は、同一ゲート長を有する複数のMOSトランジスタを含む回路の設計パターンデータに基づき、前記複数のMOSトランジスタの種類を特定するステップ(ST2)と、前記複数のMOSトランジスタのゲートパターンに対し、前記MOSトランジスタの種類毎にそれぞれ異なる寸法スペックを設定するステップ(ST3)と、前記MOSトランジスタを形成するためのマスクパターンデータを用いたシミュレーションにより予測した前記MOSトランジスタのゲートパターンが、前記寸法スペックを満たすように、前記マスクパターンデータの修正を行うステップ(ST5)とを備える。

(もっと読む)

CMOS素子及びその製造方法

【課題】CMOS素子及びその製造方法を提供する。

【解決手段】基板上に形成されたエピ層と、エピ層のそれぞれ異なる領域上に形成された第1及び第2半導体層と、第1及び第2半導体層上にそれぞれ形成されたPMOS及びNMOSトランジスタと、を備えるCMOS素子である。

(もっと読む)

半導体デバイス、半導体デバイスを形成する方法、および集積回路

【課題】 相互に異なるしきい値電圧要件を有する複数のトランジスタを結合するための技法を提供する。

【解決手段】 一態様では、半導体デバイスは、第1および第2のnFET領域と第1および第2のpFET領域とを有する基板と、第1のnFET領域の上の基板上のロジックnFETと、第1のpFET領域の上の基板上のロジックpFETと、第2のnFET領域の上の基板上のSRAM nFETと、第2のpFET領域の上の基板上のSRAM pFETとを含み、そのそれぞれが、高K層の上の金属層を有するゲート・スタックを含む。ロジックnFETゲート・スタックは、高K層から金属層を分離するキャッピング層をさらに含み、キャッピング層は、ロジックpFET、SRAM nFET、およびSRAM pFETのうちの1つまたは複数のしきい値電圧に対してロジックnFETのしきい値電圧をシフトするようにさらに構成される。

(もっと読む)

特にアナログ適用例に適した電界効果トランジスタを具備する半導体アーキテクチャの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(100,100V,140,150,150V,160,170,170V,180,180V,190,210,210W,220,220U,220W,380,480,500,510,530又は540)は、そのソース/ドレインゾーンと隣接するボディ物質(108,268又は568)との間のPN接合に沿っての寄生容量を減少させるためにそのソース/ドレインゾーンの内の一つ(104,264又は564)下側にハイポアブラプトな垂直ドーパントプロフィルを有している。

【解決手段】 特に、該ボディ物質の導電型を画定する半導体ドーパントの濃度は、そのソース/ドレインゾーンから下方へ該ソース/ドレインゾーンよりも上部半導体表面下側に10倍を超えて一層深いものではない下側のボディ物質位置へ移る場合に、少なくとも10の係数だけ減少する。該ボディ物質は、好適には、他方のソース/ドレインゾーン(102,262又は562)に沿って位置されている一層高度にドープされたポケット部分(120,280又は580)を包含している。通常ドレインとして機能する最初に述べたソース/ドレインゾーン下側のハイポアブラプトな垂直ドーパントプロフィルと、通常ソースとして機能する2番目に述べたソース/ドレインゾーンに沿っての該ポケット部分との結合が、結果的に得られる非対称トランジスタを特に高速アナログ適用例に適したものとさせることを可能とさせる。

(もっと読む)

半導体装置の製造方法

【課題】p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】第1および第2領域13、14にゲート絶縁膜17を介して第1金属を含む第1金属膜18を形成する工程と、第1領域13における第1金属膜18を保護膜で被覆し、第2領域14における第1金属膜18を除去してゲート絶縁膜17を露出させる工程と、第1金属膜18上およびゲート絶縁膜17上に第1金属と異なる第2金属を含む第2金属膜19を形成する工程と、ゲート電極パターンを有するマスク材を用いて第2金属膜19を異方性エッチングし、第2領域14に第2ゲート電極を形成する工程と、第1金属膜18および第2金属膜19の露出部に酸化処理を施す工程と、第1領域13における第1金属膜18を異方性エッチングし、第1領域13に第1ゲート電極を形成する工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、各ゲートについて均一で十分なフル・シリサイド化を実現する、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極の表層部分及びソース/ドレイン領域16a,16bの表層部分がシリサイド化されている状態において、半導体基板1にフラッシュランプアニールを施す。この処理により、ソース/ドレイン領域16a,16bには(NiPt)2Si層19bが形成された状態が保持されて、ゲート電極のみが選択的にフル・シリサイド化され、フル・シリサイドゲート電極21が形成される。

(もっと読む)

141 - 160 / 334

[ Back to top ]