Fターム[5F048BB15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB15]の下位に属するFターム

絶縁膜厚が異なるもの (781)

絶縁材料が異なるもの (340)

注入量、注入物質が異なるもの (323)

Fターム[5F048BB15]に分類される特許

101 - 120 / 334

半導体装置及びその製造方法

【課題】半導体基板上に分布して形成された複数のDMOSトランジスタが破壊されることなく動作可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に分布して形成された3つ以上のDMOSトランジスタのうちの最内位置のDMOSトランジスタのオンオフ閾値電圧は最外位置のDMOSトランジスタのオンオフ閾値電圧よりも大きくなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】ばらつきの少ない適切な閾値電圧がそれぞれ設定されたLogic領域およびSRAM領域のトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、第1の領域および第2の領域を有する半導体基板と、前記半導体基板上の前記第1の領域に形成された第1の高誘電率層を有する第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1のゲート電極と、を有する第1のトランジスタと、前記半導体基板上の前記第2の領域に形成された前記第1の高誘電率層よりも酸素欠損濃度の平均値が低い第2の高誘電率層を有する第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2のゲート電極と、を有し、前記第1のトランジスタと異なる閾値電圧を有する第2のトランジスタと、前記半導体基板上に形成され、前記第1のトランジスタと前記第2のトランジスタとを分離する、酸素原子を含む素子分離領域と、を有する。

(もっと読む)

半導体装置とその製造方法

【課題】本発明は、高性能でかつ閾値電圧の低い半導体装置とその製造方法を提供することを目的とする。

【解決手段】基板に形成され、NMOSトランジスタが形成されるNMOS形成領域とPMOSトランジスタが形成されるPMOS形成領域とを絶縁分離する素子分離領域と、該基板上に形成されたHigh−k材料からなるNMOSおよびPMOSのゲート絶縁膜と、該NMOSのゲート絶縁膜上に形成されたNMOSゲート電極と、該PMOSゲート絶縁膜上に形成された第1ニッケルシリサイド層と、該第1ニッケルシリサイド層上に形成され、該第1ニッケルシリサイド層よりも厚くかつ該第1ニッケルシリサイド層よりニッケル密度が大きい第2ニッケルシリサイド層と、を有するPMOSゲート電極と、該NMOSゲート電極および該PMOSゲート電極の側壁に形成されたサイドウォールスペーサとを備える。

(もっと読む)

半導体デバイスとその製造方法、および集積回路

【課題】 バンド端を制御されたVtオフセット・デバイスを提供する。

【解決手段】 バンド端を制御されたVtオフセット・デバイス、バンド端を制御されたVtオフセット・デバイスの設計構造体、及びその構造体の製造方法を開示する。構造体は、第1のバンド構造及び第1の型をもたらす第1の原子比の第1の化合物半導体のチャネルを有する第1のFETを含む。この構造体はさらに、第2のバンド構造及び第1の型をもたらす第2の原子比の第2の化合物半導体のチャネルを有する第2のFETを含む。第1の化合物半導体は第2の化合物半導体とは異なり、その結果、第1のFETは第2のバンド構造とは異なる第1のバンド構造を有し、第2のFETの閾値電圧とは異なる閾値電圧を生じる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】低閾値電圧動作が可能な電界効果トランジスタを提供する。

【解決手段】n型半導体基板2と、半導体基板に離間して形成されたソースおよびドレイン領域12a、12bと、ソース領域とドレイン領域との間の半導体基板上に形成され、Hf、Zr、Tiから選ばれた少なくとも1つの物質と酸素を含む第1絶縁膜4と、第1絶縁膜上に形成され、シリコンと酸素を含む第2絶縁膜8と、第2絶縁膜上に形成されたゲート電極10と、を備え、V、Cr、Te、P、As、S、Seの群から選ばれた少なくとも一つの第1物質と、窒素とが第1絶縁膜と第2絶縁膜との界面を含む界面領域7に含まれ、第1物質の面密度が界面領域内の第2絶縁膜側において第1ピークを有し、窒素の面密度が界面領域内に第2ピークを有し、第2ピークの位置が、第1ピークの位置よりも半導体基板側にある。

(もっと読む)

半導体装置

【課題】複数のしきい値電圧をもつソース・ドレインが対称構造であるMOSトランジスタを同一基板上に搭載するとき、各MOSトランジスタのソース・ドレインの接続入れ替えに対して電気的に対称な特性を提供することにある。

【解決手段】しきい値電圧の大きいMOSトランジスタ9にはハロー拡散領域4を設け、しきい値電圧の小さいMOSトランジスタ16からはハローインプラを除く。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜形成工程のような大きな熱負荷を避けて、チャネルの最上面の不純物濃度を薄くした、深さ方向のドーピング・プロファイルを実現し、オン電流が向上する半導体装置の製造方法を提供することである。

【解決手段】 ゲート電極形成後にゲート電極をマスクにして角度10度以下でチャネル不純物をイオン注入し、この後、チャネル不純物の活性化を、基板表面から所定の深さのチャネル不純物濃度がゲート長方向に一定になるように、RTAを用いたアニールで行う、さらに、その後のエクステンション/ハロー注入、深いS/D注入の後の活性化を、拡散レスアニールで行う。

(もっと読む)

半導体装置の製造方法

【課題】複数の半導体素子における界面特性及び信頼性の劣化を抑制する。

【解決手段】半導体装置の製造方法は、第1半導体素子を有する第1領域と前記第1半導体素子と異なる第2半導体素子を有する第2領域とを備えた半導体装置の製造方法であって、前記第1領域及び前記第2領域における半導体基板10表面にシリコンゲルマニウム膜11を形成する工程と、前記第1領域及び前記第2領域における前記シリコンゲルマニウム膜表面を窒化処理する工程と、前記第1領域及び前記第2領域における窒化処理された前記シリコンゲルマニウム膜上にシリコンと酸素とを主成分とする第1絶縁膜13を形成する工程と、前記第2領域における前記第1絶縁膜を除去する工程と、前記第1領域における前記第1絶縁膜上及び前記第2領域における窒化処理された前記シリコンゲルマニウム膜上に金属と酸素とを主成分とする第2絶縁膜15を形成する工程と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、しきい値電圧のばらつきが大きいトランジスタのしきい値電圧を調整してしきい値電圧のばらつきを低減することを可能にする。

【解決手段】基板11と絶縁層12とシリコン層13が積層されてなるSOI基板10の該シリコン層13の表面側にトランジスタ20を形成する工程と、SOI基板10上に、トランジスタ20を被覆する第1絶縁膜30と、トランジスタ20に電気的に接続される配線部40とを形成する工程と、配線部40を通じてトランジスタ20のしきい値電圧を測定する工程と、第1絶縁膜30表面に第2絶縁膜を介して支持基板を形成する工程と、SOI基板10の裏面側の基板11と絶縁層12の少なくとも一部を除去する工程と、測定されたしきい値電圧に基づいてトランジスタ20のしきい値電圧を調整する工程を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】低い閾値電圧を有するFETおよび高い閾値電圧を有するFETのいずれも高性能な特性を有する半導体装置を提供する。

【解決手段】半導体装置100は、FET102と、FET102よりも高い閾値電圧を持つFET104を同一半導体基板上に備える。FET102は、ゲート絶縁膜114とゲート電極126を備える。FET104は、ゲート絶縁膜114とゲート電極121を備える。FET102のゲート電極126、FET104のゲート絶縁膜114、ゲート電極121はHf、Zr、Al、La、Pr、Y、Ta、Wからなる群から選択される少なくとも一つの金属を含む。FET104のゲート絶縁膜114とゲート電極121との界面における前記金属の濃度は、FET102のゲート絶縁膜114とゲート電極126との界面における前記金属の濃度よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応でき、High−kゲート絶縁膜を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、p型層103上に設けられた第1のゲート絶縁膜115、TiNからなる第1のゲート電極116と、及び不純物を含む半導体からなる第1の上部ゲート電極117を有するNチャネル型MOSトランジスタ106と、n型層102上に設けられた第2のゲート絶縁膜109、TiN結晶からなり、(111)配向/(200)配向が1.5以上となるTiN層を少なくとも一部に含む第2のゲート電極110、及び不純物を含む半導体からなる第2の上部ゲート電極111を有するPチャネル型MOSトランジスタ105とを備えている。

(もっと読む)

電圧変換回路および半導体装置

【課題】より低い電源電圧で動作させる場合の安定性を確保する。

【解決手段】電源Vbatの電圧を昇圧するためにオンオフ動作を繰り返すNMOSトランジスタNM1、NM2と、NM1をオンオフ駆動する駆動回路11と、NM2をオンオフ駆動する駆動回路12と、昇圧された電圧を平滑し平滑電圧が所定の値を超えたか否かを検知するコンパレータCMP2と、電源投入後に駆動回路11を活性化し、平滑電圧が所定の値を超えたことをコンパレータCMP2が検知した場合に駆動回路11を非活性化し駆動回路12を活性化する。NM1は、NM2よりも閾値電圧を低くなるよう構成され、ソースを接地し、ゲートに駆動回路11からのオンオフ駆動信号が供給される。ソースをNM1のドレインに接続し、ゲートに電源Vbatが供給され、ドレインをNM2のドレイン(ノードP)に接続するNMOSトランジスタNM3を備える。

(もっと読む)

固体撮像装置とその製造方法、及び電子機器

【課題】CMOS固体撮像装置における電荷読み出しトランジスタのゲート電極を縦型構成として画素サイズの微細化を可能にしつつ、各トランジスタにおけるチャネル領域の電位コントロールを確実ならしめる。

【解決手段】基板20と、基板20内に埋め込まれたフォトダイオードPD1,PD2と、フォトダイオードPD1,PD2の信号電荷を読み出す為に基板の深さ方向に埋め込まれて形成された、電荷読み出しトランジスタTr1の縦型のゲート電極26と、縦型の読み出しゲート電極26とは異なる電極材料で形成された、他のトランジスタTr2,Tr3の平面型のゲート電極31,33とを有する。

(もっと読む)

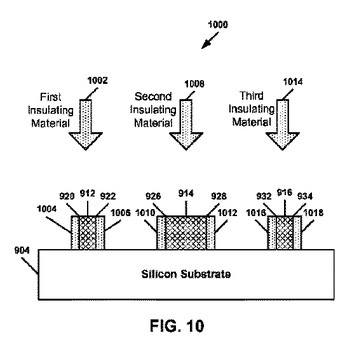

フィン電界効果トランジスタ(フィンFET)デバイスの製造方法

フィン電界効果トランジスタ(フィンFET)を用いた半導体の製造方法が開示される。特定の実施形態の方法は、第一の幅によって離隔された第一の側壁及び第二の側壁を有する第一のダミー構造体をシリコン基板上に堆積させるステップを含む。また、本方法は、第一のダミー構造体を堆積させるのと同時に第二のダミー構造体をシリコン基板上に堆積させるステップも含む。第二のダミー構造体は、第二の幅によって離隔された第三の側壁及び第四の側壁を有する。第二の幅は第一の幅よりも実質的に大きい。第一のダミー構造体を用いて略第一の幅によって離隔された第一の対のフィンを形成する。第二のダミー構造体を用いて略第二の幅によって離隔された第二の対のフィンを形成する。  (もっと読む)

(もっと読む)

複数のトランジスタゲートの形成方法、および少なくとも二つの異なる仕事関数を有する複数のトランジスタゲートの形成方法

少なくとも二つの異なる仕事関数を有する複数のトランジスタゲートを形成する方法は、異なる幅を有する基板上に第一および第二のトランジスタゲートを形成するステップを含み、第一の幅は第二の幅よりも狭い。材料は、第一および第二のゲート上を含む基板上に堆積される。エッチングチャンバー内で、材料は、第一および第二のゲートの双方の上からエッチングされ、第一のゲートの導電性材料を露出し、第二のゲート上に支持された材料の厚さを減少させ、材料によって被覆された第二のゲートをそのまま残す。エッチング後に、エッチングチャンバー内のそのままの位置で、基板は少なくとも300℃の基板温度で金属を含むプラズマに対して暴露され、第二のゲートの仕事関数と比較して、第一のゲートの仕事関数を改変するために、第一のゲートへと金属を拡散させる。  (もっと読む)

(もっと読む)

コンタクト形成方法、半導体装置の製造方法、および半導体装置

【課題】 低抵抗率のコンタクトを実現した半導体装置の製造方法を提供する。

【解決手段】半導体と接した第1の金属層を酸化防止用の第2の金属層で覆った状態で、第1の金属層のみをシリサイド化し、酸素混入のないシリサイド層を形成する。第1の金属層の材料として、半導体との仕事関数の差が所定の値となるような金属が用いられ、第2の金属層の材料として、アニール温度で第1の金属層と反応しない金属が用いられる。

(もっと読む)

固体撮像装置、その製造方法および撮像装置

【課題】本発明は、縦型トランジスタが形成される溝部内面にゲート絶縁膜を介して形成した薄膜を実効的なゲート電極とすることで、同一基板上に平面CMOSFETと縦型トランジスタを混載することを可能にする。

【解決手段】半導体基板11に、光電変換部51を備えた画素部12と周辺回路部13を有し、画素部12は、光電変換部51から信号電荷を読み出す縦型トランジスタ21と、この縦型トランジスタ21で読み出した信号電荷を処理する平面型トランジスタ22を有し、縦型トランジスタ21は、半導体基板11に形成した溝部31と、その内面に形成したゲート絶縁膜32と、溝部31内およびその周囲の半導体基板11上のゲート絶縁膜32上に形成した導電層35と、ゲート絶縁膜32と導電層35を介して溝部31内を埋め込む埋め込み層36と、埋め込み層36上に導電層35に接続した電極層37を有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲートラストプロセスで作製するトランジスタにおいて、活性領域と素子分離領域の高さばらつきのためゲートのポリシリコンを抜くことができないことにより、ゲートの抵抗にばらつきが生じるのを防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、第1のゲート部30及び第2のゲート部31の上面が共に露出するように、酸化膜16、PMD19、及び第1のゲート部30又は第2のゲート部31の一部を研磨除去する工程、露出された部分より、ポリシリコン12を抜く工程、第1のゲート部30及び第2のゲート部31を覆うメタルを形成する工程を備える。また、第1のゲート部30及び第2のゲート部31の上面が共に露出するようにメタルを研磨除去し、第1のゲート部30と第2のゲート部31で厚みの異なるメタルを残す工程を備えて構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】SRAMにおいてNMOS及びPMOSトランジスタのバランスを確保して、PMOSトランジスタの閾値電圧を高くできる半導体装置及びその製造方法を提供する。

【解決手段】メモリ領域において、基板の第1半導体領域(12,13)の第1チャネル形成領域上に第1ゲート絶縁膜(20,21)を介して第1ゲート電極が形成され、第1半導体領域に第1ソースドレイン領域(16,17)が形成されて第1トランジスタが形成され、ロジック領域において、基板の第2半導体領域(14,15)の第2チャネル形成領域上に第2ゲート絶縁膜(22,23)を介して第2ゲート電極が形成され、第2半導体領域に第2ソースドレイン領域(18,19)が形成されて第2トランジスタが形成され、第1ゲート電極の第1ゲート絶縁膜に接する部分が金属(40,41)からなり、第2ゲート電極の第2ゲート絶縁膜に接する部分が半導体(26,27)からなる。

(もっと読む)

101 - 120 / 334

[ Back to top ]