Fターム[5F048BB15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB15]の下位に属するFターム

絶縁膜厚が異なるもの (781)

絶縁材料が異なるもの (340)

注入量、注入物質が異なるもの (323)

Fターム[5F048BB15]に分類される特許

21 - 40 / 334

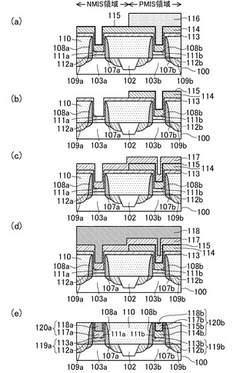

半導体装置及びその製造方法

【課題】さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現する。

【解決手段】ゲート電極120bは、第1の仕事関数を有する第1の金属含有膜114bと、第1の金属含有膜114b上に形成されており且つ第2の仕事関数を有する第2の金属含有膜117bとを含む。ゲート電極120aは、第1の金属含有膜114を含まないと共に第2の金属含有膜117aを含む。ゲート電極120bにおける第1の金属含有膜114bと第2の金属含有膜117bとの間に拡散防止層115bが形成されている。

(もっと読む)

半導体集積回路のトランジスタ素子

【課題】簡易な構成であり且つトランジスタ毎にしきい値電圧が異なる半導体集積回路のトランジスタ素子の提供。

【解決手段】ソース領域16A,16D、ドレイン領域16B,16Cおよびチャネル領域を備えた支持基板(Si基板2)上に、ゲート電極10とゲート電極10を覆う中間膜18とを備える第1および第2のトランジスタ構造を、少なくとも有し、前記第1のトランジスタ構造におけるゲート電極10とチャネル領域とが重なる領域には、中間膜18上に、第1のトランジスタ構造のしきい値電圧に変動を及ぼす範囲でゲート電極10とチャネル領域とが重なる領域の大部分を覆うよう支持基板(Si基板2)に応力を印加する応力膜22を有し、前記第2のトランジスタ構造におけるゲート電極10とチャネル領域とが重なる領域には、中間膜18上に、支持基板(Si基板2)に応力を印加する応力膜22を有さない半導体集積回路のトランジスタ素子。

(もっと読む)

ターンオン防止付き複合半導体デバイス

【課題】ターンオン防止付き複合半導体デバイスを提供する。

【解決手段】本明細書は、ターンオン防止制御を有する複合III-窒化物半導体デバイスの種々の実現を開示する。1つの好適な実現では、ノーマリオフ複合半導体デバイスが、ノーマリオンIII-窒化物パワートランジスタ、及びこのノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイスを具えて、ノーマリオフ複合半導体デバイスを形成する。このLVデバイスは、ノイズを伴う環境内で、ノイズ電流が、ノーマリオンIII-窒化物パワートランジスタのチャネルを通って流れることを防止することによって、ノーマリオフ複合半導体デバイスに、ターンオン防止制御を与えるように構成されている。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体装置および基準電圧生成回路

【課題】所望の温度特性を有することによって回路規模を小さくできるMOSトランジスタを提供する。

【解決手段】ゲート電極はP型半導体層及びN型半導体層からなるので、P型半導体層とN型半導体層との接合面に、空乏層13が生じる。温度が変化すると、空乏層13の領域の面積が変化し、P型半導体層11及びN型半導体層12の領域の面積もそれぞれ変化することで、MOSトランジスタに所望の温度特性を与えられる。その結果、温度補正回路を簡単にする、あるいは不要にすることができる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

多動作電圧垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、多動作電圧のMOSFETを生じる形態を提供する。

【解決手段】一般に、集積回路構造は平面に沿って形成された主表面を有する半導体領域と、表面中に形成された第1及び第2の空間的に分離されたドープ領域を含む。第1の領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1の領域上に配置される。異なる伝導形をもち、チャネルを形成する第4のドープ領域が、第2の領域上に配置される。2つのトランジスタのそれぞれにゲート構造を形成するプロセスにより、2つのトランジスタ間で異なる厚さの酸化物層が形成される。各トランジスタは更に、それぞれ第3及び第4の領域上に配置され、第3及び第4の領域に対して相対する伝導形をもつ第5及び第6層を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】用途によって異なるしきい値電圧を有するトランジスタを有する半導体装置、及び工程数の増加を抑えた当該半導体装置を製造する方法を提供する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1のゲート絶縁膜110aと、第1のゲート絶縁膜110a上に形成された第1のゲート電極109aと、第1のゲート絶縁膜110aの側面上及び第1のゲート電極109aの側面上に形成された第1のサイドウォール絶縁膜140aとを有する第1導電型の第1のMISFET150を備えている。第1のサイドウォール絶縁膜140aの少なくとも一部には、第1のゲート絶縁膜110aに正または負の固定電荷を誘起するための元素が含まれている。

(もっと読む)

半導体回路

【課題】レイアウトの複雑化や面積増大を伴わずにオフリーク電流の抑制と高速化を両立した半導体回路の実現。

【解決手段】通常動作モードと、少なくとも一部の回路に供給する信号を固定して、少なくとも一部の回路の状態を固定する低消費電力モードと、を備え、少なくとも一部の回路20において、低消費電力モード時にオン状態になるトランジスタPT1,PT3,NT2,NT4の閾値電圧が、低消費電力モード時にオフ状態になるトランジスタPT2,PT4,NT1,NT3の閾値電圧より小さい。

(もっと読む)

半導体装置及び電子機器

【課題】薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】第1の半導体層に設けられた第1のゲート電極と、第2の半導体層に設けられた第2のゲート電極と、第1の半導体層と第2の半導体層に接して設けられた第1の絶縁層と、第1の絶縁層が設けられた第1の半導体層の一方の面の反対側に設けられた第2の絶縁層と、第1の絶縁層が設けられた第2の半導体層の一方の面の反対側に設けられた第2の絶縁層及び第3の絶縁層と、を有し、第1の半導体層には第2の絶縁層により応力が加わり、第2の半導体層には第2の絶縁層と第3の絶縁層により応力が加わることで、第1の半導体層及び第2の半導体層に加わる応力が異なる。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

半導体装置

【課題】 ゲート−ソース逆バイアス駆動の動作原理を定量化し、MOSTのしきい電圧と動作電圧の関係を明らかにすることにより、逆バイアス駆動の原理を活用した複数のMOSTの組み合わせを用いて、動作電圧1V以下の高速低電圧動作を可能にする。

【解決手段】 低VtのMOSTを含む回路のリーク電流を、MOSTのゲート(G)とソース(S)を逆バイアスする各種の駆動方式によって低減する。低VtのMOSTに各種のG−S逆バイアスを加えることにより、リーク電流の少ない1V以下の高速低電圧CMOS論理回路、あるいはメモリ回路が実現される。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

【課題】半導体デバイスを提供する。

【解決手段】理論的な金属:酸素化学量論比を有する高kゲート誘電体、前記高kゲート誘電体の上部に設置された、Mを遷移金属として、組成がMxAlyで表されるアルミナイドを含むNMOS金属ゲート電極、および前記高kゲート誘電体の上部に設置された、アルミナイドを含まないPMOS金属ゲート電極、を有するCMOS半導体デバイス。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の主面上の洗浄効果を低下させることなく、電界効果トランジスタのゲート電極の側面上に形成されたオフセットスペーサ膜の除去を抑制する。

【解決手段】ゲート電極部Gn,Gpを覆うように、半導体基板1の主面上に薬液に対するエッチング速度が互いに異なる第1OSS膜10および第2OSS膜12を順次形成した後、異方性エッチングにより、ゲート電極部Gn,Gpの側面上に位置する第2OSS膜12を残して、他の部分に位置する第2OSS膜12を除去する。そして、ゲート電極部Gn,Gpと、ゲート電極部Gn,Gpの側面上に位置する第1OSS膜10および第2OSS膜12と、をマスクにして、半導体基板1に不純物をイオン注入した後、半導体基板1を薬液により洗浄して、露出している第1OSS膜10を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜にhigh−k膜を使用したMIS構造の半導体装置において、互いに異なる仕事関数を有する複数の同一導電型トランジスタを設けることを可能にする。

【解決手段】同じ導電型の第1のMISトランジスタ及び第2のMISトランジスタが同じ半導体基板50上に設けられている。第1のMISトランジスタにおけるゲート絶縁膜52aの界面層2Aの厚さは、第2のMISトランジスタにおけるゲート絶縁膜52bの界面層2bの厚さよりも厚い。

(もっと読む)

半導体装置、及びその製造方法

【課題】高品質な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成される半導体領域、半導体領域内に形成され、互いに分離されているソース領域及びドレイン領域、半導体領域内に形成され、ソース領域及びドレイン領域を分離するチャネル領域、チャネル領域上に形成され、1×1019atoms/cm2よりも大きいピーク濃度で、Si、O、またはNとは異なる少なくとも一つの要素を有する界面酸化層、及び界面酸化層上に形成され、実質的に界面酸化層に隣接する深さでhigh―k/界面酸化層接合面を有するhigh―k絶縁層を有するMOS(metal-oxide-semiconductor)トランジスタを備え、少なくとも一つの要素のピーク濃度の少なくとも一つの深さは、実質的にhigh―k/界面酸化層接合面よりも下に位置する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

半導体装置の製造方法

【課題】前工程においてトランジスタごとに不純物の種類や量を変えることによる、製造コストや製造時間の増大を抑制する。

【解決手段】本発明による半導体装置の製造方法は、第1の閾値電圧及び第1のドレイン・ソース間電流を呈するようなデバイスパラメータをもって設計された第1のトランジスタを含む半導体回路を形成する半導体回路形成工程(ステップS11)と、第1のトランジスタにストレス電圧を印加して第1の閾値電圧とは異なる第2の閾値電圧及び前記第1のドレイン・ソース間電流とは異なる第2のドレイン・ソース間電流の少なくとも一方を第1のトランジスタが呈するようにする特性制御工程(ステップS14)と、第1のトランジスタが第2の閾値電圧及び第2のドレイン・ソース間電流の少なくとも一方を呈する状態で出荷する出荷工程(ステップS16)とを備える。

(もっと読む)

21 - 40 / 334

[ Back to top ]