Fターム[5F048BB15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB15]の下位に属するFターム

絶縁膜厚が異なるもの (781)

絶縁材料が異なるもの (340)

注入量、注入物質が異なるもの (323)

Fターム[5F048BB15]に分類される特許

161 - 180 / 334

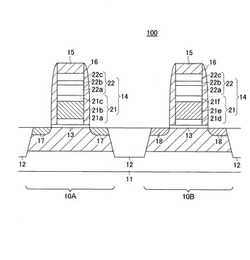

半導体装置及びその製造方法

【課題】ホウ素(B)のゲート絶縁膜の突き抜けや金属シリサイド膜による不純物の吸収によって生じるポリシリコン膜中の不純物の空乏化を防止する。

【解決手段】半導体装置100は、ゲート絶縁膜13と、ゲート絶縁膜13上に形成されたゲート電極14とを備える。ゲート電極14は、ドープドポリシリコン膜21a、21b、21cと、金属シリサイド膜22aとを備えている。ドープドポリシリコン膜21a、21cは、第1の不純物を含んでおり、ドープドポリシリコン膜21bは、反対の導電型を有する第2の不純物を含んでいる。これにより、ポリシリコン中の不純物の拡散工程やその後の熱負荷工程において、第2のドープドポリシリコン膜中の不純物の過度な拡散が抑制され、金属シリサイド膜が不純物を吸収することによるポリシリコン膜中の不純物の空乏化が防止される。

(もっと読む)

半導体装置

【課題】工程の増加や占有面積の増加もなくオフリーク電流を小さく抑えた、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】内部回路領域に内部素子のN型MOSトランジスタ701と内部素子のP型MOSトランジスタ711を有し、外部接続端子と前記内部回路領域との間にESD保護用のN型MOSトランジスタ721を有する半導体装置において、ESD保護用のN型MOSトランジスタ721のゲート電極はP型のポリシリコンにより形成した。

(もっと読む)

半導体素子及びその製造方法

【課題】高い電圧で作動が可能なトランジスター、中間電圧で作動が可能なトランジスター及び低い電圧で作動が可能なトランジスターが集積された半導体チップを提供する。

【解決手段】半導体素子は、第1導電型不純物が注入された第1領域111を含む半導体基板110と、第1領域111上に第1活性領域及AR1び第2活性領域AR2を定義して配置される素子分離膜120と、第1活性領域AR1に第1間隔で相互離隔されて、第2導電型不純物が注入されて形成される第1LDD領域151と、及び第2活性領域AR2に前記第1間隔より狭い第2間隔で相互離隔されて、第2導電型不純物が注入されて形成される第2LDD領域152を含む。

(もっと読む)

種類および膜厚の異なるゲート絶縁層を有するCMOSデバイス、ならびにその形成方法

high−k金属ゲート構造(310N,310B,310P)によって従来のゲート電極構造(310)を置換するためのプロセスシーケンスにおいて、例えば、選択性の高いエッチングステップ(322,325,327,331)を使用することによって、追加のマスク形成ステップの数を少なく保つことができ、これにより、従来のCMOS技術との高い互換性を保つことができる。更に、ここに開示の技術は、前工程(front-end)のプロセス技術および後工程(back-end)のプロセス技術との互換性を実現し、これにより、トランジスタレベルのほか、コンタクトレベルでも実績のある歪み発生機構を組み込むことが可能となる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体膜をゲート絶縁膜として備え、且つN型MISFETとP型MISFETとでゲート電極構造の異なる半導体装置においてゲート絶縁膜の信頼性を安定して確保できるようにする。

【解決手段】P型MISFET領域1及びN型MISFET領域2を含む半導体基板10上にHfSiO膜13及びTiN膜16を順次形成した後、N型MISFET領域2に位置する部分のTiN膜16を選択的に除去する。その後、N型MISFET領域2に位置する部分のHfSiO膜13を窒化してHfSiON改質層19を形成した後、ポリシリコン膜20を形成する。

(もっと読む)

デュアル仕事関数半導体デバイス

【課題】CMOSがFUSIゲートを含む場合、異なるシリサイド相を有する第1および第2の制御電極が形成され、ゲート形成後の熱工程等により各ゲートの異なったシリサイド相中のNi等の金属はゲート電極間を拡散しない半導体装置を提供する。

【解決手段】第1の制御電極17の金属半導体化合物から、第2の制御電極18の金属半導体化合物に、金属が拡散するのを防止するブロック領域23を形成する。ブロック領域23は、第1および第2の制御電極17、18の間の境界面に形成され、金属半導体化合物がそれから形成される金属中での溶解度より、金属半導体化合物中での溶解度が低いドーパント元素を注入することにより形成する。これにより、金属拡散が防止され、第1および第2の制御電極17、18の金属半導体化合物の構成が、例えば更なるデバイスの処理中の熱工程中に、実質的に変化せずに保たれる。

(もっと読む)

信号処理装置、フィルタ装置、信号処理方法、およびフィルタ方法

【課題】信号処理装置、フィルタ装置、信号処理方法、およびフィルタ方法を提供すること。

【解決手段】静電容量が可変である可変キャパシタと、前記入力信号を前記可変キャパシタにサンプリングさせるサンプリングモードと、前記入力信号をサンプリングして得られた電荷を前記可変キャパシタに保持させる保持モードと、前記可変キャパシタに保持されている電荷を出力させる出力モードと、を含む回路モードを切り替えるスイッチング部とを備え、前記可変キャパシタは、前記サンプリングモード時に前記入力信号が入力される入力端子と、前記入力端子との間に絶縁層が設けられており、前記出力モード時に前記可変キャパシタの静電容量を前記サンプリングモード時の静電容量より減少させる第1の制御信号が入力され、前記保持モード時に所定の基準電圧を有する第2の制御信号が入力される制御端子と、を備える信号処理装置。

(もっと読む)

集積型半導体装置およびMIS型半導体装置

【課題】短ゲート長のMIS型半導体装置やこれを含む集積型半導体装置において、MIS型半導体装置のしきい値電圧を制御する構造を提供する。

【解決手段】複数のMIS型半導体装置を含む集積型半導体装置が、半導体基板と、半導体基板に形成されたソース領域およびドレイン領域と、ソース領域とドレイン領域に挟まれ、ノンドープの半導体層を表面に含むチャネル領域と、チャネル領域上に形成された絶縁膜と、絶縁膜の上に形成されたゲート電極とを、それぞれが含む第1および第2のMIS型半導体装置を含み、第1のMIS型半導体装置に含まれる半導体層の膜厚と、第2のMIS型半導体装置に含まれる半導体層の膜厚とが互いに異なる。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧が低く、トランジスタ間でしきい値電圧のばらつきの無いトランジスタを含む半導体装置を提供する。

【解決手段】nチャネルトランジスタとpチャネルトランジスタとを含む相補型の半導体装置において、nチャネルトランジスタは、ゲート絶縁膜と、ゲート絶縁膜上に形成された、第1金属(M1)とシリコン(Si)からなる第1化合物層を含む第1メタルゲート電極を備え、pチャネルトランジスタは、ゲート絶縁膜と、ゲート絶縁膜上に形成された、第1金属(M1)と第2金属(M2)とシリコン(Si)からなる第2化合物層を含む第2メタルゲート電極を備え、第1化合物層の組成が、組成式:M1Six(1≦x)で表され、第2化合物層の組成が、組成式:M1M2Siy(0<y≦0.5)で表される。

(もっと読む)

半導体装置の製造方法

【課題】LDD層又はハロー層を形成する際に結晶欠陥の発生を防止できるようにした半導体装置の製造方法を提供する。

【解決手段】NMOSトランジスタ10とPMOSトランジスタ20とを同一のシリコン基板1上に有する半導体装置の製造方法であって、シリコン基板1上にゲート酸化膜21を形成する工程と、NMOS領域のゲート酸化膜21上にゲート電極22を形成すると共に、PMOS領域のゲート酸化膜21上にゲート電極23を形成する工程と、ゲート電極22、23を覆うようにシリコン基板1上にPSG膜を形成する工程と、PSG膜をエッチバックして、ゲート電極22両側のシリコン基板1上にサイドウォール25を形成すると共に、ゲート電極23両側のシリコン基板1上にサイドウォール26を形成する工程と、サイドウォール25、26に含まれるP(リン)をシリコン基板1に熱拡散させる工程と、を含む。

(もっと読む)

デュアルメタルゲート構造の形成方法

方法は、第1ウェル領域(16)と第2ウェル領域(18)を有する半導体層(13)上に、第1ゲート誘電体層(26)を形成することと;第1ゲート誘電体層上に第1メタルゲート電極層(28)を形成することと;第1メタルゲート電極層上と、第1ゲート誘電体層の側壁と第1メタルゲート電極層の側壁とに、側壁保護層(36)を形成することと;第2ウェル領域上にチャネル領域層(40)を形成することと;チャネル領域層上に第2ゲート誘電体層(42)を形成することと;第2ゲート電極層(44)を形成することと;第1ウェル領域上に、第1ゲート誘電体層と第1メタルゲート電極層それぞれの一部を含む第1ゲートスタック(58)を形成することと;チャネル領域層上と第2ウェル領域上に、第2ゲート誘電体層と第2メタルゲート電極層それぞれの一部を含む第2ゲートスタック(66)を形成することとを含む。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】素子分離部の分離幅を調整することによって、所望する特性を有するMISFETを得ることのできる技術を提供する。

【解決手段】素子分離部4の分離幅Laおよび分離幅La’を相対的に狭くすることにより、第2MISFETQ2のチャネル領域へ及ぼす応力の影響を大きくして、しきい値電圧の変化を相対的に大きくし、素子分離部4の分離幅Lbおよび分離幅Lb’を相対的に広くすることにより、第4MISFETQ4のチャネル領域へ及ぼす応力の影響を小さくして、しきい値電圧の変化を相対的に小さくする。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタ及びp型MISトランジスタの双方において、所望のシリサイド組成比を有する金属シリサイド膜からなるフルシリサイド化ゲート電極を精度良く実現する。

【解決手段】半導体装置は、第1の活性領域10a上に形成された第1のゲート絶縁膜13a、第1のゲート絶縁膜13a上に形成された第1のフルシリサイド化ゲート電極24a、及び第1のサイドウォール17aとを有するn型MISトランジスタと、第2の活性領域10b上に形成された第2のゲート絶縁膜13b、第2のゲート絶縁膜13b上に形成された第2のフルシリサイド化ゲート電極24b、及び第2のサイドウォール17bとを有するp型MISトランジスタとを備える。第1のフルシリサイド化ゲート電極24aの上面高さは、第2のフルシリサイド化ゲート電極24bの上面高さよりも低い。

(もっと読む)

インバータの作製方法及びインバータ

【課題】 簡便に作製できるE/Dインバータを提供する。

【解決手段】 本発明は、同一基板上に形成され、チャネル層がIn、Ga、Znから選択される少なくとも1つの元素を含む酸化物半導体からなるインバータの作製方法であって、前記インバータは複数の薄膜トランジスタを有するエンハンスメント−ディプリーション(E/D)インバータであり、前記チャネル層の膜厚が互いに異なる第1のトランジスタと第2のトランジスタと、を形成する工程と、前記第1及び第2のトランジスタのチャネル層のうち、少なくとも1つを熱処理する熱処理工程と、を含むことを特徴とするものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】しきい値電圧が異なる複数のMISFETが混在するチップにおいて、MISFETの短チャネル効果を抑制しつつGIDL電流およびBTBT電流等のリーク電流を抑制する。

【解決手段】相対的にしきい値電圧の低いnチャネル型MISFETQn3が形成される領域ALTNにしきい値電圧調整用に注入する不純物の濃度は、相対的にしきい値電圧の高いnチャネル型MISFETQn2が形成される領域AHTNにしきい値電圧調整用に注入する不純物の濃度より低くする。また、領域ALTNにおけるn−型半導体領域19およびパンチスルーストッパ層20を形成する際の不純物の注入量は、それぞれ領域AHTNにおけるn−型半導体領域16およびパンチスルーストッパ層17を形成する際の不純物の注入量より多くする。

(もっと読む)

自己整合したソース/ドレイン領域を有するフィン型電界効果トランジスタ・デバイスおよびその形成方法

【課題】改良されたフィン電界効果トランジスタ(FinFET)デバイスと、その製造方法とを提供する。

【解決手段】1つの側面において、電界効果トランジスタ・デバイスを製造する方法は次のステップを含む。その上にシリコン層を有する基板が準備される。そのシリコン層においてフィン・リソグラフィー・ハードマスクがパターニングされる。フィン・リソグラフィー・ハードマスクの中央部分の上にダミー・ゲート構造が置かれる。ダミー・ゲート構造の周りにフィラー層が堆積させられる。フィン・リソグラフィー・ハードマスクの中央部分の上を中心として、フィラー層にトレンチを形成するためにダミー・ゲート構造が除去され、それはデバイスのフィン領域をデバイスのソース領域およびドレイン領域から区別する。フィン領域内のフィン・リソグラフィー・ハードマスクは、シリコン層に複数のフィンをエッチングするために使用される。フィンの上にゲート・スタックを形成するためにトレンチはゲート材料で満たされる。デバイスのソース領域およびドレイン領域を形成するためにフィラー層が除去され、ソース領域およびドレイン領域は無傷であってゲート・スタックと自己整合させられている。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】 半導体装置の表面側構造の特性の不揃いを、裏面側の加工時に補償する半導体装置の製造方法を提供する。

【解決方法】 ウェーハ26に単位FET構造の複数個を形成した後、単位FET構造ごとにゲート閾値電圧の測定を行う。ウェーハ26の裏面を加熱して不純物活性化を行う際に、ゲート閾値電圧が低い単位FET構造40では加熱温度を下げたレーザ照射44を実行し、ゲート閾値電圧が高い単位FET構造50では加熱温度を上げたレーザ照射54を実行する。ゲート閾値電圧の測定結果に基づいて不純物活性化の加熱条件を設定することで、単位FET構造の特性の不揃いを補償し、半導体装置の特性を揃えることができる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体領域にn型不純物領域およびp型不純物領域を形成する際に、該半導体領域に形成されるn型およびp型不純物を含む不純物領域を小さくできる、半導体装置の製造方法を提供すること。

【解決手段】 nMOS形成領域の多結晶シリコン膜にn型不純物を導入し、加熱処理によりn型不純物領域を形成し、pMOS形成領域の多結晶シリコン膜にp型不純物を導入し、加熱処理によりp型不純物領域を形成することを含む半導体装置の製造方法であって、pMOS形成領域の多結晶シリコン膜をマスクで覆って、nMOS形成領域の多結晶シリコン膜の表面にn型不純物を導入する工程と、酸素を用いた処理により前記マスクを除去するとともに、nMOS形成領域の多結晶シリコン膜の表面に酸化膜10を形成する工程と、酸化膜10をマスクに用いてpMOS形成領域の多結晶シリコン膜1の表面にp型不純物12を導入する工程とを含むことを特徴とする。

(もっと読む)

PMOSトランジスタ製造方法及びCMOSトランジスタ製造方法

【課題】簡単な工程を通じて優れた動作特性を有するPMOSトランジスタ及びCMOSトランジスタの製造方法を提供する。

【解決手段】 PMOSトランジスタの製造方法において、基板上にゲート酸化膜パターン及び該ゲート酸化膜パターン上に積層されるゲート電極を含むゲート構造物を形成する段階と、前記ゲート構造物に隣接する両側の基板表面下に周期表第3族からなる不純物を注入させて複数の不純物領域を形成する段階と、前記基板の表面及びゲート構造物表面上に不純物拡散防止膜を形成する段階と、前記不純物拡散防止膜上にシリコン窒化膜を形成する段階と、前記不純物領域に含まれる不純物を活性化させながら前記不純物領域間に歪みシリコン領域(strained silicon region)が形成されるように前記基板を熱処理する段階とを有することを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の厚さが互いに異なる複数種類のMISトランジスタを内蔵する半導体集積回路装置において、信頼度の高いゲート絶縁膜を形成すると同時に、MISトランジスタの製造を容易とする。

【解決手段】シリコン酸化膜9を半導体基板1の表面に形成した後、実効膜厚が薄いゲート絶縁膜が形成される領域のシリコン酸化膜9をフッ酸水溶液を用いて除去し、その後半導体基板1上に高誘電率絶縁膜10を形成することにより、高誘電率絶縁膜10とシリコン酸化膜9との積層膜からなるゲート絶縁膜12、および高誘電率絶縁膜10からなるゲート絶縁膜11の2種類のゲート絶縁膜を半導体基板1上に形成する。

(もっと読む)

161 - 180 / 334

[ Back to top ]