Fターム[5F048BB15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB15]の下位に属するFターム

絶縁膜厚が異なるもの (781)

絶縁材料が異なるもの (340)

注入量、注入物質が異なるもの (323)

Fターム[5F048BB15]に分類される特許

81 - 100 / 334

半導体装置の製造方法

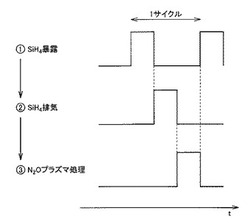

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、最適な仕事関数を有するメタルゲート電極を持つ半導体装置及びその製造方法に関する。

【解決手段】n チャネルMIS トランジスタを含む半導体装置であり、n チャネルMIS トランジスタは、基板上に形成されたp 型半導体領域、p 型半導体領域に形成されたソース領域102及びドレイン領域104、ソース領域102及びドレイン領域104間のp 型半導体領域上に形成されたゲート絶縁膜106、ゲート絶縁膜106上に形成された金属層108及び化合物層110からなる積層構造を持つゲート電極を有する。金属層108は2 nm未満の厚さ及び4.3 eV以下の仕事関数を有し、化合物層110は4.4 eVを越える仕事関数を有しかつAl及び金属層108とは異なる金属を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】ホール移動度を向上し、ジャンクションリークを低減する。

【解決手段】DSB(Direct Silicon Bonded)基板は、第1の基板および第2の基板を含み得る。ここで、第2の基板は、第1の基板に比べて、45度の結晶方位ねじれ角に回転され得る。閾値電圧(Vt)に基づいて調整された厚さを備えるDSB基板を含む半導体装置および半導体装置の製造方法が開示されている。言い換えると、より厚い基板または層が高閾値電圧(HVt)に対応し、より薄い基板または層が低閾値電圧(LVt)に対応し得る。この薄膜化により、LVt装置において、さらに移動度が向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】各々ばらつきの少ない異なる閾値電圧を有する複数のトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板2上に形成された高誘電率材料を母材料とするゲート絶縁膜11、ゲート電極12、およびゲート絶縁膜11に接するように形成されたSiNを主成分とする絶縁材料からなるオフセットスペーサ13、を有する低閾値電圧MISFET10と、半導体基板2上に形成された高誘電率材料からなるゲート絶縁膜21、ゲート電極22、およびゲート絶縁膜21に接するように形成されたSiNを主成分とする絶縁材料からなるオフセットスペーサ23、を有する高閾値電圧MISFET20と、を有し、オフセットスペーサ23は、オフセットスペーサ13よりも、単位体積当たりのSi−H結合とN−H結合の存在比、単位体積当たりのClの量、および単位体積当たりのHの量の少なくともいずれか1つが大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】閾値電圧が相対的に高い半導体装置のチャネル領域における不純物濃度を閾値電圧が相対的に低い半導体装置のチャネル領域における不純物濃度よりも高くすると、閾値電圧が相対的に高い半導体装置の駆動力の低下を招来する虞があった。

【解決手段】半導体装置は、第1のトランジスタと第2のトランジスタとを備えている。第1のトランジスタは、第1のチャネル領域3aと、第1のゲート絶縁膜4aと、第1のゲート電極5aと、第1のエクステンション領域8aとを有している。第2のトランジスタは、第1のトランジスタよりも高い閾値電圧を有しており、第2のチャネル領域3bと、第2のゲート絶縁膜4bと、第2のゲート電極5bと、第2のエクステンション領域8bとを有している。第2のエクステンション領域8bは浅接合化不純物を含んでおり、第2のエクステンション領域8bの接合深さは第1のエクステンション領域8aの接合深さよりも浅い。

(もっと読む)

分周回路及び半導体装置

【課題】回路動作の安定性の向上と、消費電力の低減とを両立できるようにした分周回路及び半導体装置を提供する。

【解決手段】発振回路に近い前段の側にあって高い周波数で動作するFF回路10と、発振回路から遠い後段の側にあって低い周波数で動作するFF回路10と、を備え、前段と後段の各FF回路10は、分周回路の動作時に通常、オン、オフを繰り返すFB−SOI−MOSFET11〜14、21、25をそれぞれ有し、前段の各FF回路10が有するMOSFET11〜14、21、25の閾値電圧の絶対値を│Vth1│とし、後段の各FF回路10が有するMOSFET11〜14、21、25の閾値電圧の絶対値を│Vth2│としたとき、│Vth1│<│Vth2│に設定されている。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

半導体装置の製造方法

【課題】所望のMOSトランジスタのみにチャネル領域に引っ張り応力を印加してキャリア移動度を向上させ、且つ、製造工程の複雑化を抑える。

【解決手段】シリコン基板10上にnMOSトランジスタのゲート絶縁膜13およびゲート電極14を非単結晶シリコンで形成し、ゲート電極14をマスクとして例えばAsやSb等の比較的質量数が大きい(質量数70以上)n型ドーパントを注入することで、nMOSトランジスタのソースドレイン領域を形成する。それにより、ゲート電極14は非晶質化する。そして、ゲート電極14が再結晶化する温度(約550℃)以下の温度条件でゲート電極14を覆うようにシリコン酸化膜40を形成し、その後1000℃程度の加熱処理を行う。それにより、ゲート電極14内に強い圧縮応力が残留すると共に、その下のチャネル領域には強い引っ張り応力が印加され、当該nMOSトランジスタのキャリア移動度は向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート配線に達するコンタクトホールを確実に形成し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38を形成する工程と、第1応力膜とエッチング特性が異なる絶縁膜40を形成する工程と、第1領域2を覆う第1マスク60を用いて、第2領域内の絶縁膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の絶縁膜をサイドエッチングする工程と、第1マスクを用いて第2領域内の第1応力膜をエッチングする工程と、絶縁膜とエッチング特性が異なる第2応力膜を形成する工程と、第2領域を覆い、第1領域側の端面が絶縁膜上に位置する第2マスクを用いて、第2応力膜の一部が第1応力膜の一部及び絶縁膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】NチャネルMOSFETとPチャネルMOSFETを備える半導体装置において、PチャネルMOSFETの閾値電圧のばらつきを抑制し、製造歩留まりを上げる。

【解決手段】半導体基板103の上にゲート絶縁膜110A、110Bを形成した後、PチャネルMOSFET形成領域107に形成されたゲート絶縁膜110Bを第一マスク111で覆う。次に、NチャネルMOSFET形成領域106およびPチャネルMOSFET形成領域107に第一金属層112を形成し、PチャネルMOSFET形成領域107から第一金属層112および第一マスク111を除去することにより、PチャネルMOSFET形成領域107に形成されたゲート絶縁膜110Bを露出させる。その後、NチャネルMOSFET形成領域106およびPチャネルMOSFET形成領域に107ゲート電極を形成する。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

半導体素子およびその製造方法

【課題】チャンネル長および延長ソース/ドレイン領域のドーピング条件によって閾値電圧を調製できる半導体素子の提供。

【解決手段】SOI構造の半導体層の上に形成された高Vt素子と、前記半導体層の上に形成され、高Vt素子よりも低い閾値電圧を有する低Vt素子とを有し、高Vt素子と低Vt素子とはMOSFET素子であって、延長ソース領域と延長ドレイン領域との間の部分であるチャンネルを有し、高Vt素子は低Vt素子よりもチャンネル長が長いSOI構造の半導体素子。

(もっと読む)

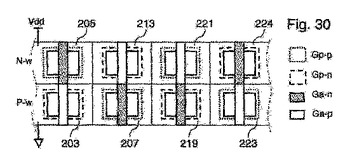

明白に異なる閾値電圧を有するトランジスタを持つSOIから製造する集積回路

本発明は、埋め込まれた絶縁材料面によって半導体基板層から隔てられた活性半導体層を含む集積回路に関する。この集積回路は、同じ型の第1および第2のトランジスタ(205、213)と、第1および第2のトランジスタの真下に配置された第1および第2の接地面とを有し、第1のトランジスタの接地面のドーピングは、第1のトランジスタのソースのドーピングと反対のドーピングであり、第1の閾値電圧を有する。第2のトランジスタの接地面のドーピングは、第2のトランジスタのソースのドーピングと同一のドーピングであり、第2の閾値電圧を有する。第1の閾値電圧は、第1のトランジスタのソースと接地面との間に印加される電位差に依存し、第2の閾値電圧は、第2のトランジスタのソースと接地面との間に印加される電位差に依存する。  (もっと読む)

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

ソース/ドレイン延長部又は/及びハローポケットと組み合わせて空のウエルを使用した電界効果トランジスタの構成及び製造

【課題】 混合信号適用例を含むアナログ及びデジタル適用例用のIGFETを与える半導体製造プラットフォームに適した対称的及び非対称的の両方の絶縁ゲート電界効果トランジスタ(「IGFET」)が、高性能を達成する上で空のウエル領域を使用する。

【解決手段】 各空のウエルの上部近くにおいては半導体ウエルドーパントが比較的少量である。各IGFET(100,102,112,114,124又は236)は、空のウエル(180,182,192,194,204又は206)のボディ物質のチャンネルゾーンによって横方向に分離された一対のソース/ドレインゾーンを有している。ゲート電極が該チャンネルゾーン上方でゲート誘電体層の上側に位置している。各ソース/ドレインゾーン(240,242,280,282,520,522,550,552,720.722、752又は752)が主要部分(240M,242M,280M,282M,520M,522M,550M,552M,720M,722M,752M又は752M)及び一層軽度にドープした横方向延長部(240E,242E,280E,282E,520E,522E,550E,552E,720E,722E,752E又は752E)を有している。代替的に又は付加的に、該ボディ物質の一層高度にドープしたポケット部分(250又は290)が該ソース/ドレインゾーンの内の一方に沿って延在する。存在する場合には、該ポケット部分は典型的に該IGFETを非対称的装置とさせる。

(もっと読む)

半導体装置の製造方法

【課題】素子特性を劣化させることなく、しきい値電圧の低い、金属のゲート電極を有するPチャネルMOSトランジスタを備えた半導体装置を製造することを可能にする。

【解決手段】半導体領域2上にゲート絶縁膜5を形成するステップと、第1金属元素と、OH基、NOx(x=1,2)基のうち少なくとも一つを含有する酸素含有金属層6をゲート絶縁膜上に形成するステップと、酸素含有金属層上に第2金属元素を含むゲート電極膜7を形成するステップと、ゲート電極膜を形成した後、酸素含有金属層の熱分解反応或いは脱水反応が生じる温度以上に加熱するステップと、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】歩留まりが向上して信頼性の高いフラッシュメモリセルを備えた半導体装置の製造方法を提供すること。

【解決手段】第1窓70aを有する第1レジストパターン70を第2絶縁膜69上に形成する工程と、第1レジストパターン70をエッチングマスクにしてコンタクト領域CRが露出する第1開口69dを形成する工程と、第1レジスト部76aを有する第2レジストパターン76を第2導電膜74上に形成する工程と、第2レジストパターン76をエッチングマスクにし、第1、第2導電体67a、74a、フローティングゲート67d、及びコントロールゲート74dを形成する工程と、第3レジストパターン80を各領域I、IIに形成する工程と、第3レジストパターン80をエッチングマスクにして第2窓80a下の第2導電体74aを除去する工程と、を有する半導体装置の製造方法による。

(もっと読む)

半導体集積回路装置

【課題】従来のパワースイッチと比較して、高速動作を行う活性状態と、内部論理状態は保持しているが低リーク状態である非活性状態を実現し、その二つの状態間の遷移を高速かつ低雑音かつ低電力を実現する。

【解決手段】第1の外部電源電圧(VDD)を与える第1電源線と第2の外部電源電圧(VSS)を与える第2電源線間に、複数の回路からなる内部回路ブロックと電源電圧を制御するパワー制御回路を具備し、制御回路は出力MOSFET(MPP)を具備し、出力MOSFETはゲートとソースが等電圧であっても一定のオフ電流が流れるものであって、出力MOSFET(MPP)の閾値電圧は、内部回路MOSFETのそれよりも小さい。

(もっと読む)

81 - 100 / 334

[ Back to top ]