Fターム[5F048BE00]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ウェル (5,077)

Fターム[5F048BE00]の下位に属するFターム

濃度分布に特徴のあるウェル (142)

二重ウェル (485)

両ウェル(P・N) (2,414)

同型多ウェル (525)

深さの異なる複数ウェル (355)

濃度の異なる複数ウェル (175)

表面エピ層より深いウェル (12)

ウェルなしCMOS (42)

ウェルに電圧印加 (892)

その他 (30)

Fターム[5F048BE00]に分類される特許

1 - 5 / 5

半導体装置

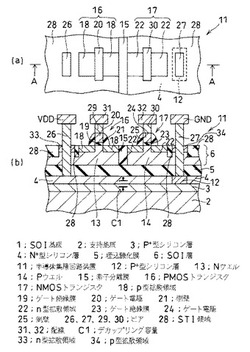

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

半導体装置

【課題】DAT技術を利用した電力増幅器において、能動素子として高耐圧トランジスタを用いた場合に、その特性を十分に活用することができる技術を提供する。

【解決手段】3個のほぼ等価なプッシュプル増幅器を具備している。プッシュプル増幅器における1対のトランジスタ3A〜3Fのドレインは、金属配線1A〜1Hから成る電流経路により相互に接続され、電流経路の中間点が正電源Vddに接続されている。金属配線1A〜1Hのうちトランジスタのドレインからその正電源Vddに至る部分が1本の1次コイルを構成する。1次コイルが、それらと近接して配置された金属配線2から成る2次コイルと磁気的に結合することにより、1次コイルからの出力を合成し2次コイルの出力端子から出力する。1本の1次コイルに相当する金属配線の長さに対する、2次コイル全体に相当する金属配線の長さの比が、およそ3である。

(もっと読む)

高電圧シーモス素子及びその製造方法

【課題】実施例は、フォトアラインキー形成のために別途のマスクを形成する必要がないので、工程を単純化して、製造費用を節減することができる高電圧シーモス素子及びその製造方法を提供する。

【解決手段】高電圧シーモス素子の製造方法は、半導体基板の所定領域が露出した第1酸化膜パターンを形成して、露出した半導体基板上に第2酸化膜パターンを形成して、第1酸化膜パターンをマスクにしてイオン注入及びアニーリングを遂行して高電圧ディープウェル領域を形成する。このような場合、アニーリングによって第2酸化膜パターンが拡散して高電圧ディープウェル領域の表面に段差が発生する。このような段差はフォトアラインすることに使用することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体措置で発生した熱を放熱しやすくすることによってESD耐圧に優れた半導体装置およびその製造方法を提供する。

【解決手段】 拡散層領域3に形成されたチャネル11の上には、ゲート絶縁膜7を介してゲート電極8が設けられている。また、ゲート電極8の側壁部には、サイドウォール9が形成されている。そして、ゲート電極8上とソース・ドレイン領域5上の一部とに、ゲート電極8およびサイドウォール9を被覆するようにしてシリサイドプロテクション膜10が形成されている。シリサイドプロテクション膜10が設けられていないソース・ドレイン領域の上には、シリサイドプロテクション膜10に隣接して金属シリサイド膜6が形成されている。ここで、シリサイドプロテクション膜10は、SiC膜およびSiOC膜の少なくとも一方からなるものとする。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の高集積化、高速度化が進んでも、保護回路を構成するトランジスタがその機能を十分果たすことが可能な構造を提供する。

【解決手段】 保護回路が形成された第1導電型ウエル領域5aと、この第1導電型ウエル領域5aに上部は素子分離領域2に隔てられ、素子分離領域2の底面より下では、接合されている高不純物濃度の第2導電型ウエル領域4とを備えている。第1導電型ウエル領域は、素子分離領域を越えて第2導電型ウエル領域に入り込んでいるか素子分離領域の幅の半分より第2導電型領域側に入り込んでいる。過電流は保護回路のトランジスタのソース/ドレイン領域間を流れずに、ドレイン領域から空乏層が延びて第1導電型ウエル領域の第2導電型ウエル領域に入り込んだ部分に接触して、ドレイン領域と第2導電型ウエル領域に入り込んだ部分との間を流れるようになる。

(もっと読む)

1 - 5 / 5

[ Back to top ]