Fターム[5F048BH06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | PN接合分離 (956) | ガードリング(ガードバンド) (263) | ガードリングが複数形成されたもの (50)

Fターム[5F048BH06]に分類される特許

1 - 20 / 50

半導体装置

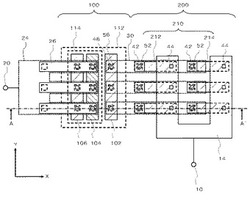

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

裏面照射型固体撮像素子及びそれを備えた撮像装置

【課題】従来の素子の作製プロセスに特別なプロセスを追加することなく、端面で発生した電子が画素部に混入することによって生じるノイズを低減することができる裏面照射型固体撮像素子及びそれを備えた撮像装置を提供する。

【解決手段】裏面照射型固体撮像素子100は、画素領域20、pウエル30、nガードリング40、pガードリング50、端面103〜106を有し、画素領域20から各端面103〜106に向かって、画素領域20を囲むように、pウエル30、nガードリング40及びpガードリング50が順次形成され、pウエル30にはpウエル端子31、nガードリング40にはnガードリング端子41、pガードリング50にはpガードリング端子51が、それぞれ設けられ、各端子に印加される電圧が、nガードリング端子電圧>pウエル端子電圧≧pガードリング端子電圧≧裏面端子電圧の関係を有する。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

半導体装置

【課題】不要な寄生素子の影響を排除できる低容量の過渡電圧保護素子を提供する。

【解決手段】半導体基板上に第1のエピタキシャル層210を形成し、第1のエピタキシャル層の表面近傍に埋め込み層220を形成し、埋め込み層上に第2のエピタキシャル層211を形成し、第2のエピタキシャル層内に第1のディープ拡散層250を形成し、第1のディープ拡散層内にツェナーダイオードを形成し、ツェナーダイオードから離れた位置に第1のPNダイオードを形成し、ツェナーダイオードは第1の分離層240により分離されており、第1のPNダイオードは第2の分離層241で分離されており、ツェナーダイオードと第1のPNダイオードが埋め込み層を経由して逆方向に直列接続されることにより、不要な寄生素子の影響を排除でき、かつ低容量の過渡電圧保護素子を実現する。

(もっと読む)

半導体装置

【課題】小さな面積で電源端子との間に保護素子が設けられていないオープンドレイン信号端子のESD保護を図る半導体装置を提供する。

【解決手段】第1導電型ウェルの表面にソースが第2の電源に接続され、ドレインがオープンドレイン信号端子に接続された第2導電型MISトランジスタを設ける。MISトランジスタの電流が流れる方向と並行にMISトランジスタの両側に第2導電型の第1領域を設け、オープンドレイン信号端子に接続する。その全体を第2の電源に接続された第1導電型ガードリングで囲い、さらにその外側を第1の電源に接続された第2導電型ガードリングで囲う。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の主面上に素子形成領域を取り囲むように形成されたスリットを有する半導体装置の信頼性を向上させることのできる技術を提供する。

【解決手段】ボンディングパッドBPに用いる第6層目の配線M6の上面を露出するように形成された開口部31の側面と、ガードリングGRの周りを囲み、その底部がバリア絶縁膜22を突き抜けないように第1パッシベーション膜30、接着用絶縁膜29、および層間絶縁膜23に形成されたスリットSLの内壁(側面と底面)とを第2パッシベーション膜32により覆う。

(もっと読む)

半導体装置および測定方法

【課題】内包されるダイオードの電気的特性を直接かつ簡便に測定することが可能な半導体装置および当該半導体装置に関する測定方法を提供する。

【解決手段】半導体装置は、n-層6およびp-層7と、ガードリング12と、チャネルストッパ領域14と、等電位アルミ15と、コレクタ電極8とを備える。チャネルストッパ領域14は、ガードリング12の外周側に位置するように、半導体基板の主表面に形成される。等電位アルミ15は、チャネルストッパ領域14に電気的に接続される。コレクタ電極8は、半導体基板の裏面上に形成される。半導体基板は、p-層7とn-層6とを含む。p-層7は、コレクタ電極8と電気的に接続される。n-層6は、p-層7と直接接触し、チャネルストッパ領域14と直接接触する。等電位アルミ15はチャネルストッパ電極16を含む。

(もっと読む)

静電気保護用半導体装置

【課題】高耐圧の内部素子をESDの過電流ノイズとラッチアップ試験の過電流ノイズから保護する静電保護回路装置を提供する。

【解決手段】ESD保護素子のガードリングとラッチアップ試験の過電流ノイズから保護するラッチアップ保護ダイオードのカソードを共有することにより、ESDの過電流ノイズとラッチアップ試験の過電流ノイズの両方のノイズから、内部回路を保護しつつ、静電保護回路装置のサイズ縮小を図ることができる。

(もっと読む)

半導体装置

【課題】隣接する保護装置を備える半導体装置において、クロストークノイズの低減を実現する。

【解決手段】本発明に係る半導体装置に備えられた隣接位置に配置される保護装置50A,50Bは、第1導電型半導体基板1と、第1導電型ウェル12と、保護対象の回路の端子に接続された第2導電型の第1の領域22、21cと、第1の電圧が印加される、第2導電型の第2の領域21b、21dと、第1導電型ウェル12を囲むように形成された第2導電型ガードリングウェル23と、ガードリングウェル23の深層部に接触し、第1の領域22、21cに接触せずに隣接して形成された第2導電型深層領域24と、第1導電型ウェル12よりも不純物濃度が高く、第2導電型深層領域24より下層に配置され、第1の領域22の下層から、少なくともその近傍領域の第2導電型深層領域24までに亘って形成された第1導電型深層領域14とを備える。

(もっと読む)

半導体装置

【課題】デジタル領域とアナログ領域とが混載された半導体装置におけるデジタル領域からアナログ領域へのノイズ伝搬を効果的に抑制する。

【解決手段】デジタル領域120とアナログ領域130とが混載された半導体装置100は、平面視でデジタル領域120およびアナログ領域130の外周を取り囲む環状のシールリング140と、シールリング140で囲まれた領域内で、デジタル領域120とアナログ領域130との間に設けられ、アナログ領域130をデジタル領域120から隔離するとともに、シールリング140に電気的に接続されたガードリング150と、ガードリング150と当該ガードリング近傍で電気的に接続された電極パッド160aとを含む。電極パッド160aは、外部の接地端子(180a)に接続されて接地電位とされている。

(もっと読む)

半導体装置

【課題】耐圧の安定化をはかることができる半導体装置を提供する。

【解決手段】半導体装置20は、主表面1aに素子形成領域14を有する半導体基板1と、ガードリング2b,2c,2d,2eと、ガードリング電極7b,7c,7d,7eと、チャネルストッパ領域3と、チャネルストッパ電極7fと、半導体基板1上に絶縁状態で配置されたフィールドプレート9a,9b,10とを備え、フィールドプレート9a,9b,10は、半導体基板1の主表面1aとガードリング電極7eとの間に位置する第1の部分9aと、半導体基板1の主表面1aとチャネルストッパ電極7fとの間に位置する第2の部分9bとを含み、第1の部分9aは、平面視においてガードリング電極7eと重なり合う部分91を有し、第2の部分9bは、平面視においてチャネルストッパ電極7fと重なり合う部分92を有している。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】MOSFETとSBDとを同じ基板に形成したSiC半導体装置において製造工程の簡略化を図る。

【解決手段】外周領域のメサ構造部14を構成するための凹部とSBD20のコンタクト用トレンチ21とを同じ工程で形成する。これにより、SBD20の形成工程の一部を他の部分の形成工程と同時に行うことが可能となり、SBD20を形成するためだけにのみ必要な工程を少なくできる。したがって、MOSFETとSBD20とを同じ基板に形成するSiC半導体装置において、製造工程の簡略化を図ることが可能となる。

(もっと読む)

半導体装置

【課題】論理回路に向けた製造プロセスで製造できるパワーMOSFET及び論理回路を有する半導体装置を提供する

【解決手段】半導体装置は、パワーMOSと論理回路とを有する。第1領域が第1方向及び第1方向と直交する第2方向に並んで複数個配置され、周囲にガードリング領域が設けられて第2領域が構成され、更に第2領域が第1方向及び第2方向に並んで複数個配置されて第3領域で構成される。第1領域は、第1方向に延長され、第2方向に並んで配置された複数のゲート電極及びソース,ドレインを有する複数のMOSFET及びバックゲート領域及びそれぞれを相互に接続する第1配線層を有する。第3領域において、第2方向に延長されてそれぞれ相互に接続する第1配線層同士を接続する第2配線層、第1方向に延長されて第2配線層同士を接続する第3配線層とが設けられてパワーMOSFETが形成される。

(もっと読む)

集積回路内のESD保護に要する面積を縮小する方法および装置

入力/出力(「I/O」)回路(100)は、シリサイドブロック(102)を用いて入力ピン(110)に結合された第1のNチャネル金属酸化物半導体(「NMOS」)電界効果トランジスタ(「FET」)(104)を有する。第1のPチャネル金属酸化物半導体(「PMOS」)FET(106)はこの入力ピンに直接結合され、そのNウェルはESDウェルバイアス回路(124)に電気的に結合される。NMOS低電圧差動信号(「LVDS」)ドライバ(222)も入力ピンに直接接続され、このドライバはカスケード接続されたNMOS FET(224,226)を有する。LVDSドライバの第1のNMOS FET(224)は、接地に電気的に結合された第1のPタップガードリング(308)およびESDウェルバイアスに結合されたNウェルガードリング(312)の中に作られる。LVDSドライバの第2のNMOS FET(226)は接地に電気的に接続された第2のPタップガードリング(324)の中に作られる。  (もっと読む)

(もっと読む)

半導体装置、光ディスク装置

【課題】電流利得のばらつきを低減することができる半導体装置を提供する。

【解決手段】第1導電型の半導体基体1と、この半導体基体1の表面の一部に形成された、バイポーラトランジスタの第2導電型のコレクタ層2と、このコレクタ層2の一部に形成された、バイポーラトランジスタの第1導電型のベース層6と、このベース層6の一部に形成された、バイポーラトランジスタの第2導電型のエミッタ層7と、このエミッタ層7の直下の領域を除いた部分の半導体基体1に形成された、第1導電型の半導体層9とを含む半導体装置を構成する。

(もっと読む)

半導体装置

【課題】PNPN寄生サイリスタによるラッチアップ現象を防止する。

【解決手段】P型半導体基板50pに形成されたNウェル51n内に設けられ、外部端子に接続されたPMOSトランジスタ24と、PMOSトランジスタ24に隣接して配置され、一端及び他端に電源電位VDDQ及び接地電位VSSQがそれぞれ供給されるMOSゲート容量41とを備え、PMOSトランジスタ24とMOSゲート容量41によって構成されるPNPN寄生サイリスタのカソードとなるN型拡散層52nが電源電位VDDQに固定されている。これにより、PNPN寄生サイリスタはオンすることができないことから、ラッチアップ現象により素子が破壊されるという問題がなくなる。

(もっと読む)

半導体装置

【課題】ESD耐量を向上させることが可能な半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、P型基板111と、P型基板111の表面部分に形成された第1のP型ウェル領域105aと、第1のP型ウェル領域105a内に形成された保護トランジスタ117と、第1のP型ウェル領域105aを囲むように形成された第2のP型ウェル領域105bと、第2のP型ウェル領域105b内の表面部分に形成されたP型半導体拡散領域102と、第1のP型ウェル領域105aと第2のP型ウェル領域105bとの間に形成され、これらとそれぞれ所定の間隔をあけて形成されたN型ウェル112と、第1のP型ウェル領域105aとN型ウェル112との間及び第2のP型ウェル領域105bとN型ウェル112との間にそれぞれ形成され、第1のP型ウェル領域105a、第2のP型ウェル領域105bよりも不純物濃度が低いP型基板111とを備える。

(もっと読む)

ガードリング構造およびその製造方法

半導体素子用のガードリング構造。ガードリング構造は、第1層および第1層の上面に第2層を有する半導体積層体と、第1層内に形成されたゲート構造と、第1層内に形成されたガードリングとを有する。第2層は、第1層のドーパント濃度よりも高いドーパント濃度を有する。ゲートおよびガードリングは、単一のマスクを用いて同時に形成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】ノイズ対策による耐圧低下を抑制し、かつ、高速動作できること。

【解決手段】p型半導体基板51上に形成されたディープn型ウェル53と、ディープn型ウェル53上に形成されたp型ウェル56と、p型ウェル56内に形成されたp型半導体領域58と、p型半導体領域58よりもp型ウェル56の表面側に形成されたn型半導体ソース領域60b及びn型半導体ドレイン領域60aと、p型半導体領域58とドレイン領域60aとの間においてドレイン領域60aと接触して形成され、p型ウェル56よりもp型不純物濃度が低濃度である第1の低濃度p型半導体領域57bと、ソース領域60bとドレイン領域60aとの間に形成されたゲート電極59nと、を備える半導体装置である。

(もっと読む)

1 - 20 / 50

[ Back to top ]