Fターム[5F048CC01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 保護回路の構成 (4,292) | 抵抗 (491)

Fターム[5F048CC01]の下位に属するFターム

Fターム[5F048CC01]に分類される特許

1 - 20 / 373

半導体集積回路

ESD保護回路およびこれを備えた半導体装置

ESD保護回路

半導体装置

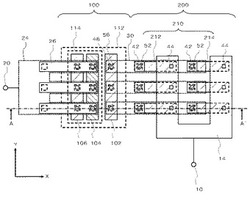

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に負電流が流れた場合でも、回路素子を構成する深い半導体層の電位に対して、半導体基板の電位が低くなるのを抑制して寄生素子を作動させず、半導体装置の誤動作を防止する。

【解決手段】本発明は、n型の半導体基板3と、半導体基板3の一面に形成し、接続する負荷に電力を供給する電力素子1と、n型のソース・ドレイン領域を有するMOSトランジスタ2cを少なくとも1つ含む回路素子2と、電力素子1および回路素子2に対し独立して配置したp型の半導体層4と、半導体基板3および半導体層4と接続する外部回路とを備えている。外部回路は、電源と、電源に一端を接続する抵抗素子と、抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地するダイオードとを有し、抵抗素子の他端に半導体層4を接続する。

(もっと読む)

静電気検出回路

【課題】本発明は、静電気検出回路を提供することを目的とする。

【解決手段】本発明の静電気検出回路は、電源線と接地線との間に直列に接続されているレジスター及びスイッチユニットを備え、前記電源線に静電気が存在する場合、前記スイッチユニットはオンされて、前記レジスターの両端に検出電圧が生じ、前記検出電圧は、静電気保護回路を動作させて静電気を除去するか、又は制御回路を動作させてデータを保存する。

(もっと読む)

半導体装置

【課題】大規模な変更を必要とせず開発上の負荷が小さい半導体装置を提供する。

【解決手段】High SideのIGBTにおける比(コレクタコンタクト面積/コレクタ活性面積)および比(p+領域上コンタクト面積/p+領域面積)の少なくともいずれかが、Low SideのIGBTにおける上記比よりも高い。

(もっと読む)

半導体集積回路及び保護回路

【課題】 より効率的にESDサージ電流を流すことができるESD保護回路を備える半導体集積回路を提供する。

【解決手段】 半導体集積回路100は、クランプMOSトランジスタ30と、第1トリガー回路部10と、第2トリガー回路部20と、内部回路2とを備える。第1トリガー回路部10は、出力端がクランプMOS30のゲートに接続され、クランプMOSトランジスタ30内のサージ電流のチャネル経路を開閉制御する。そして、第2トリガー回路部20は、出力端がクランプMOS30のウエルに接続され、クランプMOSトランジスタ30内のサージ電流のバイポーラ経路を開閉制御する。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

トレンチポリシリコンダイオード

【課題】シリコン内にダイオード構造を位置させた半導体製造方法を提供する。

【解決手段】トレンチポリシリコンダイオードを製造する方法は、N+(P+)型基板上にN−(P−)型エピタキシャル領域を形成すること、エピタキシャル領域内にトレンチを形成すること、さらに、前記トレンチ内に絶縁層を形成し、前記トレンチをポリシリコンで充填する。さらに、P+(N+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのP+(N+)型領域を、N+(P+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのN+(P+)型領域を形成しトレンチ内にポリシリコンダイオードを形成することを含み、ダイオードの一部は、トレンチの上面より低い。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

半導体装置

【課題】異なる電源系統を含む半導体装置において、静電気による破壊から出力回路を保護する保護素子を備えた半導体装置の提供。

【解決手段】半導体装置は、第1の電源電圧と第1の接地電圧からなる第1の電源系統と、第2の電源電圧と第2の接地電圧からなる第2の電源系統と、第2の電源系統から電源供給を受ける出力回路と、第1の電源系統から電源供給を受け、出力回路を駆動する信号を出力する第1の駆動回路と、第1の接地電圧と第2の接地電圧との間に接続された第1の保護回路と、一端が、出力回路の出力ノードに接続され、他の一端が、第1の接地電圧に接続されている第1の保護素子と、を備えている。

(もっと読む)

半導体装置

【課題】ESD耐圧が向上した半導体装置を提供する。

【解決手段】半導体装置は、電源パッドと、電源用配線を有する所定回路と、電源パッドと電源用配線とを接続する第1配線と、所定電位に設定された第2配線と、第1静電保護素子と、第2静電保護素子と、を含む。第1静電保護素子は、第1配線の電位が第1の閾値になった場合に、第1配線から第2配線への電流経路を形成する。第2静電保護素子は、電源用配線と第2配線との間に設けられ、第1配線の電位が第2の閾値になった場合に、電源用配線から第2配線への電流経路を形成する。

(もっと読む)

半導体集積回路およびその製造方法

【課題】半導体集積回路に電源を投入後の通常の動作時にリーク電流の抑制と同時にクランプ電圧の増大防止または低下を図り、保護用MOSトランジスタのゲート電位が変動しにくい保護回路を有する半導体集積回路及び製造方法を提供する。

【解決手段】RCMOS型のESD保護回路1において、保護用MOSトランジスタ5は、内部回路6の内のチャネルの導電型が同じトランジスタに対して、仕事関数差を有する異なる電極材料からゲート電極が形成され、または、仕事関数差を設けるために異なる導電型の半導体電極材料からゲート電極が形成されることによって、単位チャネル幅あたりのリーク電流量が、より減る向きに閾値電圧が異なっている。

(もっと読む)

半導体集積回路

【課題】実装工程中のESD保護とともに、保護用トランジスタのオフリーク電流を低減する。

【解決手段】RCMOS型のESD保護回路において、RC構成の検出回路の出力を、電源配線2のサージを基準電圧配線3に流す保護用トランジスタ5のゲートに伝達するインバータ回路4内で、出力が上記ゲートに接続されたインバータを、電源配線と第3の電源線7との間に接続している。第3の電源線は実装時には、オープンで実装後には負電圧に接続する。

(もっと読む)

半導体装置

【課題】横型IGBTのコレクタ領域側にPN接合によりアバランシェダイオードをさらに設けることにより、ESD保護回路の面積および製造コストを減少させ、かつ、直流電流が重畳した場合にも素子破壊を防止するESD保護回路を含む半導体装置を提供する。

【解決手段】外部電圧を受ける第1のノードと、接地電圧を受ける第2のノードと、第1および第2のノードの間に並列に接続される保護回路および被保護素子を備え、保護回路は、エミッタが第2のノードに接続される横型IGBTと、アノードが横型IGBTのコレクタに接続され、カソードが第1のノードに接続されるアバランシェダイオードと、第1および第2のノードの間に接続され、横型IGBTのゲートに接続されるクランプ駆動回路とを含む。

(もっと読む)

半導体装置、半導体パッケージ、および半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】N型基板10と、N型基板10の一面側に設けられたP型ウェル40と、P型ウェル40に設けられたP型高濃度不純物領域42と、P型ウェル40に設けられたN型のソース・ドレイン領域を有するMOSトランジスタ20と、N型基板10の一面側に設けられ、かつ一方がP型高濃度不純物領域42と電気的に接続し、他方が接地されているソース・ドレイン領域を有するMOSトランジスタ30と、を備える。

(もっと読む)

信号伝達装置および撮像表示システム

【課題】静電気からの保護をより確実に行うことが可能な信号伝達装置等を提供する。

【解決手段】信号伝達装置は、信号の入力動作および出力動作のうちの少なくとも一方の動作を行う複数の画素と、画素に接続された1または複数の信号線を含む複数の配線と、複数の配線のうちの一の信号線と他の一の配線との間に配設され、第1トランジスタおよび容量素子を有する1または複数の静電気保護回路と、静電気保護回路に接続された第1制御線とを備えている。静電気保護回路では、第1トランジスタのゲートが、第1制御線と直接もしくは間接的に接続され、第1トランジスタにおけるソースおよびドレインのうちの一方が、一の信号線および容量素子の一端に接続されると共に、他方が他の一の配線に接続され、容量素子の他端が、第1トランジスタのゲートに接続されている。

(もっと読む)

1 - 20 / 373

[ Back to top ]