Fターム[5F048CC13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 保護回路の構成 (4,292) | ウェル又は基板に電圧を印加したもの (314)

Fターム[5F048CC13]に分類される特許

1 - 20 / 314

半導体装置

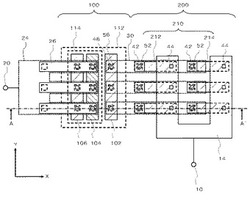

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に負電流が流れた場合でも、回路素子を構成する深い半導体層の電位に対して、半導体基板の電位が低くなるのを抑制して寄生素子を作動させず、半導体装置の誤動作を防止する。

【解決手段】本発明は、n型の半導体基板3と、半導体基板3の一面に形成し、接続する負荷に電力を供給する電力素子1と、n型のソース・ドレイン領域を有するMOSトランジスタ2cを少なくとも1つ含む回路素子2と、電力素子1および回路素子2に対し独立して配置したp型の半導体層4と、半導体基板3および半導体層4と接続する外部回路とを備えている。外部回路は、電源と、電源に一端を接続する抵抗素子と、抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地するダイオードとを有し、抵抗素子の他端に半導体層4を接続する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体装置

【課題】静電気放電が印加されたときの熱破壊を抑制すること。

【解決手段】半導体装置1の半導体活性層16には、n型領域23とp型領域26とn型の埋込み領域30が形成されている。n型領域23は、カソード電極Kに電気的に接続している。p型領域26は、アノード電極Aに電気的に接続している。埋込み領域30は、半導体活性層16のうちのp型領域26の裏面側の少なくも一部を含むように形成されており、p型領域26の裏面に接触しているとともに、不純物濃度が半導体活性層16の不純物濃度よりも濃い。

(もっと読む)

半導体装置

【課題】保護素子の異なるクランプ電圧を容易に設定して形成できる構造の保護素子を含む半導体装置を提供すること。

【解決手段】回路内部のMOS型半導体装置のゲート酸化膜を保護するための保護素子を含む半導体装置であって、該保護素子は、該MOS型半導体装置とその前段回路との間に接続される横型バイポーラトランジスタであり、該横型バイポーラトランジスタのパンチスルー耐圧をクランプ電圧として利用することを特徴とする、半導体装置。

(もっと読む)

半導体集積回路及び保護回路

【課題】 より効率的にESDサージ電流を流すことができるESD保護回路を備える半導体集積回路を提供する。

【解決手段】 半導体集積回路100は、クランプMOSトランジスタ30と、第1トリガー回路部10と、第2トリガー回路部20と、内部回路2とを備える。第1トリガー回路部10は、出力端がクランプMOS30のゲートに接続され、クランプMOSトランジスタ30内のサージ電流のチャネル経路を開閉制御する。そして、第2トリガー回路部20は、出力端がクランプMOS30のウエルに接続され、クランプMOSトランジスタ30内のサージ電流のバイポーラ経路を開閉制御する。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

半導体装置

【課題】異なる電源系統を含む半導体装置において、静電気による破壊から出力回路を保護する保護素子を備えた半導体装置の提供。

【解決手段】半導体装置は、第1の電源電圧と第1の接地電圧からなる第1の電源系統と、第2の電源電圧と第2の接地電圧からなる第2の電源系統と、第2の電源系統から電源供給を受ける出力回路と、第1の電源系統から電源供給を受け、出力回路を駆動する信号を出力する第1の駆動回路と、第1の接地電圧と第2の接地電圧との間に接続された第1の保護回路と、一端が、出力回路の出力ノードに接続され、他の一端が、第1の接地電圧に接続されている第1の保護素子と、を備えている。

(もっと読む)

半導体装置

【課題】Finger形状のソース電極、ドレイン電極と接続される各N+型ソース層、N+型ドレイン層を取り囲むようにP+型コンタクト層が構成される場合でも、サージ電圧印加時に各Finger部の寄生バイポーラトランジスタが均一にオンする。

【解決手段】互いに平行に延在する複数のN+型ソース層9、N+型ドレイン層8を取り囲むようにP+型コンタクト層10を形成する。N+型ソース層9上、N+型ドレイン層8上及びN+型ソース層9が延在する方向と垂直方向に延在するP+型コンタクト層10上にそれぞれ金属シリサイド層9a、8a、10aを形成する。金属シリサイド層9a、8a、10a上に堆積された層間絶縁膜13に形成されたコンタクトホール14を介して、該各金属シリサイド層と接続するFinger形状のソース電極15、ドレイン電極16及び該Finger形状の各電極を取り囲むP+型コンタクト電極17を形成する。

(もっと読む)

半導体装置

【課題】ESD耐圧が向上した半導体装置を提供する。

【解決手段】半導体装置は、電源パッドと、電源用配線を有する所定回路と、電源パッドと電源用配線とを接続する第1配線と、所定電位に設定された第2配線と、第1静電保護素子と、第2静電保護素子と、を含む。第1静電保護素子は、第1配線の電位が第1の閾値になった場合に、第1配線から第2配線への電流経路を形成する。第2静電保護素子は、電源用配線と第2配線との間に設けられ、第1配線の電位が第2の閾値になった場合に、電源用配線から第2配線への電流経路を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

半導体装置

【課題】 ESD対策のための特別な工程や専用マスクを増やすことなく、ESD放電能力の向上を図る事が可能な半導体装置を実現する。

【解決手段】

基板上の所定の領域に、MOSFET構造のHVトランジスタ23と保護抵抗回路25からなる高耐圧用のESD保護素子21、及び、MOSFET構造のLVトランジスタ24と保護抵抗回路26からなる低耐圧用のESD保護素子22が形成されている。当該保護抵抗回路25(26)は、ゲート電極8b(8d)を挟んで互いに対抗するようにウェル2(3)の表層に分離形成される抵抗ドリフト領域16(17)の双方が、同導電型の低濃度ドリフト領域5c(5d)により電気的に接続されていることを除き、HVトランジスタ23(LVトランジスタ24)と同一の構造である。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体集積回路のESD保護回路

【課題】 バッテリが逆接続されたときに、大電流が流れて破壊することを防止させることのできるCDMのESD保護回路の提供。

【解決手段】CDM用のESD保護回路のOFFトランジスタ11、13に直列に、寄生ダイオードが、前記OFFトランジスタと逆向きになるようにトランジスタ素子を挿入する回路構成とすることで、上記課題を解決した。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

保護素子及び保護素子を備えた半導体装置

【課題】比較的小さい面積で形成することができ、かつ、素子サイズの微小化が進んでも保護素子として動作させることを可能にする、保護素子を提供する。

【解決手段】半導体基板1に形成された、第1導電型のウェル領域3と、この第1導電型のウェル領域3に隣接して形成された、第2導電型のウェル領域4と、第1導電型のウェル領域3に形成された、第2導電型チャネルのMOSトランジスタと、第1導電型のウェル領域3とMOSトランジスタのソース領域とMOSトランジスタのゲートとに電気的に接続された第1の配線と、MOSトランジスタのドレイン領域と第2導電型のウェル領域4とに電気的に接続された第2の配線とを含む保護素子を構成する。

(もっと読む)

半導体装置

【課題】ESD保護特性のすぐれたESD保護回路を含む半導体装置を構築することが課題となる。

【解決手段】静電気によるサージ電圧が印加されたときだけオン状態になるように、抵抗素子20と容量素子21で形成されるRCタイマーとPLDMOSトランジスタ5とからなるRCタイマー付き放電部1を形成する。また、NMOSオフトランジスタ10、15のそれぞれのソース電極13とドレイン電極16同士を接続したノイズ発生防止部2を形成する。前記RCタイマー付き放電部1のPLDMOSトランジスタ5のソース電極6を電源ライン3に接続する。また、該PLDMOSトランジスタ5のドレイン電極8と前記NMOSオフトランジスタ10のドレイン電極11とを接続する。NMOSオフトランジスタ15のソース電極18を接地ライン4に接続する。

(もっと読む)

1 - 20 / 314

[ Back to top ]