Fターム[5F049MA04]の内容

受光素子−フォトダイオード・Tr (21,418) | 素子の種類 (2,342) | フォトダイオード(PD) (2,089) | PIN接合型 (513)

Fターム[5F049MA04]に分類される特許

501 - 513 / 513

pinダイオードを備えた集積回路構造およびその製造方法

特に、pinフォトダイオード(14)と、バイポーラトランジスタ(58)の高ドープされた接続領域(62)とを含んだ集積回路構造(10)を開示する。高度な制御方法により、pinダイオード(14)の非常に深い中間領域(30)を、オートドーピングを用いずに形成できる。  (もっと読む)

(もっと読む)

光検出装置

検出窓(15)内で光ビームの強度を検出し、この光ビームによって伝送されるデータを検出するための光検出装置は、第1の検出ダイオード(25)と少なくとも2つの第2の検出ダイオード(21a〜24d)からなるアレイとを検出窓内に備える。さらに、データを検出すべく第1の読み出し速度で第1の検出ダイオードを読み出すよう第1の検出ダイオードに接続可能な第1の読み出し回路(35)と、光ビームの強度を検出すべく第1の読み出し速度よりも小さい第2の読み出し速度で第2の検出ダイオードを読み出すよう第2の検出ダイオードに接続可能な第2の読み出し回路(30)とが設けられる。検出窓に追加の検出ダイオードを設けることで、追加の出費とデータ検出に有効利用できる検出窓表面積の減少とをもたらすが、この欠点はデータを伝送する光ビームを検出窓に整列させる制御を追加の検出ダイオードのアレイによって効果的かつ安価に行なえるという事実によって相殺される。  (もっと読む)

(もっと読む)

発光用光半導体素子及び受光用光半導体素子

【課題】光半導体素子と光導波路を精度良く結合させることが可能な発光用光半導体素子を提供する。

【解決手段】発光波長を透過する半導体基板2上に作られた、上記半導体基板の表面100に対して垂直な方向に光を出射する発光用光半導体素子であって、上記発光用光半導体素子外部に出た光を導く光導波路12の一端が位置決めされる出射部11と、上記半導体基板の表面に対して垂直な方向に出射された光を上記出射部の光導波路の一端に導くように反射させる上記表面の一部である反射面8と、を一体に備えた。

(もっと読む)

テルル化カドミウム水銀の製造

テルル化カドミウム水銀(CMT)を製造する方法が開示される。方法は、分子ビームエピタキシ(MBE)によって1つまたは複数のバッファ層を基板上に成長させることを含む。その後、xを0と1を含めて、その間としてテルル化カドミウム水銀Hg1−xCdxTeの少なくとも1つの層が、有機金属気相エピタキシ(MOVPE)によって成長される。バッファ層を成長させるためにMBEを使用することにより、ある範囲の基板がCMT成長に使用されることが可能になる。MBEバッファ層は、CMTの後続のMOVPE成長について正確な配向を提供し、また、MOVPE中のCMTの化学汚染および基板の侵食を防止する。方法は、CMT層のデバイス処理が、結晶CMT層および/またはパッシベーション層の他のMOVPE成長と共に実施されることをも可能である。本発明は、この方法によって形成される新規なデバイスにも関する。  (もっと読む)

(もっと読む)

高速CMOS共存Ge−オン−インシュレータ光検出器の構造および製作方法

【課題】SiCMOS技術と共存可能な高速高効率光検出器を作る問題に対処すること。

【解決手段】本構造は、薄いSOI基板の上のGe吸収層から成り、分離領域、交互になるn型およびp型コンタクト、および低抵抗表面電極を利用する。本デバイスは、下の基板で生成されたキャリアを分離するために埋込み絶縁物を利用して高帯域幅を、Ge吸収層を利用して広いスペクトルにわたった高量子効率を、薄い吸収層および狭い電極間隔を利用して低電圧動作を、さらに平面構造およびIV族吸収材料の使用によってCMOSデバイスとの共存性を、達成する。本光検出器を製作する方法は、薄いSOIまたはエピタキシャル酸化物へのGeの直接成長および高品質吸収層を達成するための後の熱アニールを使用する。この方法は、相互拡散に利用可能なSiの量を制限し、それによって、下のSiによるGe層の実質的な希釈を起こすことなく、Ge層をアニールすることができるようになる。

(もっと読む)

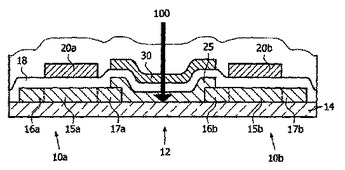

光センサーを備えたアクティブマトリックス型画素デバイス

基板に支持され、ポリシリコンTFT(10)及びアモルファスシリコン薄膜PINダイオード(12)を含む回路を有するアクティブマトリックス型画素デバイス、例えばEL表示装置、が提供される。ポリシリコンアイランドが形成された後に、アモルファスシリコン層がPINダイオード用に堆積されることにより、アモルファスシリコンは高温処理にさらされなくなる。TFTはドープされたソース/ドレイン領域(16a、17a)を有し、その一方(17a)はまた、ダイオードにN型又はP型のドープ領域を提供する。有利なことに、フォトダイオードに別個のドープ領域を設けることが不要になり、処理コストが削減される。反対導電型にドープされたソース/ドレイン領域(16b、17b)を有する第2のTFT(10b)が、ダイオードに他方のドープ領域(16b)を提供し、真性領域(25)が2つのTFT間にそれぞれのポリシリコンアイランドの各々に重なるように横方向に配置される。  (もっと読む)

(もっと読む)

光制御装置

光ファイバー等により入射した入力光17を分岐する部分14、その分岐された入力光の一方であるモニター光12を電気信号に変換する部分(光電変換部分)15と、その電気信号により信号光13の光伝送路を開閉制御する部分16とを備える。出力光18は、モニター光12に応じて出力された電気信号量によって光伝送路の開閉量が制御されることにより、その光パワーが調整される。また、光電変換部分15として、外部電源を用いることなく光電変換が可能な半導体フォトボル素子を用いる。光伝送路を開閉制御する部分16として、マイクロマシンによる光シャッター、又は吸収型変調器あるいは屈折率変調器等の光素子を用いる。

(もっと読む)

(もっと読む)

絶縁体上SiGe(SGOI)基板及び絶縁体上Ge(GOI)基板の製造方法、半導体ウェハ、並びに半導体構造

【課題】絶縁体上ゲルマニウム(GOI)基板材料を製造する方法、該方法により製造されるGOI基板材料、及び本発明の少なくともGOI基板材料を含む様々な構造を提供する。

【解決手段】GOI基板材料は、少なくとも1個の基板、基板上に位置する埋め込み絶縁体層、Ge含有層、埋め込み絶縁体層上に位置する、好ましくは純粋Geを含む。本発明のGOI基板材料の場合、Ge含有層は、GOI膜とも呼ばれる。GOI膜は、デバイスが形成される本発明の基板材料の層である。

(もっと読む)

(もっと読む)

埋込式導波路検出器

以下の段階が含まれる、検出器の作製方法である。上面を有する基板中にトレンチを形成する段階と;前記基板上及び前記トレンチ中に、第1ドープ半導体層を形成する段階と;前記第1ドープ半導体層上及び前記トレンチ中に延在して、第1ドープ半導体層の伝導度よりも低い伝導度を有する第2ドープ半導体層を形成する段階と;前記第2ドープ半導体層上及び前記トレンチ中に延在する第3ドープ半導体層を形成する段階と;前記第1、第2及び第3ドープ半導体層における、上面、実質的な平面を作製して前記トレンチ中の第1ドープ半導体層の上端を露出させるために、前記基板の表面で画定される平面よりも上方の部分を除去する段階と;前記第1ドープ半導体層への第1電気的コンタクトを形成する段階と;前記第3ドープ半導体層への第2電気的コンタクトを形成する段階と、を有する。

(もっと読む)

(もっと読む)

PIN光検出器

PIN光検出器は、第1の半導体コンタクト層と、第1の半導体コンタクト層よりも広い面積を有する半導体吸収層と、第1の半導体コンタクト層と半導体吸収層の間に配置された半導体不活性化層と、第2の半導体コンタクト層とを含む。半導体吸収層及び半導体不活性化層は、第1の半導体コンタクト層と第2の半導体コンタクト層との間に配置される。  (もっと読む)

(もっと読む)

CMOS画像センサおよびその製造方法

赤色光、緑色光および青色光用の2画素検出方式を含むCMOS結像デバイス。1つの画素が、赤色光および青色光を検出し、別の画素が緑色光を検出する。赤色および青色の検出は波長に基づき、またこのデバイスは、赤色/青色画素中で青色光の検出が浅い基板深さで行われ、赤色光の検出がより深い基板深さで行われるような構造になっている。この画素アレイは、赤色/青色画素が緑色画素に隣接し、赤色/青色画素と緑色画素とが交互に配列されるような構造になっている。本発明は、このような結像アレイおよび画素を形成する方法にも関する。  (もっと読む)

(もっと読む)

半導体接合ウエハの製造方法

【課題】低比抵抗のシリコン半導体基板の接合時におけるボイドの発生率を低減させる。

【解決手段】互いに重ね合せる第一シリコン半導体基板1及び第二シリコン半導体基板2のうち、少なくとも一方の厚さを 250μm 以下に薄くすることにより、該半導体基板がしなやかになって、他方の半導体基板と重ね合せる時に両面が貼り付き易くなり、それらの密着性が高まって結合強度が増大すると共に、固着熱処理中に水分や有機物などがガス化しても、これら両半導体基板間の密着性が高いために接合界面の結合力が勝り、発生したガスはシリコン中に拡散され、最終的にボイドは消滅される。

(もっと読む)

PIN構造のラテラル型半導体受光素子

【課題】PIN構造のラテラル型半導体受光素子において、応答速度を低下させることなく受光感度を向上させる。

【解決手段】受光領域2をなすi層15の上面に、光電変換機能を有する色素層4を設ける。

(もっと読む)

501 - 513 / 513

[ Back to top ]