Fターム[5F058BJ07]の内容

Fターム[5F058BJ07]に分類される特許

61 - 69 / 69

半導体装置およびその製造方法

【課題】ゲート酸化膜のリーク電流の発生やゲート酸化膜の耐電圧性の低下を抑制するこ

とができる、信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体シリコン基板と前記半導体シリコン基板上にゲート酸化膜を介して設

けられたゲート配線と、を備えた半導体装置であって、

前記ゲート配線は、ゲート電極、前記ゲート電極に接して設けられたゲート配線上部構

造、ならびに側壁スペーサを有し、

前記側壁スペーサは一種もしくは二種以上の無機化合物絶縁層からなり、

かつ、前記無機化合物絶縁層の少なくとも一種は、窒素含有率が30〜70%の範囲で

あるシリコンオキシナイトライドからなることを特徴とする半導体装置。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ポリメタルゲート構造とデュアルゲート構造とを採用するCMOS LSIにおいて、ゲート電極の一部を構成する高融点金属膜の酸化と、ゲート電極の他の一部を構成するp型多結晶シリコン膜中のホウ素の拡散とを共に抑制することのできるライト酸化処理技術を提供する。

【解決手段】水素ガスおよび酸素ガスと水素ガスとから触媒により合成された水蒸気を含む混合ガスを半導体ウエハ1Aの主面に供給し、エッチングによって削られたゲート電極の端部下のゲート絶縁膜のプロファイルを改善する熱処理を、ゲート電極の一部を構成する高融点金属膜が実質的に酸化されず、かつゲート電極の他の一部を構成するp型多結晶シリコン膜中のホウ素がゲート酸化膜を通って基板に拡散しない低熱負荷条件下で行う。

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】 誘電率が非常に低く且つエッチング耐性が十分に大きな不純物含有シリコン窒化膜を形成することが可能な成膜方法を提供する。

【解決手段】 真空引き可能になされた処理容器4内に、シラン系ガスと窒化ガスと不純物含有ガスとを供給して被処理体Wの表面に不純物含有シリコン窒化膜よりなる薄膜を形成する成膜方法において、前記シラン系ガスと前記窒化ガスとを交互に供給すると共に、前記不純物含有ガスを前記シリコン系ガスと同時に供給し、前記窒化ガスはプラズマにより活性化される。これにより、誘電率が非常に低く、且つエッチング耐性が十分に大きな不純物含有シリコン窒化膜を形成する。

(もっと読む)

半導体装置の製造方法及び絶縁膜の成膜速度の調整方法

【課題】 2MOSの異なる領域で膜厚の異なるNSGサイドウォール絶縁膜を有する半導体装置の製造方法を提供すること。

【解決手段】 シリコン基板1の第1の活性領域100と第2の活性領域110に、第1のゲート電極4−1と第2のゲート電極4−1を形成する。第1のシリコン酸化膜5を形成後、シリコン酸化膜5を介して不純物イオンを注入し、第1の活性領域100と第2の活性領域110に、第1の低濃度領域6−1と第2の低濃度領域6−2を形成する。その後、第1の活性領域100の第1のシリコン酸化膜5を除去し、第2の活性領域110では第1のシリコン酸化膜5を残存させる。オゾン及びテトラエトキシシランの熱分解CVD法により、第1の活性領域100に膜厚が第2の活性領域110より厚い膜厚NSG絶縁膜8を形成し、第1の側壁絶縁膜9−1と第1の側壁絶縁膜9−1よりも薄い膜厚の第2の側壁絶縁膜9−2とを形成する。

(もっと読む)

パルス化高周波源電力を使用するプラズマゲート酸化プロセス

半導体基板上にトランジスタデバイスのゲートを形成する方法は、プラズマリアクタの真空チャンバに基板を配置するステップと、チャンバの真空圧力を維持しつつ酸素を含むプロセスガスをチャンバ内へ導入するステップとを含む。連続した「オン」タイム中に真空チャンバ内のプラズマ生成領域にプラズマを生成し、制御可能なデューティーサイクルを画成する「オン」インターバル及び「オフ」インターバルのうちの、連続した「オン」インターバルを分離する連続した「オフ」インターバル中に、プラズマのイオンエネルギーが減衰するのを許容することにより、数オングストローム程度の厚さの酸化物絶縁層が基板に表面に形成される。酸化物絶縁層の形成中に、デューティーサイクルは、絶縁層におけるイオン衝撃による欠陥の形成を制限するように限定され、真空圧力は、絶縁層における汚染による欠陥の形成を制限するように限定される。導電性ゲート電極が絶縁層の上に形成される。 (もっと読む)

半導体装置の製造方法および半導体装置

【課題】 良質でかつ良好な形状のサイドウォールを備えた半導体装置を形成する。

【解決手段】 ゲート電極側壁のサイドウォールを炭素含有シリコン窒化酸化膜を用いて形成する。炭素含有シリコン窒化酸化膜は、BTBASと酸素を原料に用い、BTBAS流量/酸素流量比を適当に設定すると共に、例えば約530℃等の低成膜温度のCVD法で成膜することができる。炭素含有シリコン窒化酸化膜を用いてサイドウォールを形成することで、窒素原子や炭素原子の寄与により、HF耐性向上やフリンジ容量低減を図れる。また、低温条件で成膜することにより、半導体基板内に導入されている不純物の不要な拡散が抑えられるようになる。これにより、トランジスタ特性を高めかつ安定化させ、半導体装置の高性能化、高品質化を図れるようになる。

(もっと読む)

ケイ素−窒素−含有膜の低温プラズマ化学蒸着法

基板(40、125)上におけるケイ素−窒素−含有膜の低温プラズマ化学蒸着のための方法である。前記方法は、プロセスチャンバ(10、110)に基板(40、125)を提供し、リモートプラズマ源(94、205)の反応物ガスを励起し、その後励起された反応物ガスをシラザン前駆体ガスと混合し、及び化学蒸着プロセスで励起したガス混合物から基板(40、125)上にケイ素−窒素−含有膜を堆積する段階を含む。ひとつの実施形態では、前記反応物ガスは、SiCNH膜を堆積するため窒素含有ガスを含んでよい。また他の実施形態では、前記反応物ガスは、SiCNOH膜を堆積するため酸素含有ガスを含んでよい。  (もっと読む)

(もっと読む)

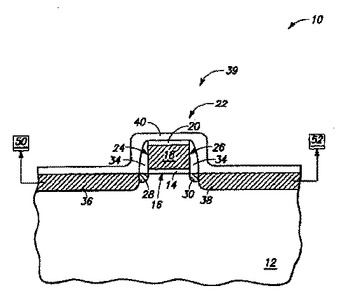

エッチングしたMOSゲート構造の窒素酸化

金属酸化膜半導体の製造方法である(500)。金属酸化膜半導体のゲート構造がエッチングされる(510)。NO又はN2Oである窒素含有ガスが生成され、金属酸化膜半導体に流す(500)。

プレインプラント膜(620)がゲート構造のエッジに成長される。プレインプラント膜は、エッチングプロセスがもたらすゲートスタックエッジの損傷を修復する。実質的に膜は窒化シリコンである。有利にも、そのような膜は従来のsilica oxide膜よりも薄い。より薄い膜は、トンネル酸化膜の不均一さに、有害に起因しない。不均一なトンネル酸化膜は、ゲートとチャネル間に均一でない電界をもたらす。均一でない電界は、多くの悪影響を持つ。有利にも、本発明の実施形態は、ゲートスタックエッジの欠陥を修復することで、従来技術の欠点を克服する。この新たな方法で、ゲートスタックエッジの欠陥が、金属酸化膜半導体デバイスの電気的性質に有害な結果をもたらすことなく、修復される。

この用途に、新たなシリカ酸化膜を応用することにより、薄い修復膜が成長できる。有利にも、本発明の実施形態を用いて製造された半導体は、小型プロセスの加工寸法を用いており、その結果、より密集した半導体デバイスアレイをもたらし、そのようなデバイスの低価格をもたらし、また、本明細書に解説している改良を実現した者たちに対して、競争上の優位性を実現している。  (もっと読む)

(もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

61 - 69 / 69

[ Back to top ]