Fターム[5F064AA02]の内容

ICの設計・製造(配線設計等) (42,086) | ICの形式 (1,534) | カスタムIC (1,426) | セミカスタムIC (1,415)

Fターム[5F064AA02]の下位に属するFターム

マスタスライス、ゲートアレイ (136)

標準セル、スタンダードセル (922)

PLA (305)

Fターム[5F064AA02]に分類される特許

41 - 52 / 52

ハード・インテレクチャル・プロパティ・ブロックのための出力レポーティング技術

【課題】プログラマブル論理よりも高いクロック周波数で動作するHIPブロックからの出力信号を捉える技術を提供すること。

【解決手段】集積回路上のHIPブロックからの出力信号の周波数を低減させる技術を提供する。出力信号の周波数を低減させることによって、HIPブロックよりも低い周波数で動作する集積回路内の回路ブロックは出力信号を捉えることができる。複数の直列結合されたフリップフロップは、出力信号の各周期の間にHIP出力信号の値を格納する。次に、論理回路構成はフリップフロップに格納された値に応答してより低い周波数のHIP出力信号を生成する。また、フリップフロップはHIPブロック内の信号が適切に動作しているかどうかを決定するのに用いられるハートビート信号を生成する。

(もっと読む)

半導体デバイスの多重波長レーザ微細加工

【課題】高品質の加工及び多重波長でのレーザエネルギーがレーザエネルギープロファイルに重なることができるより小さい可能なスポットサイズを達成するために半導体デバイス微細加工に対して目標とされる実質的にジッタのない多重波長レーザエネルギープロファイルを提供する。

【解決手段】異なる時間で異なるレーザ波長によって特徴付けられる特別に成形されたレーザパルスエネルギープロファイル(98,104,156)は、高品質加工及びより小さい可能なスポットサイズを達成する半導体デバイスの微細加工を可能にするために軽減制御ジッタを提供する。

(もっと読む)

論理回路、集積回路設計支援装置、記録媒体および集積回路設計における伝搬遅延調整方法

【課題】作業の自由度が高く簡便にし、配線追加量を確定的且つ少量にできるスタンダードセル式LSI設計におけるECO技術を提供する。

【解決手段】ECOによりセットアップエラーを改善する場合、ECO作業者はCKSEL入力を「1’b0」から「1’b1」に書き替える。セレクタ134が動作し伝達経路が無遅延伝搬系151から遅延伝搬系150に切り替わってセットアップエラーが解消する。ホールドエラーを改善する場合、ECO作業者はDSEL入力を「1’b0」から「1’b1」に書き替える。セレクタ124が動作し伝達経路が無遅延伝搬系141から遅延伝搬系140に切り替わってホールドエラーが解消する。

(もっと読む)

半導体集積回路およびその製造方法

【課題】配線を大幅に変更することなく回路セルの欠陥を救済することができる半導体集積回路とその製造方法を提供する。

【解決手段】行列状に配列された複数の回路セルのうち、列方向に並ぶ1列または複数列の回路セルが配線されずに未使用とされるため、初期設定において未使用とされる列の代わりに、欠陥セルが発見された列を未使用とすることによって、半導体集積回路の欠陥を救済し、歩留まりを大幅に向上させることができる。また、この場合、初期設定において未使用とされる列と欠陥セルが発見された列との間の領域において使用される回路セルの機能を全体的にシフトさせ、これに合わせて配線パターンも全体的にシフトさせることができるため、欠陥の救済に伴う配線パターンや配置の変更を非常に少なくすることができる。

(もっと読む)

集積回路の歩留り及び品質の分析の方法及びシステム

集積回路の歩留りと品質とをテストし、分析し、改善する方法と、装置と、システムとが、本明細書で開示される。例えば、1つの例示的実施形態で、設計欠陥抽出ルールは、少なくとも部分的に、設計製造ルールのセットから導出される。潜在的な欠陥が、設計欠陥抽出ルールを使用して、集積回路レイアウトの表現から抽出される。1つ又は複数の回路テスト中に適用される回路テスト刺激が、判定される。適用された回路テストから生じるテスト応答が、障害を発生した集積回路を識別し、適用された回路テストに関連する1つ又は複数の潜在的なタイプの欠陥の、障害を発生した集積回路での発生を識別するために、評価される。潜在的なタイプの欠陥の発生の障害を発生した集積回路での反復識別に関する情報が、集められ、分析されて、潜在的なタイプの欠陥がレイアウトに従って製造される集積回路に存在する尤度が判定される。 (もっと読む)

半導体集積回路装置

【課題】 半導体集積回路装置の設計中あるいは設計完了後の論理変更を容易とする。

【解決手段】 所定の回路が形成された主領域と、主領域に形成された回路の論理変更に用いる予備素子領域とを有する。予備素子領域は、Pチャンネルトランジスタ領域111〜113と、Nチャンネルトランジスタ領域121〜123と、Pチャンネルトランジスタ領域上及びNチャンネルトランジスタ領域上に設けられた複数のゲート電極131〜134、141〜144と、ゲート電極よりも上層の配線層に形成されたバイパス配線151〜155と、バイパス配線よりも上層に位置する主配線層とを備える。バイパス配線151〜155は、いずれも主配線層とバイパス配線とを分離する絶縁層に形成されたコンタクトホールによって、少なくとも2箇所で主配線層と接続可能に構成されている。

(もっと読む)

情報処理方法、情報処理装置およびプログラム

【課題】 回路設計の過程で冗長回路を検出し、かつ冗長回路を表示可能な情報処理方法を提供する。

【解決手段】 ハードウェア記述言語を用いた回路動作情報およびその回路動作情報を論理合成してネットリストに変換するためのライブラリが格納された記憶部と、表示部とを備えた情報処理装置による冗長回路を検出する情報処理方法であって、記憶部に格納された回路動作情報を一文毎に階層化するステップと、ライブラリを参照し、階層化された回路動作情報を論理合成してネットリストに変換するステップと、論理的に冗長な箇所となる冗長故障箇所をネットリストから検出するステップと、冗長故障箇所を含む冗長回路を示す情報を表示部に表示させるステップとを有するものである。

(もっと読む)

回路装置およびプログラム処理方法

【課題】 機能の変更が可能なリコンフィギュラブル回路を有する回路装置を提供する。

【解決手段】 本発明の集積回路装置は、マッピング用のプログラムに含まれる条件文中にelse文が存在しない場合であっても、代入処理を適切に実行する。具体的には、プログラムのコンパイル時に、条件文の実行に先立って実行される代入処理を探索し(S18のY)、探索した代入処理をelse条件成立時の代入処理として設定する。なお、探索により代入処理がみつからない場合は(S18のN)、記憶部に記憶された最新の変数値をelse条件成立時の代入値として決定する(S22)。

(もっと読む)

ピン・マップ互換性のための半導体ダイのプログラミング

本方法およびシステムによって、ソケットのタイプのそれぞれが異なるピン・マップによって特定される多種多様の業界基準ソケットと互換性を有する半導体ダイが提供される。一実施例において、ダイは、複数の信号線、1またはそれ以上の表面接点、ならびに、信号線および表面の接点に結合された1またはそれ以上の信号セレクタを有する。各信号セレクタは、プログラム信号に基づいて、信号線の1つを表面接点の1つに電気的に接続する。特定の実施例では、各信号セレクタは、マルチプレクサおよびヒューズ要素を含み、マルチプレクサは、ヒューズ要素のプログラム値に基づいて、その入力ポートの1つからその出力ポートへの経路を定める。プログラム信号は、プログラム値を設定することができる。  (もっと読む)

(もっと読む)

局所的に制御されたパラメータ更新をもつ電子ストリーム処理回路およびそのような回路を設計する方法

電子回路、詳細には受信回路はストリーム処理回路(10a〜c)のチェーンを含む。ストリーム処理回路(10a〜c)は制御パラメータ値を受け取るための制御パラメータ入力を有する。可変のブロック・サイズをもつデータを受け取る回路の設計を容易にするために、複数のストリーム処理回路(10a〜c)のそれぞれのストリームの中のサンプルのブロックのブロック・サイズ、各特定のブロック用の制御パラメータ値を選択する制御回路(14)が含まれる。制御回路は、選択されたブロック・サイズおよび制御パラメータ値を指定する命令を局所制御回路(11)に伝達する。各局所制御回路は、制御回路(14)およびチェーンからのそれぞれ対応するストリーム処理回路(10a〜c)の制御入力に結合される。各特定の局所制御回路(11)は、命令の少なくとも一部を受け取り、命令からのパラメータ値をそれに対応するストリーム処理回路(10a〜c)に適用するように構成される。特定の局所制御回路(11)は、連続する制御パラメータ更新の時点の間のブロック・サイズ依存時間間隔をカウントすることによって、命令からのブロック・サイズを使用して制御パラメータ更新のタイミングを制御する。結果として、ストリーム処理回路(10a〜c)の設計をブロック・サイズに適合させる必要がない。  (もっと読む)

(もっと読む)

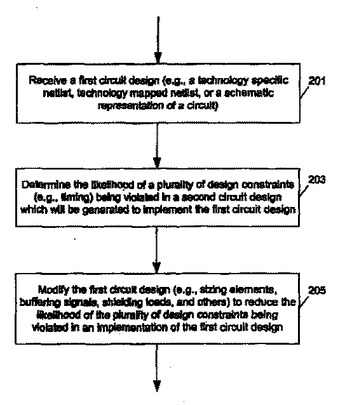

自動回路設計のための方法と装置

回路の後の実装で生じうる逸脱に応じて回路設計を自動的に修正する方法と装置。一態様では、回路を設計する方法は、回路の設計の後の配線実装時に設計制約条件に違反する可能性があるかどうかを判定することと、後の実装で設計制約条件に違反する可能性を低減するように回路設計を修正することを含む。例えば、2よりも大きい多数のファンアウトを持ち、タイミング・クリティカル・パスまたはクリティカルに近いパス上のネットに対する経路は、経路トポロジに敏感であると考えられ、代替配線経路であると、タイミング制約に違反する可能性があり、その後の配線ソリューションのタイミング問題が発生する可能性を低減するために、コスト関数を悪化させない範囲で、回路設計に変換を選択的に適用するとよい。  (もっと読む)

(もっと読む)

標準セル論理によって形成されるモジュラ・アレイ

本明細書に機能ブロックのベース・アレイを有するASICを開示している。各機能ブロックは、複数のプリミティブ・セルを含む。各プリミティブ・セルは、標準のセル・ライブラリの構成要素によって形成される。ベース・アレイは、後でカスタム回路設計と一緒に使用するために事前製造される。  (もっと読む)

(もっと読む)

41 - 52 / 52

[ Back to top ]