Fターム[5F064AA07]の内容

ICの設計・製造(配線設計等) (42,086) | ICの形式 (1,534) | カスタムIC (1,426) | セミカスタムIC (1,415) | PLA (305)

Fターム[5F064AA07]の下位に属するFターム

FPLA (234)

Fターム[5F064AA07]に分類される特許

1 - 20 / 71

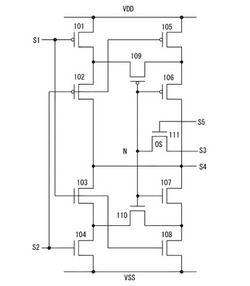

論理回路

【課題】電源電位の供給が遮断されたときでも論理回路の切り替え状態の保持が可能で、電源投入後の論理ブロックの起動時間が短く、低消費電力化が可能な、否定論理積(NAND)回路および否定論理和(NOR)回路を容易に切り替えることができる論理回路を提供する。

【解決手段】酸化物半導体を有するトランジスタを介して、ノードへの電荷保持状態を切り替えることによって、否定論理積(NAND)回路および否定論理和(NOR)回路を容易に切り替えることができる。当該トランジスタにはワイドバンドギャップ半導体である酸化物半導体材料を用いることによって、トランジスタのオフ電流を十分に小さくできるため、ノードに保持した電荷の状態を不揮発とすることができる。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

再構成デバイス、処理配置方法及びプログラム

【課題】再構成デバイスの回路構成変更において、機構追加による回路規模を増やすことなく、処理内容に対する依存を回避しつつ回路構成変更期間を短縮する。

【解決手段】外部メモリ101は、内部に回路構成情報106を保持している。回路構成情報106は再構成デバイス105を構成する要素を動作させる設定群である。コンフィギュレーションコントローラ102は上記メモリ101から結線104を通じ回路構成情報106を取得する。取得した回路構成情報106は結線103を通じて再構成デバイス105へ送られる。

(もっと読む)

プログラマブルロジックデバイス集積回路上の高速シリアルデータレシーバ用のデシリアライザ回路網

【課題】多数の異なるプロトコルに対して、および広範囲のデーターレートに対して、シリアル形式のデータをパラレル形式のデータに変換することが可能な、デシリアライザ回路網を提供する。

【解決手段】プログラマブルロジックデバイス(「PLD」)などの高速シリアルデータレシーバ回路網用のデシリアライザ回路網(10)は、シリアルデータを任意の複数のデータ幅を有するパラレルデータに変換するための回路網を含む。該回路網(10)はまた、広範囲の周波数の中の任意の周波数で動作可能である。該回路網(10)は様々な観点において構成可能/再構成可能であり、その構成/再構成の少なくとも1部分はダイナミックに(すなわち、PLDのユーザーモードオペレ−ションの間に)制御され得る。

(もっと読む)

半導体装置

【課題】 制御端子が浮遊状態になると、予期しないリーク電流などにより電極に電荷が蓄積され、電極の電位が変動し、スイッチが誤動作してしまう可能性がある。

【解決手段】 クーロン力により湾曲させることで第1の信号電極と第2の信号電極とを接触または分離することが可能な架橋部と、前記架橋部を制御するための制御端子とを有するスイッチ素子と、前記制御端子に接続された第1の不揮発性半導体素子と、前記制御端子および前記第1の不揮発性半導体素子に接続された第2の不揮発性半導体素子とを備える。

(もっと読む)

パワーグリッド最適化

【課題】導電材料の第1の層と導電材料の第2の層とを備える集積回路におけるグローバル電源配電網の最適化

をはかる。

【解決手段】パワーメッシュ配線を構成する、第1のレールは、(a)集積回路のコアロジックの1つ以上のコンポーネントに電源を供給し、(b)集積回路の第1の軸に対して位置合わせされ、(c)メッシュが第1の軸に沿って集積回路の境界から集積回路の中心に一様な電圧傾度を有するように構成される。また、第2のレールは、(a)コアロジックの1つ以上のコンポーネントに電源を供給し、(b)集積回路の第2の軸に対して位置合わせされ、(c)メッシュが第2の軸に沿って集積回路の境界から集積回路の中心に一様な電圧傾度を有するように構成された1つ以上のパラメータを有したものとする。

(もっと読む)

半導体装置及びその作製方法

【課題】書き込み電圧が小さいアンチヒューズを提供する。

【解決手段】アンチヒューズは読み出し専用の記憶装置のメモリ素子に用いられる。アンチヒューズは、第1導電層、絶縁層、半導体層、及び第2導電層を有する。アンチヒューズに含まれる絶縁層は、原料ガス中にアンモニアを添加して形成した酸化窒化シリコンであり、層中に1.2×1021以上3.4×1021atoms/cm3以下の水素、または3.2×1020以上2.2×1021atoms/cm3以下の窒素を含むことで、低電圧での書き込みが可能となる。

(もっと読む)

スイッチング素子、スイッチング素子の製造方法および半導体装置

【課題】 イオン伝導体を薄膜化することなくオン電圧を低減可能なスイッチング素子を提供する。

【解決手段】 本発明のスイッチング素子10は、金属イオンを伝導可能なイオン伝導体14と、前記イオン伝導体14に接して設けられた第1電極11と、前記イオン伝導体14に接して設けられた第2電極12とを含み、前記第1電極11が、前記イオン伝導体14に金属イオンを供給可能であり、前記第1電極11の前記イオン伝導体14と接する部分11aが、前記金属の酸化物、前記金属の水酸化物および前記金属の塩からなる群から選択される少なくとも一つを含むことを特徴とする。

(もっと読む)

集積回路における修復可能IO

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

ヒューズ回路

【課題】種々の半導体用途において使用されるヒューズ回路を提供する。

【解決手段】ヒューズ回路は、インタクト状態とブロー状態を有するヒューズを備える。上記ヒューズは、上記ヒューズにブロー電流を流すことにより、ブロー状態に切り換えられる。上記ヒューズは、第1のトランジスタと第2のトランジスタとの間に直列に接続される。上記第1のトランジスタおよび第2のトランジスタは、相補的なトランジスタであり、上記ヒューズを流れる静電放電電流を低減するように作動する。第1のトランジスタおよび第2のトランジスタは、ターンオンされて、上記ヒューズにブロー電流を流す。

(もっと読む)

マスクプログラム可能なロジックデバイスをプログラムする方法およびその方法によってプログラムされたデバイス

【課題】プログラム可能なロジックデバイスをプログラムする方法を提供すること。

【解決手段】マスクプログラム可能なロジックデバイス(MPLD)に対するユーザーのロジック設計は、互換性を有するユーザープログラム可能なロジックデバイス(UPLD)上で設計されMPLDに移行され得る、または直接MPLD上で設計され得る。設計がUPLD上でなされる場合には、目標のMPLDの制約(例えば、デバイスの間の差異)が考慮され、その結果、移行は成功する。設計が直接MPLD上でなされる場合には、その設計を試験のためにUPLDに移行することをユーザーが意図するときに、互換性を有するUPLDの制約が考慮される。これは、ロジック設計のUPLDとMPLDとの間で行き返りの移行が意図される場合にのみ、特徴の一致が使用され得ることを意味する。移行を助長するためにデバイスのペアの間の固定されたマッピングが生成され得る。

(もっと読む)

マスクプログラム可能なロジックデバイスをプログラムする方法およびその方法によってプログラムされたデバイス

【課題】プログラム可能なロジックデバイスをプログラムする方法を提供すること。

【解決手段】マスクプログラム可能なロジックデバイス(MPLD)に対するユーザーのロジック設計は、互換性を有するユーザープログラム可能なロジックデバイス(UPLD)上で設計されMPLDに移行され得る、または直接MPLD上で設計され得る。設計がUPLD上でなされる場合には、目標のMPLDの制約(例えば、デバイスの間の差異)が考慮され、その結果、移行は成功する。設計が直接MPLD上でなされる場合には、その設計を試験のためにUPLDに移行することをユーザーが意図するときに、互換性を有するUPLDの制約が考慮される。これは、ロジック設計のUPLDとMPLDとの間で行き返りの移行が意図される場合にのみ、特徴の一致が使用され得ることを意味する。移行を助長するためにデバイスのペアの間の固定されたマッピングが生成され得る。

(もっと読む)

プログラム可能高速入出力インターフェース

【課題】高速と低速の両方で柔軟な入出力を実現する方法および装置を提供すること。

【解決手段】高速入力、高速出力、中低速の入力、中低速の出力を有する入出力構造が提供される。入力回路と出力回路の一方が選択され、もう一方が選択解除される。高速入出力回路は、例えば制御ライン入力に対してクリア信号のみを有して比較的単純であり、集積回路のコア内部の低速回路構成にインターフェースすることができる。中低速入力および出力回路は、例えば制御ライン入力としてプリセット、イネーブルおよびクリアを有してより柔軟であり、JTAGバウンダリ・テストを支援することができる。これらの並列の高速回路および低速回路はユーザによって選択可能であり、したがって、アプリケーションの要件によって、入出力構造は速度と機能の間で最適化される。

(もっと読む)

動的、かつリアルタイムなディレイ特徴化、及び設定

ストラクチャードASICのようなマスクプログラム可能な集積回路でディレイチェーンがマスクプログラム可能なスイッチで設定されるディレイを提供する。ディレイチェーンは、入力を受け、マスクプログラムされたディレイをJTAG制御器の使用で無効化させる。これにより異なるディレイが試験可能となる。入力はヒューズブロックから供されても良く、この場合、ヒューズブロックが マスクプログラム可能なスイッチを無効化し、マスクでプログラミングの後のディレイ変更が可能となる。 (もっと読む)

回路における周波数性能を最適化する入力/出力モジュールのための装置および方法

回路は、回路と少なくとも1つの外部デバイスとの間で信号を送るように構成可能である信号パッドを有する、モジュールを含むことができる。モジュールはまた、信号パッド間に交互配置される、未使用パッドも有することができる。回路は、回路と少なくとも1つの外部デバイスとの間で可変信号を送るように構成可能である信号パッドを有する、モジュールを含むことができる。モジュールはまた、少なくとも1つの外部デバイスと回路との間で、実質的に一定の電圧を送るように構成可能である電圧パッドも有することができる。信号パッドは、電圧パッド間に交互配置することができる。これらの特徴の1つ以上を伴うモジュールは、ワイヤボンドパッケージおよびフリップチップパッケージの両方において、モジュール内での異なる入力/出力利用率の設定の融通性を伴って、理想的な性能を達成することができる。  (もっと読む)

(もっと読む)

設計支援プログラム、該プログラムを記録した記録媒体、設計支援装置、および設計支援方法

【課題】LSI設計の作業効率を向上させ、設計期間の短縮化を図ること。

【解決手段】設計対象回路100の中から、クロストーク解析によりクロストークエラーが発生している任意のエラー箇所E1〜Ejを特定する。つぎに、特定されたエラー箇所Eiの中から1対のエラーセグメントEi−1を特定する。このあと、エラーセグメントEi−1の配線構造を変更することで減少するクロストークノイズ値の減少量を見積もり、その見積もり結果に基づいて、エラーセグメントEi−1の配線構造を決定する。そして、エラーセグメントEi−1の配線構造を決定された配線構造に修正する。このように、クロストークノイズ値の減少量を考慮して配線構造を修正することにより、配線修正によるクロストークノイズ値の削減効果を向上させることができる。

(もっと読む)

半導体装置

【課題】配線層にスイッチ素子を有するプログラム可能な半導体装置の提供。

【解決手段】第1の配線層101の配線と第2の配線層102の配線を接続するビア103の内部、ビアの第1の配線との接触部、第2の配線との接触部のうちの少なくとも1つに、電解質材料104等導電率が可変の部材が配設され、ビア103は、第1の配線との接触部を第1の端子、第2の配線との接触部を第2の端子とする導電率が可変型のスイッチ素子又は可変抵抗素子として用いられ、スイッチ素子の導電率を変えることで、第1の

端子と第2の端子との接触部との接続状態を、短絡、開放、又はその中間状態に可変に設定自在とされる。金属イオンの酸化還元反応によって、第1の電極と第2の電極間の導電率が変化する2端子スイッチ素子を備え、第1の電極に接続された逆極性の第1、第2のトランジスタと、第2の電極に接続された逆極性の第3、第4のトランジスタを備えている。

(もっと読む)

情報処理システム、プログラマブル論理回路装置、配線方法、論理回路作成方法、及び、プログラム

【課題】時間パラメータを含む三次元に効率よく論理回路を配置できる情報処理システム、プログラマブル論理回路、及び、配線方法を提供する。

【解決手段】情報処理システムは、PLD(Programmable Logic Device)を備える。PLDは、モジュールを備える。モジュールは、複数の演算器エレメントを備える。情報処理システムは、二次元論理回路110を作成し、二次元論理回路110に基づいて仮想的な三次元論理回路120を作成する。PLDは、仮想的な三次元論理回路120を、時間パラメータを含む三次元論理回路として動的に再構成しながら、つまり、モジュールを論理回路A〜Dの順に再構成しながら、データ処理を行う。

(もっと読む)

1 - 20 / 71

[ Back to top ]