Fターム[5F064AA02]の内容

ICの設計・製造(配線設計等) (42,086) | ICの形式 (1,534) | カスタムIC (1,426) | セミカスタムIC (1,415)

Fターム[5F064AA02]の下位に属するFターム

マスタスライス、ゲートアレイ (136)

標準セル、スタンダードセル (922)

PLA (305)

Fターム[5F064AA02]に分類される特許

21 - 40 / 52

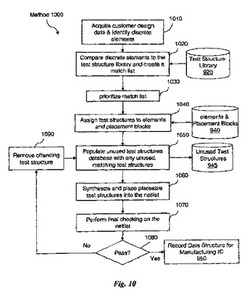

試験構造を集積回路に組み込むためのシステムおよび方法

【課題】 高い歩留まりを得ることができるように、カスタマイズされた回路を正確に試験するための手段を提供する。

【解決手段】 例えばASICのような集積回路においてデバイス固有の試験を実行しパラメータ・データを取得して、過剰な試験時間要件も、追加のシリコンも、特別な試験機器も必要とすることなく、各チップを個別に試験するためのシステムおよび方法(1000)が提供される。試験システムは、IC設計における未使用のバックフィル空間に組み込まれたデバイス試験構造(920)を含み、ICに含まれる選択された1組のデバイスと同一の1組のダミー・デバイス(940)を試験する。デバイス試験構造(920)は、カスタマ要件および設計要件(1010)に従って、ライブラリ(920)から選択される。選択された試験構造は、更に、優先度(1040)の順序で優先順位をつけて(1030)、設計内の設計要素に割り当てられる。配置アルゴリズム(1060)が、設計、レイアウト、および製造要件を用いて、選択した試験構造を、製造される設計(950)の最終レイアウトに配置する。

(もっと読む)

半導体装置

【課題】DRAMの自動配置配線化に当たり、レイアウト面積の増大を抑制できる半導体装置を提供する。

【解決手段】基板上に配置されてロジックとメモリとを構成する複数の素子と、前記複数の素子を接続する複数の配線37〜40と、前記複数の配線が配置される複数の配線層とを備え、前記複数の素子は、一方電極と他方電極とを持ち且つ前記一方電極の電位が固定された複数の遅延調整用素子22a〜22dを含み、前記複数の配線は、前記メモリで使用される内部クロックを伝達する信号配線と、前記複数の配線層の中の最上層において等間隔に引かれる仮想直線上に配置される複数の第1の配線を含み、前記複数の遅延調整用素子は、前記複数の第1の配線の中の一つを介して前記信号配線に前記他方電極を接続される。

(もっと読む)

互い違いにされた論理アレイブロックのアーキテクチャ

【課題】各論理アレイブロック(LAB)が、単一の伝導体チャンネルだけを使用して、または伝導体チャンネルを全く使用することなく、より多くの数の他のLABと通信することを可能にするアーキテクチャを提供すること。

【解決手段】集積回路(IC)デバイスであって、実質的に互いに整列された第1のグループの論理アレイブロックと、実質的に互いに整列され、かつ、複数の水平方向の伝導体および垂直方向の伝導体によって該第1のグループのLABに結合された第2のグループのLABとを備えており、該第1のグループおよび該第2のグループにおける各LABは、同じ数の論理要素(LE)を備えており、該第1のグループのLABは、実質的に、各LAB内のLEの数の半分だけ該第2のグループのLABからオフセットされている、集積回路(IC)デバイス。

(もっと読む)

電子ヒューズの最適フィールド・プログラミングを提供する方法。

【課題】 電子ヒューズの最適フィールド・プログラミング法を提供する。

【解決手段】 集積回路チップの顧客がフィールドにおいて、即ち製造テスト環境の外で、電子ヒューズをプログラミングすることができる最適ヒューズ・プログラミング条件を提供する方法が提供される。最適ヒューズ・プログラミング条件に関連付けられた最適ヒューズ・プログラミング識別子を、顧客のICチップ上の可読な形式で顧客に提供することができる。顧客のICチップ上の最適ヒューズ・プログラミング識別子にアクセスすることにより、顧客は1つ又は複数の関連付けられた最適ヒューズ・プログラミング条件に従ってフィールドにおいてヒューズ・プログラミング・プロセスを適用することができる。

(もっと読む)

データ生成方法、結線チェックシステム、およびデータ生成プログラム

【課題】プログラマブルデバイスの入出力ピンが多数ある場合にも、すべての入出力ピンの実際の機能に即して結線チェックを行うこと。

【解決手段】まず、ボード上に搭載される複数のFPGAそれぞれのピンに係るピン情報が取得される(ステップS101)。そして、結線チェックに関する設定情報が取得される(ステップS102)。ピン情報および設定情報が取得されると、データを出力し得るすべてのピンに対して、各ピンに固有の固有データが結線チェック用のデータとして付与される(ステップS103)。そして、固有データを含む入力ピン情報および出力ピン情報が生成され、これらの情報を記憶し、出力ピンと入力ピン間の結線をチェックするチェック回路が生成される(ステップS104)。そして、チェック回路に対応するROMデータが生成される(ステップS105)。

(もっと読む)

集積回路及びリコンフィギュラブル回路の入力データ制御方法

【課題】入力データをリコンフィギュラブル回路で確実に処理できるようにする。

【解決手段】本集積回路は、再構成可能に相互に結合される複数の演算器を含むリコンフィギュラブル回路3と、入力データ制御部4とを備える。そして、入力データ制御部4によって、リコンフィギュラブル回路3の構成に応じてデータが入力されるように入力データが制御される。

(もっと読む)

LSI品種決定方法、LSI設計支援方法、LSI品種決定プログラム、LSI設計支援プログラム、記録媒体、LSI品種決定装置およびLSI設計支援装置

【課題】LSIの製造途中において、中間製造物のトランジスタ性能を推定することにより、各中間製造物に合った適切な品種を決定し、LSI製造における歩留まりを向上させる。

【解決手段】ストラクチャードASIC製造時において、トランジスタ層またはトランジスタ層およびメタル1層が形成された中間製造物を製造後、当該中間製造物ごとのトランジスタ速度を測定し、この測定結果とトランジスタ速度に関連付けられた統計データとを用いて、トランジスタ速度の最大遅延推定値を算出する。そして、この算出結果に基づいて、LSIの品種リストの中から、ストラクチャードASICの品種を決定する。

(もっと読む)

半導体集積回路

【課題】基本構成単位となる回路セルの無駄を減らし、機能性を向上を図れ、回路サイズの増大を抑えることができる半導体集積回路を提供する。

【解決手段】回路セル100は、複数のセル入力信号に応じて、複数の選択入力信号から少なくとも一つの信号を選択する複数の他入力1出力マルチプレクサ121,122を有し、各マルチプレクサから選択信号をセル出力信号として出力する選択部120と、複数のテーブル部131,132を有し、各テーブルから論理機能に応じて、少なくとも一つのセル入力信号を含む複数の信号の何れか一つを複数のマルチプレクサごとに複数の選択入力信号それぞれに割り当てる割り当て部130と、選択部120の出力信号を一のセル入力信号F0に応じて出力する出力部140と、を含み、一のマルチプレクサ121は、セル入力信号F0に応じて前記選択入力信号の出力を停止可能な停止機能ENを有する。

(もっと読む)

三次元集積回路設計装置および三次元集積回路設計方法

【課題】設計コストと設計時間を節約しつつ、性能的に優れた三次元集積回路を設計する。

【解決手段】三次元集積回路設計装置は、半導体回路生成部1と、ネットリスト生成部2と、二次元レイアウトデータ生成部3と、三次元レイアウトデータ生成部4とを備えている。二次元レイアウトデータを複数のレイアウトブロックデータに分割して、そのうちの一部を裏表に反転して、複数の基板上に各レイアウトブロックデータを配置するため、二次元レイアウトデータをフルに利用して、二次元的な面積を大幅に削減可能な三次元集積回路を作製できる。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】半導体集積回路装置の開発期間を短縮すると共に、回路の高性能化かつ低コスト化を図る。

【解決手段】LSIコアとしてのRAM基板11A及びMPU基板11Bとパッケージング後に回路を特定できるFPGA基板12とには、各基板の主面上に、各集積回路に電気的に接続されているパッド51a,51b,52aがそれぞれ形成されている。半導体チップの張り合わせ技術を用いて、RAM基板11Aの主面11a及びMPU基板11Bの主面11bとFPGA基板12の主面12aとが、各パッド51a,51b,52aに、はんだ又は金等よりなるボール14をそれぞれ挟み、対向して接続されることにより、RAM、MPU及びFPGAはそれぞれ電気的に接続されている。

(もっと読む)

設計レイアウト内に充填型を挿入する方法と装置

設計レイアウト内に、充填型を挿入する方法および装置を説明する。回路設計レイアウト内の1つ以上のジョグエリアを識別する。引き続いて、回路設計レイアウト内に複数の充填型を挿入し、各充填型は、回路設計レイアウト内の対応するジョグエリアを無くすように構成されている。回路設計レイアウトに適用可能な少なくとも1つの予め定められた設計ルールに違反する、1つ以上の充填型を識別する。次に、予め定められた設計ルールに準拠するように、それらの充填型を適合させる。最後に、回路設計レイアウト内で、予め定められた設計ルールに準拠して、残りの充填型を組み合わせて、回路設計出力レイアウトを形成する。 (もっと読む)

半導体装置

【課題】チップサイズを縮小する。

【解決手段】マクロセルMC3上をX方向に延在するセル外配線をマクロセルMC3の信号用の端子Tsよりも上層の配線層で構成し、この端子Tsをセル外配線の複数のチャネル分を確保するように、Y方向(X方向に交差する方向)に延在させて構成する。マクロセルMC3と、セル外配線との接続をこの信号用の端子Tsを介して行う。

(もっと読む)

リコンフィギャラブルロジックブロック、リコンフィギャラブルロジックブロックを備えるプログラマブル論理回路装置、および、リコンフィギャラブルロジックブロックの構成方法

【課題】構成する回路に関わらずチップの高い面積効率を維持し、高速性および低消費電力化の両立を図る。

【解決手段】演算回路を構成する第1の回路211,212、および、該演算回路外の回路を構成する第2の回路213〜221を備えるリコンフィギャラブルロジックブロックであって、前記第1および第2の回路における所定の信号の設定を変化させることにより、異なる回路を構成する。

(もっと読む)

半導体集積回路

【課題】環状配線から電力の供給を受けるマクロセルを有し、消費電力を低減することが可能な半導体集積回路を提供する。

【解決手段】この半導体集積回路は、所定の機能を実現するためのマクロセルMC1と、マクロセルMC1を囲むように配置され、マクロセルMC1に接続された環状配線L1と、環状配線L1を囲むように配置され、電源電位VDDに接続された環状配線L2と、環状配線L2を囲むように配置され、電源電位VSSに接続されるとともにマクロセルMC1に接続された環状配線L3と、制御信号に従って環状電源L1と環状電源L2との間又は環状配線L1と環状配線L3との間を接続するためのスイッチ回路としてのCMOSインバータINV1,INV2とを具備する。

(もっと読む)

FPGA及びASICのネットリストを生成する方法

【課題】ASICとFPGAの設計品質を確保するとともに開発期間を短縮すること。

【解決手段】回路アーキテクチャ検討結果であり論理設計ドキュメントの一部であるブロックのポート仕様の接続情報のみを用いてデバイス・テクノロジに依存しないブロックのポートとポート間を結ぶネットからなるコア(論理コア)と呼ぶネットリストを生成し、コア(論理コア)から対象ブロックを選択、グループ化し、グループ化したコア(論理コア)のデータを使用する集積回路の開発方法。

(もっと読む)

構造化されたASICデバイスのためのクロック信号ネットワーク

【課題】クロック信号の好適な分配を行うことができる構造化されたASICデバイスを提供する。

【解決手段】構造化されたASIC(10)デバイスのクロック分配回路構成(200)は、決定性(deterministic)の部分および複数の設定可能な部分を含む。その決定性の部分は、コンダクタ(40)セグメントの所定の配置を用い、デバイス上の複数の所定のロケーションへ、クロック信号を分配するために、回路をバッファする。それぞれの所定のロケーションから、クロック分配回路構成の関連される設定可能な部分は、そのクロック信号を、その所定のロケーションから提供された、構造化されたASIC(10)の所定の領域においてそのクロック信号を必要とする任意のクロック利用回路構成に分配する。

(もっと読む)

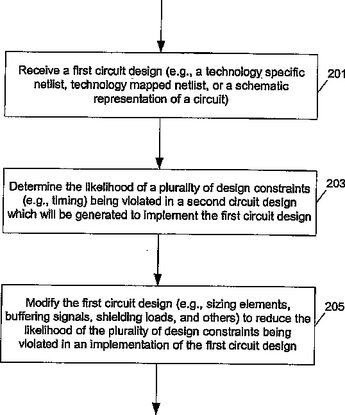

自動回路設計のための方法および装置

回路のその後の実装(例えば、配置と配線)で発生しうる逸脱に関する設計パラメータの感度に応じて回路設計(例えば、合成ソリューション)を自動的に修正する方法と装置を提供する。本発明の一態様では、回路を設計する方法は、第1の回路設計(例えば、配置ソリューションがある場合またはない場合の技術特有のネットリスト)の実装で設計制約条件に違反する可能性を判定することと第1の回路設計を修正して設計制約条件に違反する可能性を低減することとを含む。一例では、第1の回路設計の実装は、第1の回路設計を実装する配線ソリューションを含み、第1の回路は、論理素子のインスタンスのサイズ設定、信号のバッファリング、信号の負荷遮蔽、またはその他のオペレーションを通じて修正される。  (もっと読む)

(もっと読む)

等価なフィールドプログラマブルゲートアレイとストラクチャード特定用途向け集積回路の製造方法

【課題】機能的に等価なフィールドプログラマブルゲートアレイ(“FPGA”)およびストラクチャード特定用途向け集積回路(“ストラクチャードASIC”)を生成することが可能なコンパイラフローを提供する。

【解決手段】該フローはいずれか一方のフロー時にその後のもう一方のフローのパフォーマンスに同じ変換を必ず含むように実行される設計変換をフィードバックするステップを含み、それにより機能等価性を実現することが可能となる。該フローは、その機能等価性が実現していることを証明するために、中間結果を比較するステップを含むことも可能である。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】集積度を向上でき、光近接効果補正の均一化を図る半導体集積回路装置およびその製造方法を提供する。

【解決手段】半導体集積回路装置は、半導体基板中に設けられた第1導電型のウェルの論理回路構成領域中にアレイ状に配置され、それぞれが前記ウェル上に設けられたゲート電極と前記ウェル中に前記ゲート電極を挟むように隔離して設けられソース/ドレインとして働く第2導電型の第1拡散層とを備えたセル(BC)と、前記論理回路構成領域の空き領域中に配置され、それぞれが前記ウェル上に設けられ前記ゲート電極と同一のパターン形状の導電層と前記第1拡散層と同一のパターン形状であって前記ウェル中に前記導電層を挟むように隔離して設けられ前記ウェルと電気的に接続される第1導電型の第2拡散層とを備えたサブ領域(sub領域<01>)を具備する。

(もっと読む)

半導体集積回路

【課題】配線経路に挿入されるビヤの数を低減することができる半導体集積回路を提供する。

【解決手段】配線群LA1およびLB1の重なり部分または配線群LA2およびLB2の重なり部分にビヤを1つ形成することによって、配線群1つ分の長さだけ行方向または列方向に配線経路を伸ばすことができる。そのため、行方向または列方向に配線経路を伸ばすために複数のビヤを必要とする従来の配線構造に比べて、配線経路に挿入されるビヤの数を減らすことができる。

(もっと読む)

21 - 40 / 52

[ Back to top ]