Fターム[5F064BB04]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082) | デジタル信号処理 (4,646) | 論理ゲート (2,166) | オア (198)

Fターム[5F064BB04]に分類される特許

1 - 20 / 198

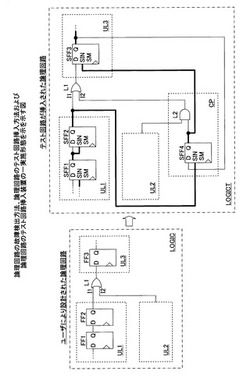

論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

配置配線装置

【課題】改訂期間の短縮およびマスク改定費用の削減を図ることが可能な配置配線装置を提供すること。

【解決手段】比較部32は、既存ネットおよび改訂情報から論理の改訂箇所を特定し、論理を合わせるための論理接続情報を抽出する。判定部33は、レイアウト情報および比較部によって抽出された論理接続情報に基づいて、メタル層の最上位層から順に配線の繋ぎ換えの可否を判定する。そして、置換部34は、判定部33によって繋ぎ換えが可能と判定されたメタル層において配線の繋ぎ換えを行なう。したがって、上位層のみの改訂によって改訂期間の短縮およびマスク改定費用の削減を図ることが可能となる。

(もっと読む)

ネットリスト変換装置、論理合成装置及びコンピュータプログラム

【課題】半導体集積回路の開発期間を短縮し、且つ、レイアウトエラー確率を低減する。

【解決手段】本発明の実施形態のネットリスト変換装置は、半導体集積回路を構成する複数のセルであって、第1遅延時間だけスキャン用データ信号を遅延させる第1スキャンフリップフロップを含む複数のセルの接続関係を示すネットリストを変換する。そのようなネットリスト変換装置は、論理ライブラリ30と、ネットリスト変換部18と、を備える。論理ライブラリ30は、半導体集積回路を構成する複数のセルの論理的機能を示す情報を含むセル論理情報であって、第1スキャンフリップフロップの論理的機能を示す情報と、第1遅延時間より大きいスキャン用第2遅延時間だけデータ信号を遅延させる第2スキャンフリップフロップの論理的機能を示す情報と、を含むセル論理情報を記憶する。ネットリスト変換部18は、セル論理情報を参照して、ネットリストの第1スキャンフリップフロップを第2スキャンフリップフロップに置換する。

(もっと読む)

半導体集積回路,および,半導体集積回路の検査方法

【課題】故障検査のために観測用フリップフロップ回路を配置することなく,故障検査を可能とする半導体集積回路,その検査方法を提供する。

【解決手段】第2の論理回路51の試験の際に試験モードを示す制御信号TSMが,故障検査用回路41に入力され,この試験モードに対応するテスト値が,論理回路51に入力されると,故障検査用回路41により,論理回路51の出力論理が,論理回路13に対応するフリップフロップ回路14に入力される。さらに,通常モード時に,論理回路13の出力論理が,故障検査用回路41により,論理回路13に対応するフリップフロップ回路14にそのまま入力される。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップ面積の増大を抑制しつつ、ダミー配線パターンの配置にかかる工数を低減する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、レイアウト領域に対して、半導体集積回路の配置配線(S1)を行った後、レイアウト領域に配置されているバルクセルを抽出し(S2)、レイアウト領域において、抽出したバルクセルの周囲に、所定の大きさを備える空き配線領域が存在するかどうかを検索し(S3)、検索の結果、所定の大きさを備える空き配線領域を検出した場合、抽出したバルクセルの座標を基準にして、検出した空き配線領域にダミー配線パターンを配置(S4)する。

(もっと読む)

クロックツリー生成方法、クロックツリー生成プログラム、記録媒体、およびクロックツリー生成装置

【課題】外部電源電圧が変動した場合でも、安定に動作する半導体装置を実現することが可能なクロックツリー生成方法を提供する。

【解決手段】プログラム5のCTS部8は、電源領域Aから電源領域Bにクロック信号CLK1,CLK2を伝達する経路L1,L2を設け、電源領域A内の経路L1,L2にそれぞれアンカーバッファB1,B2を配置し、遅延回路D1,D2を電源領域B内の経路L1,L2にそれぞれ配置し、遅延回路D3,D4をアンカーバッファB1,B2の入力ノード側の経路L1,L2にそれぞれ配置する。したがって、外部電源電圧VDD1,VDD2が変動した場合でも、クロック信号CLK1,CLK2の遅延時間は同じになる。

(もっと読む)

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

可変遅延回路およびその制御方法

【課題】信号の遅延量を微調整可能な可変遅延回路を提供する。

【解決手段】可変遅延回路において、N個の可変論理回路を用いてN段のセレクタが直列接続される。1段目のセレクタSL1の2つの入力端子に信号が入力される際、入力信号が通過する2つの信号経路D1には経路差d1が存在している。また、2段目のセレクタSL2の2つの入力端子に信号が入力される際、入力信号が通過する2つの信号経路D2には、経路差d2が存在している。信号が通過する当該経路の組み合わせは、セレクタSLの段数に基づき、N段であるため2nとおりの信号経路の組み合わせが生じる。すなわち、2nとおりの切替信号R1〜Rnの組み合わせに基づいて2nとおりの信号経路が選択される。2nとおりの信号経路の組み合わせに基づく配線経路差に基づいて信号遅延量を調節する。

(もっと読む)

半導体集積回路の設計方法及び半導体集積回路の設計支援装置

【課題】論理回路の面積縮小化を実現しつつ、設計TATの短縮を可能とする技術を提供する。

【解決手段】複合論理マクロセルを、基本マクロセルに置き換えて面積の総和を抽出し、その面積の総和と複合論理マクロセルの面積とを比較して面積縮小化に有効となる複合論理マクロセルを選択する。その選択された複合論理マクロセルにフラグを設定する。フラグを設定したマクロセルと同等の論理を論理情報から検索する論理構造検索処理を行い、置換対象となる基本マクロセルにフラグを設定する。置換対象のフラグを設定した基本マクロセルを、フラグ設定した複合論理マクロセルに置き換える等価論理置換処理を行う。

(もっと読む)

半導体装置

【課題】タイミングエラーに起因する動作不良を低減した半導体装置の実現。

【解決手段】組合せ回路11A-11Cと、クロックCLKに応じて、組合せ回路が出力するデータを取り込んで保持する1個以上の記憶素子2A-2Dと、クロックを供給するクロック信号線3と、を備え、少なくとも1個の記憶素子は、記憶素子に供給するクロックを遅延させ、遅延時間が可変の少なくとも1個の可変遅延素子11A,11Bを、備え、可変遅延素子が出力する遅延クロックに応じて、当該記憶素子が正常に動作するか否かを検出し、正常に動作するか否かの検出結果に応じて可変遅延素子の遅延時間を変化させるタイミングエラー検出機能付き記憶素子である半導体装置。

(もっと読む)

論理シミュレーション方法および論理シミュレーション装置

【課題】論理シミュレーションに要する時間を削減する。

【解決手段】RTL記述の論理シミュレーション結果とゲートレベルの論理シミュレーション結果とが一致しているか否かを判定する。そして、判定結果が不一致であった場合に、RTL記述の論理シミュレーション結果情報とゲートレベルの論理シミュレーション結果情報の不一致箇所を抽出する。抽出した不一致ポイントに基づき、ゲートレベルの論理シミュレーション結果情報をRTL記述の論理シミュレーション結果情報に強制代入記述を作成する。その強制代入記述を含むForceファイルに基づき再度ゲートレベルの論理シミュレーションを実施する。

(もっと読む)

プログラマブル・ゲートアレイ部を備えたマスクプログラマブル論理装置

【課題】プログラマブルゲートアレイ部を備えるマスクプログラマブル論理装置を提供すること。

【解決手段】集積回路の基板上に配置される複数のマスク−プログラマブル領域と、上記マスク−プログラマブル領域に結合されると共に上記マスク−プログラマブル領域を相互接続するために基板上に配置される複数の相互接続導体と、基板上に配置される複数のゲートアレイ部とからなり、ゲートアレイ部はマスクプログラマブル論理装置上の回路設計の実行を促進する少なくとも一つの機能を達成するようにプログラム可能である集積回路上に配置されるマスク−プログラマブル論理装置。

(もっと読む)

貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法

【課題】貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法を提供する。

【解決手段】複数の半導体レイヤ間で伝送される情報の衝突を防止する構造を有する半導体装置であり、該半導体装置は、第1温度情報を出力する第1温度センサ回路を含む少なくとも1つの第1半導体チップと、貫通電極に電気的に連結されずに、第1温度センサ回路に電気的に連結される第1バンプと、第1半導体チップの貫通電極に電気的に連結される第2バンプと、を具備する半導体装置であることを特徴とする。

(もっと読む)

リコンフィギュラブルロジック装置

【課題】セット全体のコストダウンや小型化、ないしは、起動時間の短縮を実現することが可能なリコンフィギュラブルロジック装置を提供する。

【解決手段】リコンフィギュラブルロジック装置において、ルックアップテーブル11は、コンフィギュレーションデータを不揮発的に記憶する手段として、強誘電体素子のヒステリシス特性を利用した不揮発性フリップフロップFFを有する。コンフィギュレーションデータは、ルックアップテーブル11に任意の入出力論理値表を実装するための設定データであり、プログラミングによって設定される。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

1 - 20 / 198

[ Back to top ]