Fターム[5F064CC01]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | トランジスタ (1,639)

Fターム[5F064CC01]の下位に属するFターム

バイポーラトランジスタ (85)

FET (1,516)

bi−MOS (5)

Fターム[5F064CC01]に分類される特許

1 - 20 / 33

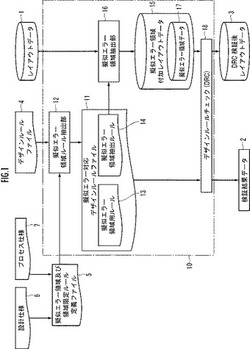

レイアウト検証装置及びレイアウト検証方法

【課題】汎用性が高く、効率的に検証処理を行うことができるレイアウト検証技術を提供する。

【解決手段】レイアウトデータがデザインルールに反するか否かの検証を行うに際し、所定の設計値に基づき、レイアウトデータ(1)を、擬似エラー領域内のものとそれ以外のものとに区分し、通常のデザインルール(4)からの許容範囲内のものとして擬似エラー領域用のデザインルール(13)を作成し、擬似エラー領域外のレイアウトデータについては通常のデザインルールで検証を行い、擬似エラー領域内のレイアウトデータについては擬似エラー領域用のデザインルールで検証を行う。

(もっと読む)

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

半導体集積回路のレイアウト設計装置、レイアウト設計方法及びレイアウト設計プログラム並びに半導体集積回路装置の製造方法

【課題】半導体集積回路の設計TATの増大を防止する。

【解決手段】レイアウト設計装置は、パッケージに起因して半導体チップに加わるパッケージ応力の応力値の分布を示す応力分布データを読み込む応力分布データ読込み手段3と、半導体チップのチップレイアウトデータから素子レイアウトデータを抽出する素子レイアウトデータ獲得手段7と、半導体チップに搭載される各素子について応力値と素子の特性変動の関係を示した検量線データを保持する検量線データ保持部9と、応力分布データ、素子レイアウトデータ及び検量線データに基づいて各素子についてパッケージ応力による素子特性変動を算出する素子特性変動計算手段11と、素子特性変動を打ち消すように素子レイアウトデータを補正する素子レイアウト補正手段13と、補正後素子レイアウトデータを用いてチップレイアウトデータを補正するチップレイアウト補正手段と、を備えている。

(もっと読む)

半導体評価回路

【課題】不良トランジスタの検出と、不良トランジスタのトランジスタ特性の測定を高速で行うことができる、大規模な半導体評価回路(DMA−TEG等)を提供する。

【解決手段】本発明の半導体評価回路においては、評価セルアレイ中の測定対象トランジスタの閾値Vthの電圧が、閾値Vth電圧の正規分布曲線に対して、例えば、5σ(σは標準偏差)以内の分布から外れたものを選別する。そして、閾値Vthの電圧が5σ以内の分布から外れた測定対象トランジスタに対して、トランジスタ特性の測定を行う。

(もっと読む)

レイアウト設計方法および半導体集積回路

【課題】パッド律則とコア律則を意識しないレイアウト設計を容易に実現し、半導体集積回路の面積の縮小化とコストの低減化を図ること。

【解決手段】レイアウト設計装置300は、設計対象回路の回路情報の入力を入力部301により受け付け、入力された回路情報に含まれているコアの領域が確保された設計対象回路のレイアウト情報を生成部302が生成する。生成されたレイアウト情報上のコアの領域以外の領域に、回路情報に含まれているI/O回路をレイアウト部303により配置および配線する。回路情報に含まれているパッドの配置可能領域を決定部308により作成したレイアウト情報上に決定する。必要配置数分のパッドの総面積が配置可能領域の面積を超えない最大の大きさに、パッドの面積を最適化部309により最適化する。最適化されたパッドを配置部310により配置可能領域に配置する。

(もっと読む)

半導体集積回路のレイアウト装置及びレイアウト方法

【課題】レイアウト修正を必要としないでメタル密度を均一化し、レイアウト修正を必要としないでダミーメタルを配置する半導体集積回路のレイアウト方法を提供する。

【解決手段】半導体集積回路のレイアウト方法は、フロアプラン時に所定のメタル密度となるように所定の寸法X×X及び間隔2Xでダミーパターン1を第1領域に配置するステップと、第1領域にタイミング解析をしながらタイミング制約を満たすように論理回路セルを配置し配線を行うステップと、論理回路セルを配置し配線を行うことで生成されるレイアウトパターンが規格を満足しているか検証するステップとを具備する。

(もっと読む)

動的アレイアーキテクチャにおけるセル位相整合及び配置の方法及びその実施

半導体チップは、レイアウト特徴部が第1の仮想格子に従って配置される第1のチップレベルと、レイアウト特徴部が第2の仮想格子に従って配置される第2のチップレベルとを有する論理ブロック区域を含むように定められる。第1の仮想格子と第2の仮想格子の間には、有理空間的関係が存在する。論理ブロック区域内には、複数のセルが配置される。複数のセルの各々は、複数のセル位相のうちの適切な1つに従って定められる。複数のセル位相のうちの適切な1つは、所定の配置セルの第1及び第2のチップレベル内のレイアウト特徴部を所定の配置セルに位置決めされた第1及び第2の仮想格子と整合させる。 (もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】回路動作の信頼性向上および設計期間の短縮化を図ること。

【解決手段】設計対象回路の配線領域内の各ネットグループ固有の始点座標から終点座標に辿り着くまでの各ネットグループ固有の配線幅の配線経路を探索する。そして、探索された配線経路間で相互に交差関係を有するネットグループの組み合わせを検出し、検出された組み合わせのネットグループがそれぞれ異なる配線層に割り当てられるように、設計対象回路に与えられた複数の配線層の中から各ネットグループに割り当てる配線層を決定し、決定された決定結果を出力する。

(もっと読む)

半導体集積回路のレイアウト作成装置及びレイアウト作成方法

【課題】多層構造の半導体装置を製造する製造プロセスに基づいて、複数層のレイアウトデータを検証するレイアウト検証処理のプロセスを適宜変更し、レイアウト検証処理の負担を軽減し、レイアウトデータの品質を向上させる半導体集積回路のレイアウト作成装置及びレイアウト作成方法を提供する。

【解決手段】半導体集積回路のレイアウト作成装置は、論理回路図設計部と、レイアウトデータ作成部と、論理接続検証部と、デザインルール検証部と、層間レイアウト検証部と、レイアウトデータを出力するデータ出力部と、多層構造の前記半導体集積回路をチップ化する際の製造プロセスに基づいて、前記論理接続検証部、前記デザインルール検証部、及び前記層間レイアウト検証部において実行される検証処理のプロセスを設定する検証プロセス設定部と、を備える。

(もっと読む)

半導体装置

【課題】ディッシングを抑制する。

【解決手段】半導体装置は、複数の銅配線層と複数の絶縁層が交互に積層されて構成される。低インピーダンス配線は、所定の領域を占有して形成される。第1配線群は、第1の銅配線層に所定の間隔d1を空けて並列に敷設され、第1の方向に延伸する短冊状の複数の銅配線Lc1を含む。第2配線群は、第1の銅配線層と隣接する第2の銅配線層に、所定の間隔d2を空けて並列に敷設され、第1の方向と垂直な第2の方向に延伸する短冊状の複数の銅配線Lc2を含む。第1配線群が占める領域RGN1と、第2配線群が占める領域RGN2と、所定の領域は、少なくとも部分的にオーバーラップする。第1配線群Lc1と第2配線群Lc2は、等電位となるように電気的に接続される。

(もっと読む)

半導体集積回路の自動遅延調整方法

【課題】マニュアルによる方法に比べて、汎用性に優れていること。

【解決手段】コンピュータ1は、レイアウトデータ7にダミー配線50−Jを追加する処理(S2)と、レイアウトデータ7中でタイミング違反であるセル30−1とセル30−2間の対象配線40にダミー配線50−Jを接続する処理(S4)とを実行する。処理(S4)において、コンピュータ1は、ダミー配線50−Jを、ダミー配線50−Jの両端部に対応するピン61、62を有するダミー配線セル60に置き換え(S12)、対象配線40を切断して、対象配線41、42を生成し(S13)、対象配線41、42をピン61、62にそれぞれ接続し(S14〜S16)、ダミー配線セル60をダミー配線50−Jに置き換えて、対象配線40の切断部分にダミー配線50−Jが接続された配線とする(S17)。

(もっと読む)

半導体素子及びその製造方法、並びに半導体素子を備えるスタックモジュール、カード及びシステム

【課題】集積度を低下させずに、信頼性あるように積層することができる半体素子が提供され、かような半導体素子を備えるスタックモジュール、カード及びシステムを提供する。

【解決手段】半導体素子100は基板105を備え、回路110は基板上に提供される。一つ以上のパッド120は、回路のテストのために基板上に提供される。一つ以上のターミナル135は、回路にアクセスするために基板上に提供される。一本以上の第1配線ライン140は、一つ以上のパッド及び回路を電気的に接続する。一本以上の第2配線ライン145は、一つ以上のターミナル及び回路を電気的に接続する。そして、スイッチング素子150aは、一本以上の第1配線ラインの中間に挿入され、一つ以上のパッド及び回路の電気的な接続を制御する。

(もっと読む)

半導体集積回路の設計方法

【課題】従来の設計フローでは、レイアウト設計後に寄生素子抽出(LPE)を行い、LPE後のネットリストに対しEM検証を実施し、EM規格値違反が発生した場合、手作業または自動化手法によるレイアウト修正が行われ、再度LPEからEM検証を実施し、EMエラーが無くなるまで続けるため、多大な設計工数がかかる。

【解決手段】回路設計用とレイアウト設計用とで関連する複数の配線情報パラメータを保持した配線マクロセル群からなる配線マクロセルライブラリE1を用いることを特徴にし、回路設計工程S10では対象ネットに配線マクロセル(回路シンボル)を挿入する処理を有し、レイアウト設計工程S30では回路シミュレーション工程S20によって得られる対象ネットの回路シミュレーション結果E5とエレクトロマイグレーション(EM)を考慮するための設計条件などの設計制約E3とを入力として対象ネットの配線マクロセル(レイアウトパターン)を選択する処理を有している。

(もっと読む)

半導体チップ及びその位置合わせ方法

【課題】半導体チップの微細化・高集積化に好適なアライメントマークを有する半導体チップ及びその位置合わせ方法を提供することを目的とする。

【解決手段】半導体基板2上に、トランジスタ等の素子から成る集積回路3と、当該集積回路3と電気的に接続されたパッド電極4が形成されている。各集積回路3同士、あるいは集積回路3とパッド電極4とを電気的に接続する配線層5が形成されている。配線層5は、半導体基板2の各辺に対して傾斜した傾斜部6を有する。傾斜部6は、位置合わせの際に半導体チップ1の位置を認識するためのアライメントマークとして機能する。このような半導体チップ1は、例えば以下に示すようにして目的の位置に実装される。まず、半導体チップ1を保持し傾斜部6の位置を認識装置を用いて光学的に検出する。そして、当該検出結果に基づいて、半導体チップ1を目的の位置に合わせる。

(もっと読む)

パターン作成方法、パターン検証方法、パターン作成・検証プログラム、および半導体装置の製造方法

【課題】パターンの設計データの作成および修正を、半導体装置の製造プロセスやパターン設計プロセス上の要請に沿って効率良く、かつ、均一に行うことができるパターン作成方法を提供する。

【解決手段】半導体装置内に形成されるパターンの設計データのうち第1のデザインルール1によるチェックが済んだデータを修正指針5に基づいて修正し、再び第1のデザインルールチェックにかける。ルール1に違反していないデータをパターン作成用設計データとして出力するとともにルール1に違反しているデータをルール1よりも許容範囲の広い第2のデザインルール4によるチェックにかける。ルール4に違反していないデータをパターン作成用設計データとして出力するとともに、ルール4に違反しているデータをルール4を満足するように設計し直すか、ルール4に違反しているデータがルール4を満足するように修正指針5を調整する。

(もっと読む)

半導体装置

【課題】共用層にカスタマイズ層が積層されている構造で、容量素子や抵抗素子を自在に形成できて生産性が良好な半導体装置を提供する。

【解決手段】下部電極151と誘電体膜152と上部電極153とが積層されている構造の複数の積層体150がカスタマイズ層120に形成されている。機器メーカなどの中間ユーザの要求に対応してカスタマイズ層120に配線130などを形成するとき、積層体150に対する配線130の接続構造を相違させることにより、容量素子140や抵抗素子141〜144が形成される。このため、共通の積層体150から容量素子140や抵抗素子141〜144を自在に形成できて生産性が良好な構造を提供することができる。

(もっと読む)

集積回路装置及び電子機器

【課題】回路面積の縮小を実現できる集積回路装置、電子機器の提供。

【解決手段】集積回路装置はデータドライバブロックDBとメモリブロックMBとロジック回路ブロックLBを含む。データドライバブロックDBはデータドライバDRと、ロジック回路ブロックLBからのドライバ制御信号をバッファリングしてデータドライバDRに出力するバッファ回路BFを含む。メモリブロックMBは、メモリセルアレイMAと、ワード線の選択を行うローアドレスデコーダRDを含む。データドライバブロックDBとメモリブロックMBはD1方向に沿って配置され、バッファ回路BFとデータドライバDRはD2方向に沿って配置され、ローアドレスデコーダRDとメモリセルアレイMAはD2方向に沿って配置され、バッファ回路BFとローアドレスデコーダRDはD1方向に沿って配置される。

(もっと読む)

金属エレクトロマイグレーション設計を有するRFパワートランジスタデバイス、及びその製造方法

メタル構造(70)を具備したRFパワートランジスタは、ドレインパッド(72)、及びドレインパッドから延在する複数の金属ドレインフィンガー(74)を有する。少なくとも1つの金属ドレインフィンガーは1つ以上の金属区画(74−1、74−2、100−1、100−2、100−3)を有し、各金属区画は、バンブーレジーム内に維持された金属幅を有する1つ以上の金属ブランチ(54−1、54−2、116−1、116−2、116−11、116−21、116−41)を含む。

(もっと読む)

(もっと読む)

半導体装置

【課題】圧接時のバランスを保つために補強用のダミー端子を設けたとしても、チップ上により多くの回路素子を設けることができるようにすること。

【解決手段】COG実装に用いられる半導体装置10であって、チップの一の端部の近傍に第1のパターンで配置された出力端子群12fと、チップの一の端部の近傍であって出力端子群12fが配置された領域とは別の領域に配置されるとともに、第1のパターンと異なる第2のパターンで配置されたダミー端子12dと、を備える。第2のパターンは、第1のパターンよりも幅が狭く構成される。ダミー端子12dの近傍であって出力端子群12fの長さ方向の隣に電源部14が配される。

(もっと読む)

半導体集積回路設計方法及び装置

【課題】半導体集積回路の設計において、電圧降下に関連する回路安定性や歩留まりを確保するための再設計や長時間を要する設計工程の繰り返しの試行回数を低減する。

【解決手段】半導体集積回路設計方法において、取得可能な情報の範囲内で解析対象の電源モデルを選定し(S101)、チップレベルあるいは下位モジュールレベルの初期配置を仮定して作成した電圧降下傾向の情報を作成し(S102)、この情報をもとに、設計初期に決まってくる電圧降下傾向に対応したセル、マクロ及びトランジスタの密度分布を見積もる(S103)。そして、配置密度分布情報を定量的設計情報として設計に盛り込む(S104)。

(もっと読む)

1 - 20 / 33

[ Back to top ]