Fターム[5F064CC23]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | コンデンサ、キャパシタ (371)

Fターム[5F064CC23]に分類される特許

361 - 371 / 371

ネットリスト作成装置

【課題】 寄生RCの抽出の容易化を図るとともに、回路シミュレーションの解析精度を高める。

【解決手段】 トップ階層のブロック内の電源配線及びグランド配線を示すアブストラクトが適用されたレイアウトデータZから配線の寄生RCを抽出し、その抽出結果をネットリストCに適用するとともに、その寄生RCのノードのレイアウトデータ上の座標情報を特定する一方、座標ファイルF1に格納された回路素子の端子のレイアウトデータ上の座標情報と寄生RCのノードのレイアウトデータ上の座標情報とを比較して、その寄生RCの抽出結果が適用されたネットリストEにおける回路素子と寄生RCの接続関係を適正化する。

(もっと読む)

半導体集積回路の動作検証システム及びその動作検証方法

【課題】 動作検証内容に応じた特性ライブラリを作成することにより高精度の動作検証ができる半導体集積回路の動作検証システム及び動作検証方法を提供する。

【解決手段】回路セル設計レイアウト情報を入力して、仕上がりレイアウトを予測し、ネットリスタ8を用いて、仕上がり予測レイアウト情報に基づいてネットリスト変換を行ない、消費電力についての動作検証に用いる第1ネットリスト4aと、遅延についての動作検証に用いる第2ネットリスト4bと、容量についての動作検証に用いる第3ネットリスト4cとを作成する。回路シミュレータ9により、各ネットリスト4a,4b,4cを用いて、動作検証を行なった結果は、第1〜第3特性ライブラリ5〜7に格納される。

(もっと読む)

シングルイベントアップセットに対する抵抗力を増加する集積回路構造

フィールドプログラマブルゲートアレイ(「FPGA」)の集積回路(「IC」)デバイスのコンフィギュレーション・メモリセル(「CRAM」)は、シングルイベントアップセット(「SEU」)に対する増加された抵抗力を与えられる。CRAMの入力ノードのゲート構造の一部分は、そのゲート構造の残りの部分の名目上のサイズに対して、サイズが増加される。拡大されたゲート構造の部位はICのNウェル領域に容量的に近くに配置され、別の部位はICのPウェル領域に容量的に近くに配置される。この配置は、その入力ノードのロジックレベルに関係なく、その入力ノードに、SEUに抵抗するための増加された静電容量を与える。本発明はまた、SEUへの抵抗力を増加させることが所望される任意のタイプのメモリセルの任意のノードに対しても応用可能である。  (もっと読む)

(もっと読む)

半導体装置

【課題】 アナログ回路とデジタル回路が搭載されるシステムLSIにおいて、アナログ回路へのデジタル電源ノイズの影響による特性劣化、及びパッド数増加によるチップサイズの増大問題を解消するこのできる半導体装置を提供する。

【解決手段】 半導体チップに搭載されたアナログ回路内のデジタル電源電圧及び接地電圧供給と、該アナログ回路内のアナログ電源電圧及び接地電圧供給を分離するために、半導体チップ上の外周部にアナログ回路内のアナログ電源電圧及び接地電圧供給用パッドと、半導体チップ内部にアナログ回路に隣接してアナログ回路内のデジタル電源電圧及び接地電圧供給用パッドとを設け、さらに、アナログ回路に隣接したデジタル電源電圧及び接地電圧供給用パッドを接続する多層配線を用いて容量セルを生成する構成とした。

(もっと読む)

静電放電保護回路

プログラム可能なポリシリコンフューズのような繊細な回路を有する集積回路が提供される。静電放電イベントの存在下において、繊細な回路がダメージと望ましくないプログラミングとを被らないように保護する静電放電(ESD)保護回路が提供される。静電放電保護回路は、ESD信号にさらされたときに、繊細な回路にわたる電圧レベルを最大電圧に制限し、繊細な回路から離れて電流を汲み上げる電力ESDデバイスを有し得る。静電放電保護回路はまた、最大電圧が繊細な回路にわたって印加されたときに電流が繊細な回路を流れないようにするのに役立つESDマージン回路をも含み得る。  (もっと読む)

(もっと読む)

電子回路の設計方法および装置

アナログおよび混成信号回路を含む、電子回路を設計する方法および装置であって、実施形態の一例では、階層的設計およびサイジング・フローを、1つ以上の評価モデル(例えば、性能および実現可能性モデル)と共に用いて、あるレベルにおいて得られた結果が階層の他のレベルでも有効であり関連性を保つようにする。別の態様では、例えば、階層の種々のレベルと関連付けられた1つ以上の既存の性能モデルに基づいて性能を評価する後処理ステップによって、設計の歩留まりを考慮して階層的サイジングを実行する。これらの方法はコンピュータ・プログラムにて具体化され、このプログラムを実行するように適合化されたコンピュータ・システムにて実行される。 (もっと読む)

単一ポリ・2−トランジスタベースのヒューズ素子

ポリシリコンの単一層内に配置されたダブルゲート構造を有した、電気的にプログラム可能なトランジスタヒューズ(200)。このトランジスタヒューズ(200)では、第1のゲート(216)は、ソース領域(210)の一部と重なり合うように配置されていて、第2のゲート(215)は、第1のゲート(216)からは絶縁されていると共に、ドレイン領域(211)の一部と重なり合うように配置されている。第1のゲート(216)は、外部から供給されたコントロール信号を入力するための端子を有しており、第2のゲート(215)は、ドレイン領域(211)に容量結合されている。第2のゲート(215)は、第2のゲート(215)の容量結合を大きくするための結合装置(220)と、ヒューズプログラミング電圧を低くするためのドレイン領域(211)とを含んでいる。  (もっと読む)

(もっと読む)

集積回路製作におけるデルタ情報設計クロージャ

集積回路(「IC」)製作におけるタイミングドリブンの形状クロージャのためのシステム及び方法が提供される。これらの統合設計製造工程(「IDMP」)は、IC製作のタイミング及びジオメトリ検証工程の情報をIC設計に統合するデルタフローを含む。デルタフローは、回路特徴パラメータに関する差分情報を処理するためのデルタ−ジオメトリタイミング予測工程及び/又はデルタ−タイミング形状予測工程を含むインクリメンタルフローである。デルタフローは、回路特徴パラメータに対応する差分又はデルタ情報を用いてIC設計を独自に再特徴付けする。デルタフローは、新しい回路特徴パラメータを生成する必要がなく、更にIC設計の全ての情報を再処理することを必要とせずに、デバイス及び相互接続構造部の対応するパラメータを強調又は再特徴付けするデルタ出力(インクリメンタルの)を提供する。 (もっと読む)

集積回路製作におけるデルタジオメトリタイミング予測

集積回路(「IC」)製作におけるタイミングドリブンの形状クロージャのためのシステム及び方法が提供される。これらの統合設計製造工程(「IDMP」)は、IC製作のタイミング及びジオメトリ検証工程の情報をIC設計に統合するデルタフローを含む。デルタフローは、回路特徴パラメータに関する差分情報を処理するためのデルタ−ジオメトリタイミング予測工程及び/又はデルタ−タイミング形状予測工程を含むインクリメンタルフローである。デルタフローは、回路特徴パラメータに対応する差分又はデルタ情報を用いてIC設計を独自に再特徴付けする。デルタフローは、新しい回路特徴パラメータを生成する必要がなく、更にIC設計の全ての情報を再処理することを必要とせずに、デバイス及び相互接続構造部の対応するパラメータを強調又は再特徴付けするデルタ出力(インクリメンタルの)を提供する。 (もっと読む)

電子的プログラマブル・アンチヒューズおよびそれにより形成された回路

【課題】 電子的プログラマブル・アンチヒューズおよびそれにより形成された回路を提供することにある。

【解決手段】 アンチヒューズ・デバイス(120)は、バイアス・エレメント(124)とアンチヒューズ・エレメント(128)との間に位置する出力ノード(F)を有する分圧器を形成するために、互いに直列に配置されたバイアス・エレメントとプログラマブル・アンチヒューズ・エレメントとを含む。アンチヒューズ・デバイスがそのプログラム化されていない状態にあるときに、バイアス・エレメントとアンチヒューズ・エレメントのそれぞれは非導電性になる。アンチヒューズ・エレメントがそのプログラム化された状態にあるときに、バイアス・エレメントは非導電性のままであるが、アンチヒューズ・エレメントは導電性になる。そのプログラム化されていない状態とプログラム化された状態とのアンチヒューズ・エレメントの抵抗の差により、1Vの電圧がアンチヒューズ・デバイスの両端間に印加されたときに出力ノードで見られる電圧の差が数百ミリボルト程度になる。この電圧差は、単純な感知回路を使用して容易に感知できるほど大きいものである。

(もっと読む)

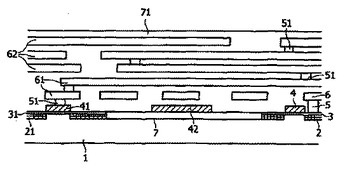

機密性を要する半導体製品、特にスマートカード・チップ

機密性を要する半導体製品、特にスマートカード・チップを提供するため、チップ設計によって実現されうる電気的に活性な構造(2、3、4、5、6)が、例えばシリコンからなるウェーハ(1)内及びウェーハ(1)上に、回路機能の形態で製造されるだけでなく、残りの領域に、それらの下に置かれた機密性を要する回路構造を解析するリバース・エンジニアを大幅に妨げる、互いに絶縁された充てん構造のさらなる導電性部分(42、61、62)(タイル)が設計プログラムによって形成される。形成された部分を説明された偶然の信号経路と連結するための形成された部分間のコンタクトは、「手で」、又は、当該設計プログラムと対応するルーティング・プログラムとの組合せによって配置されることができる。充てん導電性部分はさらに、さらなる回路機能(例えば解析回路)を提供するために、トランジスタ、ダイオード、抵抗器又はコンデンサなどの回路構成部品に接続されてもよい。  (もっと読む)

(もっと読む)

361 - 371 / 371

[ Back to top ]