Fターム[5F064DD09]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子、セル、ブロックの大きさ (500) | 素子の大きさ (178)

Fターム[5F064DD09]に分類される特許

1 - 20 / 178

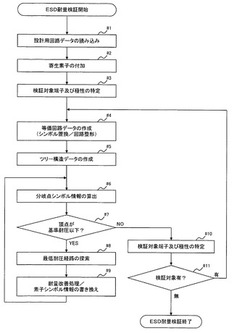

ESD耐量検証方法及びESD耐量検証装置

【課題】 ESD耐量の低いパス及びその原因素子を安易且つ良好に特定できる検証方法及び検証装置を提供する。

【解決手段】 設計用回路データから2つの検証対象端子とその間に接続される検証対象素子を特定し、電流方向を設定し、検証対象素子の夫々を識別情報、電流方向別の特性情報及び耐量情報を記憶した素子シンボル情報を備える素子シンボルで表した等価回路データを作成し、2ノード間の特性情報及び耐量情報を記憶可能な分岐点シンボルを用い、検証対象端子に対応する分岐点シンボルを頂点とし、等価回路データをツリー構造データに変換し、素子シンボル情報に基づいて分岐点シンボル情報を作成し、頂点の分岐点シンボルの耐量情報が基準耐量以下の場合に、耐量情報に基づいて耐性が最も低い最低耐量経路と耐量制限シンボルを特定し、当該耐量制限シンボルに対応する設計用回路データの素子を特定する。

(もっと読む)

レイアウトデータ作成装置及び半導体装置

【課題】従来のようにピラーの分割単位が小数点数とならず、単位ピラートランジスタのピラーの径の変更を行う必要が無くなり、半導体装置を製造するプロセスを複雑化することなく、ピラー型のトランジスタによりセルを、セルロウ内に効率的に配置するレイアウトデータ作成装置を提供する。

【解決手段】本発明のレイアウトデータ作成装置は、集積回路における複数の単位ピラー型トランジスタで構成されるピラー型トランジスタを、配置領域内に配置可能な単位ピラー型トランジスタの整数単位に分割し、配置領域内に配置するサブピラー型トランジスタを生成するトランジスタ調整部2を備えている。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

半導体集積回路のレイアウト設計装置、方法、及びプログラム

【課題】アナログ回路において最適な配線効率を実現するためのレイアウト設計を可能にする。

【解決手段】機能ブロックを構成する素子をその種類毎にグループ化する。機能ブロック内の素子の配置を各素子の接続関係に基づいて決定する。この時、グループを構成する素子の分割数を考慮してもよい。機能ブロックの配置順序を面積又は幅が大きい順に配置されるように決定する。また、配置順序はユーザの指定により調整できることが好ましい。配置順序と回路全体の接続情報とに基づいて各機能ブロックの配置位置を決定する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

スタンダードセル回路、半導体集積回路、及び半導体集積回路装置

【課題】スタンダードセル回路のレイアウト面積を削減する。

【解決手段】配線導体Laは電源電圧VDDaを出力する電源に接続される。レギュレータ6aは、配線導体Laからの電源電圧VDDaを電源電圧VDDaより低い電源電圧VDDbに変換し、配線導体Lbを介してレベルシフタ2−1〜2−3,3,及びスタンダードセル4に出力する。レベルシフタ2−1は、入力されるデータの電圧レベルを電源電圧VDDaの電圧レベルから電源電圧VDDbの電圧レベルに電圧シフトしてスタンダードセル4に出力する。レベルシフタ3は、スタンダードセル4からの出力信号の電圧レベルを電源電圧VDDbの電圧レベルから電源電圧VDDaの電圧レベルに電圧シフトし、出力端子Tqを介して出力する。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体集積回路

【課題】フリップフロップにおけるアクティブ領域のレイアウトの凹凸を低減する。

【解決手段】半導体チップには、クロック領域CR1、ラッチ領域LR1およびバッファ領域BR1が設けられ、クロック領域CR1にはアクティブ領域AK5、AK6が形成され、ラッチ領域LR1にはアクティブ領域AK1、AK2が形成され、バッファ領域BR1にはアクティブ領域AK3、AK4が形成され、アクティブ領域AK1〜AK6の幅をそれぞれにおいて均一の幅として分割されている。

(もっと読む)

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

チャージアップダメージの検証方法および検証装置

【課題】 配線と非配線とを分けて扱い、マクロ等にも半導体集積回路全体にも適用できるアンテナルールを用いるチャージアップダメージの検証方法等を提供できる。

【解決手段】 配線層毎のアンテナ比の上限値を、注目配線層の階層数と総配線層数とに基づいて設定する第1のステップS10、半導体集積回路のレイアウトデータに基づいて、配線層毎に所与のゲートにチャージアップダメージを与えるノードの面積を演算し、下位の配線層に含まれる同一のノードの面積との積算値を求める第2のステップS20、半導体集積回路のモジュール毎に、注目モジュールに含まれる所与のゲートにチャージアップダメージを与えるノードについて、注目モジュールの最上位配線層までの面積の積算値と所与のゲートの面積とに基づいてアンテナ比を求め、注目モジュールの最上位配線層におけるアンテナ比の上限値と比較する第3のステップS30を含む。

(もっと読む)

集積回路のレイアウト設計方法、レイアウト設計装置、及び設計プログラム

【課題】高駆動素子が含まれている論理素子経路に遅延素子を挿入してホールドタイム違反を解消する際に、セットアップタイム違反が新たに発生することを防止する。

【解決手段】レイアウト設計方法が、第1フリップフロップ101と、第2フリップフロップ102と、第1フリップフロップ101の出力と第2フリップフロップ102の入力の間の論理回路とを含む集積回路について配置及び配線を行うステップと、ホールドタイム違反を検出するステップと、遅延素子302をホールドタイム違反を解消するように挿入するステップとを備えている。遅延素子302を挿入するステップでは、第1フリップフロップ101と第2フリップフロップ102間の論理素子経路に高駆動素子105が配置されているかが確認され、高駆動素子105が配置されている場合、高駆動素子105の出力に直接に接続されないように遅延素子302が配置される。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

スイッチアレイ

【課題】 スイッチアレイの占有面積の縮小を図る。

【解決手段】本実施形態のスイッチアレイは、基板上に設けられる2つのスイッチと、第1の方向に延在する第1及び第2の制御線と、を具備し、スイッチのそれぞれは、メモリセルトランジスタが設けられる第1のアクティブ領域と、パストランジスタが設けられる第2のアクティブ領域と、を含み、アクティブ領域内でトランジスタのチャネル長方向に隣接するメモリセルトランジスタはソース又はドレインを共有し、第1及び第2のアクティブ領域は、トランジスタのチャネル幅方向に互いに隣接している。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】RCで鈍る出力電圧を再現し、遅延誤差を抑制すること。

【解決手段】電流テーブル群は、セルへ与える入力電圧の変化開始時からの複数の経過時間の各経過時間でのセルの出力電圧値をセルごとに保持し、設計支援装置がアクセス可能な記憶装置に記憶されている。設計支援装置は、設計対象回路の回路情報の中から選ばれた対象セルに関する各経過時間での出力電圧値を対象セルに基づいて抽出する。設計支援装置は、Vds(出力電圧)<Vgs(入力電圧)−Vth(ゲート閾値電圧)であるVdsの経過時間を補正対象の経過時間に決定する。設計支援装置は、補正対象の経過時間に対象セルの出力側の時定数を加算することにより、該経過時間を補正する。設計支援装置は、補正後の経過時間ごとの出力電圧値と補正対象に決定されなかった経過時間ごとの出力電圧値とを出力する。

(もっと読む)

設計ライブラリデータベース

【課題】結晶化半導体薄膜に対して適正かつ効率的なフォトマスクの作成を可能にする。

【解決手段】1実施形態に係る設計ライブラリデータベースは、2次元的に区画して各々薄膜トランジスタのチャネル領域のサイズを超える複数の結晶粒規定領域が配置された結晶化半導体薄膜を用いる薄膜トランジスタ回路の設計ライブラリデータベースであって、各々のチャネル領域が単一の前記結晶粒規定領域内の固定位置に配置される2個以上の薄膜トランジスタおよび前記2個以上の薄膜トランジスタを相互接続する配線を含む様々な論理ゲート回路をそれぞれ表す複数のスタンダードセル、並びに前記様々な論理ゲート回路の様々な組み合わせをそれぞれ表す複数のマクロセルの少なくとも一方のセルのライブラリ、および前記複数の結晶粒規定領域が配置された結晶化アレイパターンのスタンダードセルのライブラリを含みハードディスクに登録される。

(もっと読む)

MOSFETモデル出力装置及び出力方法

【課題】寄生素子の効果が適切に取り入れられた高精度のMOSFETモデルを作成可能なMOSFETモデル出力装置及び出力方法を提供する。

【解決手段】MOSFETの形状データを入力するための形状データ入力部101を備える。前記形状データを利用して、前記MOSFETモデルに付加するための寄生素子モデルのパラメータを算出するパラメータ算出部102を備える。前記寄生素子モデルのパラメータを利用して、前記寄生素子モデルが付加された前記MOSFETモデルを作成して出力するMOSFETモデル出力部103を備える。そして、前記MOSFETモデル出力部は、前記MOSFETがN型MOSFETである場合とP型MOSFETである場合とで、前記MOSFETモデルに対し、異なる前記寄生素子モデルを付加する。

(もっと読む)

半導体装置、電源スイッチの制御方法及びその設計方法

【課題】従来の半導体装置では、電源制御領域への突入電流の発生を抑制するためにチップ面積が増大する問題があった。

【解決手段】本発明にかかる半導体装置は、オン抵抗が大きな第1のスイッチトランジスタSWLと、オン抵抗が小さな第2のスイッチトランジスタSWSと、を有し、第1、第2のスイッチトランジスタSWL、SWSは、異なる領域に電流を供給し、第1のスイッチトランジスタSWSは、制御信号CONTを直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLは、前記制御信号を直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLのうち初段に配置される第2のスイッチトランジスタSWLは、第1のスイッチトランジスタSWSのうち最も後ろに配置される第1のスイッチトランジスタSWSが出力する制御信号CONTが入力される。

(もっと読む)

1 - 20 / 178

[ Back to top ]