Fターム[5F064DD15]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子、セル、ブロックの位置、座標 (576) | 対称性 (163)

Fターム[5F064DD15]の下位に属するFターム

線対称 (65)

Fターム[5F064DD15]に分類される特許

1 - 20 / 98

メモリセル

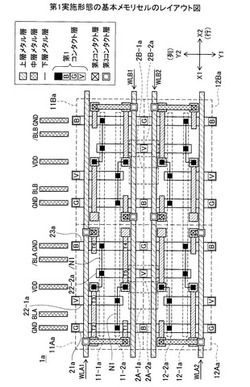

【課題】拡散層等のバルクが固定であってメタル層、コンタクト層の少なくとも何れか1層を変更して複数の仕様に対応可能なメモリセルを提供すること。

【解決手段】メモリユニットが列方向に沿って鏡面対称に行方向に沿って並置されて、2行2列に配置されメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第4拡散層を備え一対の記憶ノードが構成される。第1および第2ワード線は第1〜第4拡散層の両端部外方に配置される。第1及び第2ワード線の間に行方向に沿って第1のメタル配線領域が確保され、第1メタル層が配線可能とされる。列方向に隣接配置されるメモリユニットの境界領域でありは第3、第4拡散層が配置される列方向の位置には列方向に沿って第2のメタル配線領域が確保され、第2メタル層が配線可能とされる。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

レイアウト設計装置

【課題】アナログレイアウト設計の自動化による設計工期の短縮を図ることが可能なレイアウト設計装置を提供すること。

【解決手段】レイアウト設計装置21は、回路データ24の中から特性を一致させる必要があるトランジスタ、抵抗、容量素子群を抽出し、トランジスタ、抵抗、容量素子群の接続関係に基づいてトランジスタ、抵抗、容量素子群に含まれる複数のトランジスタ、抵抗、容量素子によって構成される所定の機能を有する回路、たとえば差動回路、差動負荷回路およびミラー回路を特定する。そして、特定された回路の種別に応じてレイアウト制約30を生成し、レイアウト制約30に基づいて配置配線を行なう。したがって、アナログ回路のレイアウト制約30を自動的に付加することができ、アナログレイアウト設計の自動化による設計工期の短縮を図ることが可能となる。

(もっと読む)

半導体装置

【課題】 データ保持回路を備えた半導体装置において、回路面積の低減及び動作速度の向上を図ること。

【解決手段】 本半導体装置100は、少なくとも1以上の不揮発性のメモリセルFCと、メモリセルFCへの書き込みデータ又はメモリセルFCからの読み出しデータを格納するラッチ回路30とを含み、メモリセルFC及びラッチ回路30がアレイ状に配置された複数の不揮発性メモリ回路20と、複数の不揮発性メモリ回路20におけるラッチ回路30のそれぞれに接続され、データを一時的に保持する複数のデータ保持回路10と、を備える。

(もっと読む)

半導体チップ、半導体装置及びLSI設計装置

【課題】チップコストの低下とチップ歩留りの向上とを同時に実現する。

【解決手段】実施形態に係わる半導体チップは、パッド領域11及び方形でないゲート領域12を備える第1のレイアウトL1と、第1のレイアウトL1を180°回転させた第2のレイアウトL2とを備える。第1及び第2のレイアウトL1,L2は、点対称かつ重なり合わずに結合されることによりチップレイアウトを構成する。チップレイアウトは、方形のチップ領域内に配置され、第1及び第2のレイアウトL1,L2は、それぞれ独立に動作するLSIを構成する。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

半導体集積回路のレイアウト変更方法および、レイアウト装置及び半導体集積回路

【課題】 最小限度の層の変更のみでレイアウト変更を可能にし、マスク製作費用を最小限に抑え、変更箇所以外でのタイミングを保持する。

【解決手段】 半導体集積回路のレイアウト変更方法は、半導体集積回路のレイアウト上の所定の箇所に、既存の配線層とは接続しない不接続層を含む複数層にわたるスタック構造のダミービアをあらかじめ配置し、レイアウト変更時に、所望の位置のスタック構造のダミービアに接続する新規配線を配置し、当該選択されたダミービアの前記不接続層にビア層を挿入する。

(もっと読む)

マスタスライス方式メモリセル

【課題】複数種類の回路構成をマスタスライス方式で対応可能なメモリセル専用のマスタスライス方式メモリセルを提供すること。

【解決手段】メモリユニットが2行2列に配置されてメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第3拡散層を備え、各拡散層で並列接続のトランジスタが構成される。第1および第2ワード線は第1〜第3拡散層の両端部外方に配置される。第1〜第3拡散層の第1コンタクト層とゲート層の第2コンタクト層との間、第1コンタクト層と第1/第2ワード線との間に、行方向に沿って第1のメタル配線領域が確保される。第1のメタル配線領域には、第2または第3メタル層の何れかが配線可能である。第1及び第2拡散層、第2及び第3拡散層の間には、列方向に沿って第2のメタル配線領域が確保される。第2のメタル配線領域には第3メタル層が配線可能である。

(もっと読む)

半導体集積回路

【課題】セル面積が小さい不揮発性SRAMセルを提案する。

【解決手段】本開示に係わる半導体集積回路は、第1及び第2のインバーターINV1,INV2と、ゲートにワード線WLが接続され、ソースに第1のビット線BLが接続され、ドレインに第2のインバーターINV2の入力端子が接続される第1のトランジスタM5と、ゲートにワード線WLが接続され、ソースに第2のビット線bBLが接続され、ドレインに第1のインバーターINV1の入力端子が接続される第2のトランジスタM6と、第1の端子に第1のトランジスタM5のドレインが接続され、第2の端子に第1のインバーターINV1の出力端子が接続される第1の可変抵抗素子R1と、第1の端子に第2のトランジスタINV2のドレインが接続され、第2の端子に第2のインバーターINV2の出力端子が接続される第2の可変抵抗素子R2とを備える。

(もっと読む)

半導体装置

【課題】電子回路の小型化を実現する。

【解決手段】MOSトランジスタ20が、格子状に形成されたゲート電極22と、ゲート電極22で囲まれたソース領域23およびドレイン領域24と、ゲート電極22の格子の一方向に沿って配置され、ソース領域23およびドレイン領域24とコンタクトを介して接続するソース用メタル配線27およびドレイン用メタル配線28を有する。ソース領域23およびドレイン領域24のそれぞれは、各メタル配線の長さ方向に長辺を有する長方形状に形成される。ソース用メタル配線27およびドレイン用メタル配線28は、その長さ方向にジグザグ形状に形成されて、それぞれソース用コンタクト25およびドレイン用コンタクト26に接続する。

(もっと読む)

LSI,鉄道用フェールセーフLSI,電子装置,鉄道用電子装置

【課題】従来のフェールセーフLSIは、チップ内のプロセッサや比較回路の配置について言及されていたが、パッケージの信号ピン配置までは言及されていなかった。また、多様な周辺回路や高速な外部メモリへの対応も考慮されていなかった。

【解決手段】2つのプロセッサからの出力を照合して一本化された内部インタフェースを共通系内部バスに接続し、その共通系内部バスに複数の外部インタフェース回路を接続する。また、2つの系統に関する信号ピンをパッケージの対角に配置するともに、それらの間に共通系に関する信号ピンを配置するようにする。

(もっと読む)

対称的な電気挙動を有する物理的に非対称的な半導体装置を採用するシステム及び方法

互いに平行に配置され、それらの間に空間を画定する第1の細長い構造体及び第2の細長い構造体を備える集積回路装置。集積回路装置はまた、第1及び第2の細長い構造体間の空間に分布された導電性構造体を備える。導電性構造体の少なくとも第1の1つの導電性構造体は、第2の細長い構造体よりも第1の細長い構造体に近く配置される。導電性構造体の少なくとも第2の1つの導電性構造体は、第1の細長い構造体よりも第2の細長い構造体に近く配置される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置のレイアウト設計方法

【課題】アナログ回路に利用される抵抗素子の配置領域面積を低減し、抵抗素子の相対精度を向上させる半導体装置及び半導体装置のレイアウト設計方法を提供する。

【解決手段】一の方向に並列配置されたトランジスタ素子(トランジスタ素子Q1及びトランジスタ素子Q2)と、トランジスタ素子上に層間絶縁膜(層間絶縁膜14)を介して形成された抵抗素子(抵抗素子R1及び抵抗素子R2)を有し、平面視において抵抗素子の長さ方向はトランジスタ素子のチャネル幅方向に直交する。

(もっと読む)

半導体装置

【課題】占有面積を増やすことなくロジック回路領域におけるトランジスタ特性の変動が抑制される半導体装置を提供する。

【解決手段】NMOS領域の素子形成領域4と、この素子形成領域4に隣り合う他の素子形成領域4との間隔(ゲート幅方向)が一定の間隔(距離2×LA)に設定されている。また、この素子形成領域4と、この素子形成領域4に隣り合う素子形成領域8との間隔(ゲート幅方向)も一定の間隔(距離2×LA)に設定されている。

(もっと読む)

半導体装置

【課題】トランジスタの距離に依存したばらつきに対して、電流源の出力電流誤差を均一にする事ができる、レイアウト構成の半導体装置の提供。

【解決手段】第1の電流源を構成するトランジスタAと、第1の電流源の電流を基準とした第2の電流源を構成する複数のMOSトランジスタBを備えたカレントミラー回路のレイアウトとして、MOSトランジスタAの周囲に、MOSトランジスタBを均等に配置し、入力電流端子及び出力電流端子から、MOSトランジスタA、複数のトランジスタBの同一の端子への配線に関して、それらの特性(寄生抵抗容量)を該配線間で均等化させるレイアウトを有する。

(もっと読む)

集積回路の設計のためのデバイスミスマッチのモデリングおよびシミュレーティング

【課題】ユーザは、回路スケマティック中のデバイスに対するレイアウトスタイルであって、デバイス配置およびデバイス相関の特徴を捉えるレイアウトスタイルを特定する。

【解決手段】結果として得られるレイアウトは、コンピュータを用いることでシミュレーションされ得て、1つ以上のパフォーマンス指標がその回路に対して評価され得る。場合によっては、テストチップが、異なるレイアウトスタイルに対応する配置に対するデバイス相関を画定するために用いられても良い。

(もっと読む)

半導体集積回路評価方法、半導体集積回路、および半導体集積回路評価装置

【課題】大規模な半導体集積回路(DMA−TEG等)における不良トランジスタの検出と、不良トランジスタのトランジスタ特性の測定を高速で行うことができる、半導体集積回路評価方法を提供する

【解決手段】本発明の半導体集積回路評価方法においては、評価セルアレイ中の被評価トランジスタの閾値Vthの電圧が、閾値Vth電圧の正規分布曲線に対して、5σ(σは標準偏差)以内の分布から外れたものを選別する。そして、閾値Vthの電圧が5σ(σは標準偏差)以内の分布から外れた被評価トランジスタに対して、トランジスタ特性の測定を行う。

(もっと読む)

レイアウト設計方法

【課題】バンプによるスタック実装のためのチップ重ね合わせ配置を自動的に行うことのできるレイアウト設計方法を提供する。

【解決手段】LSI1のフロアプラン上にレイアウト済みのLSI2に配設されているバンプセルのミラー反転イメージをして、フロアプラン上でのバンプセルの配置位置座標を算出し、その配置位置座標にLSI2のバンプセルの接続先となるLSI1のバンプセルを配置し、そのバンプセルの配置位置に応じて、LSI1の機能セルの配置および配線を行う。

(もっと読む)

半導体集積回路及びそのレイアウト方法

【課題】メモリセルアレイ等の矩形セルを正方形に配置した半導体集積回路及びそのレイアウト設計方法を提供する。

【解決手段】それぞれ実質的に同一形状を有する第一乃至第四矩形セルが、第一矩形セルの長辺と第二矩形セルの短辺が矩形枠の第一辺に内接し、第二矩形セルの長辺と第三矩形セルの短辺が矩形枠の第二辺に内接し、第三矩形セルの長辺と第四矩形セルの短辺が矩形枠の第三辺に内接し、第四矩形セルの長辺と第一矩形セルの短辺が矩形枠の第四辺に内接するように配置されたレイアウトパターンを有する。

(もっと読む)

1 - 20 / 98

[ Back to top ]