Fターム[5F064DD16]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子、セル、ブロックの位置、座標 (576) | 対称性 (163) | 線対称 (65)

Fターム[5F064DD16]に分類される特許

1 - 20 / 65

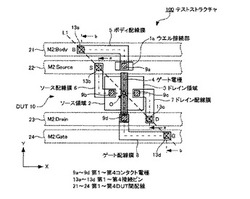

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

レイアウト方法及び半導体装置の製造方法

【課題】ダブルパターニングによるトランジスタの特性ばらつきを抑える。

【解決手段】並列に配置される複数のゲート電極パターン10〜15を交互に、ダブルパターニングの第1の露光工程で形成する第1のパターン及び第2の露光工程で形成する第2のパターンとして設定し(ステップS1)、第1のパターンと第2のパターンとを並列に接続したトランジスタ対を含む回路をレイアウトすることで(ステップS2)、ダブルパターニングによるトランジスタの特性ばらつきが抑えられる。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

半導体装置

【課題】高い比精度が要求される複数のトランジスタの特性ばらつきを低減する。

【解決手段】本発明の半導体装置は、半導体基板上に配置されたトランジスタTr1と、半導体基板上で見たキャリアのドリフト方向がトランジスタTr1のキャリアのドリフト方向と同じ方向となる向きに配置されたトランジスタTr2と、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51b同士を接続する拡散層51cと、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51bまたはその拡散層同士を接続する拡散層51cの表面に接続され、拡散層51a,51bに給電するためのコンタクトプラグ61と、を備える。

(もっと読む)

半導体集積回路のレイアウト装置

【課題】 本発明の課題は、半導体集積回路のレイアウト処理におけるセル配置の際に、隣り合う2つのセルの特性を考慮した配置によって最適化することことを目的とする。

【解決手段】 上記課題は、隣接して配置されるセルの組み合せ毎にショート可否とセル枠のオーバーラップ可能な距離との対応付けを含む最適化ライブラリを格納する第一記憶領域と、デザインルールを満たすセル配置において、前記第一記憶領域に格納されている前記最適化ライブラリを参照することによって、前記ショート可能なセルの組み合せに対して前記セル枠をオーバーラップさせて配置する第一最適化手段とを有することを特徴とする半導体集積回路のレイアウト装置により達成される。

(もっと読む)

半導体集積回路

【課題】複数の相補トランジスタ対(CMOS対)を同相駆動するような回路を実現するためのスタンダードセルのスペース削減、コスト低減を図る。

【解決手段】所望の回路を形成するためのセルに相補対を同相駆動するタイプのスタンダードセルを含む。例えばダブルハイトの場合、CMOS対を複数(ここでは7対)含み、その少なくとも一部(ここでは7対とも)同相駆動される。このスタンダードセルは、CMOS対の1対分に対応した基本セル長のM(ここではM=2)倍のM倍セル長で、規格化されたセル長(縦)のサイズが規定されている。同相駆動される少なくとも2対分の共通ゲート電極21,22,23が規格セル長(縦)の方向に直線配置されている。

(もっと読む)

集積回路装置及び電子機器

【課題】I/Oセルを効率良く配置できる集積回路装置及び電子機器等を提供すること。

【解決手段】集積回路装置は、各I/OセルがI/O回路及びパッドで構成される複数のI/Oセルと、コア回路102とを含み、チップ外縁部101からコア回路102へ向かう方向を第1の方向とした場合に、複数のI/Oセルのうちの第1のI/Oセル10の第1のI/O回路11及び複数のI/Oセルのうちの第2のI/Oセル20の第2のI/O回路21は、第1の方向に沿って並んで配置され、第1の方向に直交する方向を第2の方向とした場合に、第1のI/Oセル10の第1のパッド12は、第1のI/O回路11の第2の方向に配置される。

(もっと読む)

半導体装置及びそれを用いた表示装置のデータドライバ

【課題】省面積化を図るデコーダ及び、それを用いた省面積(低コスト)のデータドライバを提供。

【解決手段】トランジスタ(21〜24)の配列と、第1の配線層(71)に配置され前記配列上方を互いに離間して行方向に延在される複数の参照電圧信号線と、第2の配線層(72)に配置され、前記配列上方を互いに離間して行方向に延在される複数の参照電圧信号線を備え、行、列方向に隣接するトランジスタの拡散層(56)には、互いに異なる配線層の参照電圧信号線が接続される。

(もっと読む)

半導体装置のレイアウト設計装置、方法及びプログラム

【課題】電源分離処理を行うと、チップサイズが増大する課題があった。

【解決手段】セルデータ格納部と、分離処理部とを具備する半導体装置のレイアウト設計装置によって解決できる。セルデータ格納部は、複数のセルが隣接して連続する構造を有する半導体装置における各セルのセルデータを格納する。分離処理部は、セルデータを処理し、複数のセルに亘って設けられるメタル配線を、半導体装置の設計基準に従って、セル間で分離する。分離処理部は、延伸・短縮部と、反転部とを備える。延伸・短縮部は、セルデータのそれぞれについて、メタル配線の一部であって、各セルのセル枠内に配置されるべきメタル部分の一端を延伸すると共に、他端を、一端を延伸した方向と同じ方向に短縮する。反転部は、延伸・短縮部によって、延伸され及び短縮されたメタル部分を有する任意のセルを、延伸された一端と、短縮された他端とが入れ替わるように、ミラー反転する。

(もっと読む)

半導体装置

【課題】チップ面積を縮小することができ、かつコンタクト間の短絡を防止することができる半導体装置を提供する。

【解決手段】電源配線Paは第1方向に延びている。第1および第2ゲートG1、G2のそれぞれは、第1方向と交差する第2方向に延びる第1および第2端部領域RA1、RA2を含む。第1および第2端部領域RA1、RA2は、第1方向において互いに第1間隔S1を空けて配列されている。絶縁膜は、第1および第2端部領域RA1、RA2の間の少なくとも一部を埋め、平面視において第2の方向に沿って第1および第2端部領域RA1、RA2の間を通る空隙部VDを有する。電源コンタクトCPaは第1および第2端部領域RA1、RA2の間の領域の第2方向に沿った延長領域から離れて配置されている。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】半導体集積回路装置の集積度の向上を図ることのできる技術を提供する。

【解決手段】セルの高さ方向に隣接して配置されるセルrow上段の2入力NAND回路6とセルrow下段のインバータ回路1との間の結線に、2層目以上の配線を用いずに、1層目の配線M1よりも下層に位置し、2入力NAND回路6またはインバータ回路1を構成するMISFETのゲート電極7N2,7P2と一体化した導電体膜からなる配線8を用いる。

(もっと読む)

アナログ回路用セルアレイおよびアナログ集積回路

【課題】短いリードタイムで製造でき、高い集積度を有するアナログ回路の実現。

【解決手段】複数のトランジスタセルPMOSC2,NMOSC2が、アレイ状に配置されたアナログ回路用セルアレイARYP1,ARYN1であって、各トランジスタセルは、隣接して順に配置された第1ソース領域SOURCE1、第1チャネル領域、共通のドレイン領域DRAIN、第2チャネル領域および第2ソース領域SOURCE2と、第1チャネル領域および前記第2チャネル領域上にそれぞれ配置された第1ゲート電極POLYG1および第2ゲート電極POLYG2と、を備え、第1ゲート電極POLYG1と第2ゲート電極POLYG2は接続して使用され、第1ソース領域SOURCE1と第2ソース領域SOURCE2は接続して使用される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】閾値電圧が互いに同一であることを要求される2つのトランジスタにおいて、閾値電圧が異なる値になることを抑制する半導体装置の製造方法及び半導体装置を提供する。

【解決手段】第1素子形成領域12には第1トランジスタ202及び第2トランジスタ204が形成され、第2素子形成領域13には第3トランジスタ302が形成される。これら3つのトランジスタは同一導電型である。第1トランジスタ202及び第2トランジスタ204は同一の閾値電圧を有する。第1マスクパターンを用いて第1素子形成領域12に第1ウェル210を形成し、第2マスクパターンを用いて第2素子形成領域13に第2ウェル410を形成する。第1トランジスタ202のチャネル領域及び第2トランジスタ204のチャネル領域は基準線Lを介して線対称な形状を有している。また第1マスクパターンも、基準線Lを介して線対称な形状を有している。

(もっと読む)

半導体集積回路装置とテスト端子配置方法

【課題】テスト端子がI/Oセルの1部を占有することをなくし、テスト端子に起因するチップサイズの増大を抑止し、コスト増大を抑止する半導体集積回路装置の提供。

【解決手段】チップの第1の辺に沿って配置される第1の論理回路セル(IOセル)(2)の列と、前記第1の辺と直交する第2の辺に沿って配置される第2の論理回路セル(IOセル)(2’)の列と、を有し、第1の辺と第2の辺とが交わるチップコーナー部において、第1のテスト論理回路セル(4A)は、前記第1の論理回路セル(2)の列の端部のセルの辺に長辺を対向させて配置され、第2のテスト論理回路セル(4B)は、第2の論理回路セル(2’)の列の端部のセルの辺に長辺を対向させて配置され、第1のテスト論理回路セル(4A)と第2のテスト論理回路セル(4B)は、それぞれの平面形状が、対向配置される前記斜辺の中間の仮想線(8)に関して互いに対称(鏡映対称)となるように配置される。

(もっと読む)

スタンダードセルおよびそれを用いた自動配置配線方法

【課題】半導体装置設計時の自動配置配線における配線ショートによるセル再配置を抑制する。

【解決手段】本発明のスタンダードセルおよびそれを用いた自動配置配線方法は、回路素子が配置される矩形の素子領域11と、素子領域11の対向する2辺と同じ幅で対向する2辺に近接して設けられ、上層配線が配置される矩形の追加配線領域12a、12bを有する。

(もっと読む)

1 - 20 / 65

[ Back to top ]