Fターム[5F064DD46]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 付加的要素に関する構造 (884) | ボンディングパッドに関するもの (728) | テスト用パッド (92)

Fターム[5F064DD46]に分類される特許

1 - 20 / 92

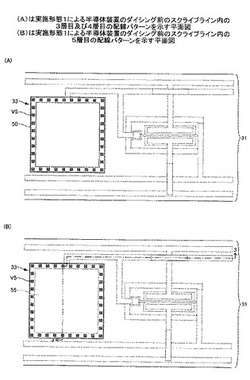

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

半導体ウェハ、半導体装置、及び半導体装置の製造方法

【課題】ヒューズメモリを利用したトリミングを行う半導体ウェハにおける各半導体チップの回路面積を小さくする。

【解決手段】半導体ウェハ10におけるシリコン基板上は、複数個のチップ領域TARとこの領域TARを囲むスクライブ領域SARとに区画されている。チップ領域TARには、トリミング対象回路11と、ヒューズ素子Fm(m=1〜2M)と、ヒューズ素子Fm(m=1〜2M)が断線状態であるか否かを検出する検出回路としての役割を果たす定電流源IPm(m=1〜2M)及びインバータINm(m=1〜2M)とが形成されている。スクライブ領域SARには、制御信号に応じてON/OFFが切り換わり、ONとなることによりヒューズ素子Fm(m=1〜2M)を断線させる電流を発生するNチャネル電界効果トランジスタTSm(m=1〜2M)がある。

(もっと読む)

半導体装置

【課題】電源ノイズを一層効果的に解消する技術を提供する。

【解決手段】半導体装置1は、所定動作を実行するための内部回路6と、内部回路6に対して高電位電圧を供給するための電源ライン7と、内部回路6に対して低電位電圧を供給するためのグラウンドライン8と、ウェハテスト用電極パッド9と、ウェハテスト用電極パッド9を内部回路6に接続するための電気線10と、電気線10を内部回路6に対して非導通状態にすると共に、電気線10を電源ライン7とグラウンドライン8のうち何れか一方に対して選択的に導通状態とする接続切替部11と、を備える。

(もっと読む)

半導体装置

【課題】裏面FIB加工における場所特定を容易にする。

【解決手段】半導体装置は、第1方向および前記第1方向に直交する第2方向の平面内に広がる第1導電型の半導体基板60の表面上に形成された回路部65と、前記半導体基板内の表面側に形成され、前記回路部を構成し、素子として機能する、前記第1導電型と異なる第2導電型の複数のウェル61と、前記半導体基板内の表面側に形成され、前記回路部を構成せず、素子として機能しない、前記第2導電型の複数のダミーウェル62と、を具備する。

(もっと読む)

半導体装置

【課題】ダイシング処理に起因する、チップ用パッド同士のショートを抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板と複数の第1のパッドと、複数の第2のパッドとを備える半導体装置であり、第1のパッドは素子形成領域IMC内に、第2のパッドは素子形成領域IMCを取り囲むダイシングライン領域DLR内に形成される。ダイシングライン領域DLRには、第2のパッド同士が電気的短絡を生じさせやすい第1の領域SLRと、第2のパッド同士が電気的短絡を生じさせにくい第2の領域SURとを有している。第1の領域SLRに対向する位置に配置された一部の第1のパッドは、第2の領域SURに対向する位置に配置された残りの第1のパッドよりも、素子形成領域IMCの外縁の1辺BDLから離れて配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積の増加を抑制しつつ、ウェハ状態でのスクリーニング時に電源電圧低下(IRドロップ)を抑えることができる半導体装置を提供する。

【解決手段】本発明の一形態に係る半導体装置50は、半導体チップ100と、半導体チップ100上面の中央部のチップ中央領域120に形成された複数の外部接続用パッド102及び複数の検査用パッド104と、複数の外部接続用パッド102上に形成されたバンプ105とを備える。

(もっと読む)

半導体装置の製造方法、半導体装置の検査方法、及び半導体装置

【課題】半導体装置の検査において、電極パッドの配列、スクライブ領域の幅に影響されることなくプローブカードを共有化し、プローブカードの製作費用を低減する。

【解決手段】基板20はチップ領域100、スクライブ領域200および電極パッド300を備えている。チップ領域100は基板20上の第1の方向に沿って、スクライブ領域200により互いに分離されるように並んでいる。電極パッド300は第1の方向に沿って周期性をもって配列している。接続用電極パッド320はチップ領域100に形成され、ダミー電極パッド340は少なくともスクライブ領域200に形成されている。電極パッド300の間隔はスクライブ領域200の幅よりも狭い。電極パッド300の配列と平行な方向における、チップ領域100とスクライブ領域200を合わせた幅は、電極パッド300間隔の整数倍である。

(もっと読む)

ネットリスト作成方法、回路シミュレーション方法、半導体集積回路装置の設計方法及び半導体集積回路装置の製造方法

【課題】パッケージにより生じる回路特性のバラツキを簡便にかつ正確に予測する。

【解決手段】設計されたレイアウトデータと、パッケージに起因してシリコンチップに加わる応力値の分布を示す応力マップデータと、シリコンチップに搭載される各素子について、応力値と素子の特性変動量の関係を示す検量線データとを用いる。レイアウトデータから素子の種類、位置、方向、大きさのうち1つ以上の情報を読み取る。その素子の位置での応力値を応力マップデータから読み取る。その応力値に対するその素子の特性変動量をその素子に対応する検量線データから読み取る。その特性変動量に基づいてその素子の特性を修正してネットリストの作成を行なう。

(もっと読む)

半導体素子及び半導体装置の製造方法

【課題】隣接した半導体素子領域(IC領域)を同時に検査しても、検査用のプローブが外部電極から食み出し難くい、半導体素子、半導体ウエハ、及び半導体装置の製造方法を提供する。

【解決手段】外周に沿って配置された複数の外部電極28を有する、矩形の半導体素子38であって、前記外部電極の対向する二辺が、前記半導体素子の一の対角線34に垂直な方向36を向いている半導体素子。

(もっと読む)

半導体構成素子を備えた回路装置

本発明は、電力端子(2.1,2.2)と、該電力端子から電気的に絶縁されている、制御電圧(U2)を印加するための制御端子(2.0)とを有する半導体構成素子(2)、並びに、半導体構成素子の電気的な特性を測定するために制御端子に接触接続するための制御端子コンタクト面(3)を有する電気的な回路装置(1,1a,1b,31,51,61,71)に関する。接続装置(6,32)、特にアンチヒューズ又は回路ユニットが設けられている。接続装置を介して制御端子を直列ユニット(4;34;78,74)と電気的に接続可能であり、接続装置を、制御端子が直列ユニットと電気的に接続されていない非導通状態から、制御端子が直列ユニットと電気的に接続されている導通状態に移行可能である。アンチヒューズを半導体構成素子に集積することができる。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法および半導体装置の判別方法

【課題】装置に固有な所望の情報を、新たな製造工程を増やさず容易に記録することができる半導体装置を提供する。

【解決手段】第1面に複数の第1電極端子11を備える第1装置10と、第1面と向かい合う第2面に、複数の第2電極端子21を備える第2装置20と、複数の第1電極端子11と複数の第2電極端子21との間に配置され、情報を記録する記録部30とを具備する。記録部30は、複数の第1電極端子11に含まれる第3電極端子11aと、複数の第2電極端子21に含まれる第4電極端子21aとを電気的に接続する導通部31と、複数の第1電極端子11に含まれる第5電極端子11bと、複数の第2電極端子21に含まれる第6電極端子21bとに接触し、第5電極端子11bと第6電極端子21bとの電気的な接続を阻害する高抵抗部32とを備える。

(もっと読む)

無線集積回路装置の製造方法、無線集積回路装置及び電子機器

【課題】効率的な動作試験ができる無線集積回路装置の製造方法、無線集積回路装置及び電子機器等を提供すること。

【解決手段】無線集積回路装置の製造方法は、ウェハー上に複数の無線集積回路装置100を形成し、複数の無線集積回路装置100のうちの少なくとも1つの無線集積回路装置を送信モード無線集積回路装置100aに設定し、複数の無線集積回路装置100のうちの送信モード無線集積回路装置100aを除く少なくとも1つの無線集積回路装置を受信モード無線集積回路装置100bに設定する。送信モード無線集積回路装置100aの送信回路により動作試験用の送信データを送信し、受信モード無線集積回路装置100bの受信回路により動作試験用の送信データを受信して動作試験を実行する。動作試験の完了後に複数の無線集積回路装置100をダイシングする。

(もっと読む)

半導体装置

【課題】一部のデータ入出力端子のみを用いて内蔵された複数の半導体チップを並列にテストすることのできる半導体装置を提供する。

【解決手段】複数の第1データ入出力端子と接続され、第1のテスト回路と、第1の記憶部とを有し、テスト動作時には、第1の記憶部から出力されるデータに応じて第1のテスト回路で第1のテスト結果を生成する第1の半導体チップと、複数の第2データ入出力端子と接続され、第2及び第3のテスト回路と、第2の記憶部とを有し、テスト動作時には、第2の記憶部から出力されるデータに応じて第2のテスト回路で第2のテスト結果を生成し、第2のテスト結果と第1の半導体チップの第1のテスト回路から供給される第1のテスト結果とに応じて第3のテスト回路で第3のテスト結果を生成し、第3のテスト結果を所定の第2データ入出力端子に出力する第2の半導体チップと、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】中間配線層までの配線が行われているマスターウェーハを使用しても、最終製品の歩留りを高い精度で予測することができる半導体装置およびその製造方法を提供する。

【解決手段】多層配線構造の中間配線層までを使用して機能動作を行うように設計された機能ブロック(SRAMマクロ11、ロジックブロック12、ロジックブロック13、IPブロック14)を搭載したマスターウェーハを使用するマスタースライス方式の半導体装置は、この中間配線層に試験用パッドTPを備え、この試験用パッドTPが、各機能ブロックに接続される。

(もっと読む)

半導体装置の製造方法、製造プログラム、及び半導体装置

【課題】回路規模の増大を抑制しつつ、素子破壊によってノード間の電気的接続を制御する電流制御素子を有する半導体装置の信頼性を高める。

【解決手段】本発明による半導体装置の製造方法は、半導体ウエハ1上に形成された素子特性抽出用パタン30の素子特性を測定するステップと、測定された素子特性を、素子特性抽出用パタン30に対応付けられた電流制御素子20の素子特性として抽出するステップと、抽出された素子特性に基づいて、半導体ウエハ1上におけるノード間に形成された電流制御素子20に供給するエネルギーを設定するステップと、設定されたエネルギーを電流制御素子に供給し、電流制御素子の素子破壊によってノード間の電気的接続を不可逆的に制御するステップとを具備する。

(もっと読む)

半導体装置の製造方法

【課題】より多数のリソグラフィ用合わせマークおよびPCMを設けることができ、かつPCMによる情報の漏えいを防止することができる半導体装置の製造方法を提供する。

【解決手段】複数の第1半導体チップ領域CRaに挟まれる第1スクライブ領域SCaの一部には、第1領域RAおよび第2領域RBが平行に配置されている。第1領域RAには、能動素子(トランジスタなど)および受動素子(抵抗、容量など)の少なくともいずれかの電気的評価を行うための第1モニター、寸法管理を行うための第2モニター、および、膜厚測定を行うための第3モニターから選択された少なくとも1つのモニターが配置されている。第2領域RBにはリソグラフィ用合わせマークが配置されている。切断する工程において第1領域RAが切り落とされる。

(もっと読む)

1 - 20 / 92

[ Back to top ]