Fターム[5F064EE08]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 配線長 (567)

Fターム[5F064EE08]に分類される特許

101 - 120 / 567

半導体装置

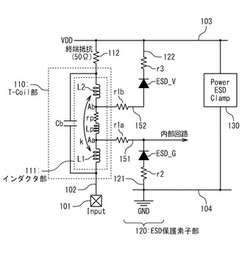

【課題】ESD放電経路におけるメタル配線の電流密度の許容値を高くとることが可能であり、また、配線抵抗を小さくすることが可能である半導体装置を提供する。

【解決手段】信号パッド(101)と、電源線(103)と、接地線(104)と、一端が信号パッド(101)と接続されたインダクタ(111)と、インダクタ(111)の他端と電源線(103)または接地線(104)との間に設けられた終端抵抗(112)と、インダクタ(111)の中間の第1位置(Aa)に接続された第1ESD保護素子(ESD_G)と、インダクタ(111)の中間の第1位置(Aa)とは異なる第2位置(Ab)に接続された第2ESD保護素子(ESD_V)とを備える。

(もっと読む)

半導体装置

【課題】誤動作を抑制しつつセルサイズを小さくしたフリップフロップ回路を備える、半導体装置を提供する。

【解決手段】CMOS半導体集積回路内に構成されたフリップフロップ回路を備える半導体装置であって、前記フリップフロップ回路は、少なくとも、第1のクロック信号を生成する、第1のクロック生成インバーターと、前記第1のクロック信号を反転させた第2のクロック信号を生成する、第2のクロック生成インバーターと、を備え、前記第1及び第2のクロック生成インバーターは、前記フリップフロップ回路のマスターラッチ部とスレーブラッチ部とから構成されるラッチ部を挟むように配置され、前記第1のクロック生成インバーターと、前記第1のクロック生成インバーターに隣り合う前記フリップフロップ回路内の第1の他の回路とは、ソース領域を共有し、前記第2のクロック生成インバーターと、前記第2のクロック生成インバーターに隣り合う前記フリップフロップ回路内の第2の他の回路とは、ソース領域を共有する。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】ストレスマイグレーションにより発生する不良を容易に減少させることを図ること。

【解決手段】設計支援装置は、設計対象回路の回路情報100内の対象配線101の面積と当該対象配線101と他層の配線とを接続するビアの個数に基づいて、ビア1個あたりの対象配線101の面積が所定の規格値より大きいか否かを判断する。ビア1個あたりの対象配線101の面積が所定の規格値より大きい場合、設計支援装置は、対象配線101を分割し、他層の配線を介して分割された後の配線間を接続することでビアの個数を増加させ、ビア1個あたりの対象配線101の面積を小さくすることができる。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、設計支援装置、及び半導体集積回路

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、回路情報21に基づいてレイアウト対象回路41、42の消費電流量211を算出するステップと、電源配線2から電源供給可能な領域における単位面積当りの供給可能電流量212を算出するステップと、算出された消費電流量211に基づき、レイアウト対象回路41、42の単位面積当りの消費電流量が、供給可能電流量212以上となるように、対象回路のセルサイズ213を設定するステップとを具備する。

(もっと読む)

半導体集積回路装置

【課題】CMP法により研磨される絶縁膜の平坦性を向上する。

【解決手段】半導体基板1の主面上に形成されたMISFETQ1を覆う層間絶縁膜9の上層に配線10を形成するとともに、その配線10間の間隔が広い領域にダミー配線11を配置する。また、ダミー配線11はスクライブ領域にも配置される。さらに、ダミー配線11は、ボンディングパッドの周辺領域およびマーカの周辺領域には、配置されない。また、MISFETのゲート電極と同層にダミーゲート配線を設ける。また、浅溝素子分離領域にダミー領域を向ける。これらダミー部材を設けた後に、CMP法で絶縁膜を平坦化する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路におけるグローバル配線の迂回を解消しながら、回路規模の増大を抑制すること。

【解決手段】ハードマクロ10は、入力端子IN_PSと、出力端子OUTと、内部回路20と、セレクタ30とを備える。内部回路20は、出力端子OUTにつながるリピータ25を有する。また、内部回路20は、第1モード時には活性化されて上記リピータ25を通して出力端子OUTに内部信号を出力し、一方、第2モード時には非活性化される。セレクタ30は、当該リピータ25の前段に設けられる。このセレクタ30は、第1モード時には内部回路20から受け取る内部信号をリピータ25に出力する一方、第2モード時には入力端子IN_PSに入力される入力信号をリピータ25に出力するように構成されている。

(もっと読む)

半導体装置

【課題】ヒューズ切断処理時間を短縮できるヒューズ素子を提供する。

【解決手段】ヒューズ素子1の第1切断可能配線3、第2切断可能配線5及び第3配線7は、レーザースポット11のスポット径Rよりも小さい線幅Wをもつ。第1切断可能配線3、第2切断可能配線5は、スポット径Rよりも長い長さL1、L2をもつ。第1切断可能配線3の一端、第2切断可能配線5の一端及び第3配線7の一端は、ヒューズ素子1の切断可能交差部9に接続されている。切断可能交差部9はスポット11のサイズよりも小さい平面サイズの一辺の長さが寸法Wの正方形に形成されている。第1切断可能配線3の一端、第2切断可能配線5の一端及び第3配線7の一端は、互いに切断可能交差部9の異なる辺に接続されており、互いに接触していない。ヒューズ素子1は、第1切断可能配線3からなるヒューズと第2切断可能配線5からなるヒューズが直列に接続された回路と等価である。

(もっと読む)

半導体装置の製造方法、製造プログラム、及び半導体装置

【課題】回路規模の増大を抑制しつつ、素子破壊によってノード間の電気的接続を制御する電流制御素子を有する半導体装置の信頼性を高める。

【解決手段】本発明による半導体装置の製造方法は、半導体ウエハ1上に形成された素子特性抽出用パタン30の素子特性を測定するステップと、測定された素子特性を、素子特性抽出用パタン30に対応付けられた電流制御素子20の素子特性として抽出するステップと、抽出された素子特性に基づいて、半導体ウエハ1上におけるノード間に形成された電流制御素子20に供給するエネルギーを設定するステップと、設定されたエネルギーを電流制御素子に供給し、電流制御素子の素子破壊によってノード間の電気的接続を不可逆的に制御するステップとを具備する。

(もっと読む)

半導体集積回路評価方法、半導体集積回路、および半導体集積回路評価装置

【課題】大規模な半導体集積回路(DMA−TEG等)における不良トランジスタの検出と、不良トランジスタのトランジスタ特性の測定を高速で行うことができる、半導体集積回路評価方法を提供する

【解決手段】本発明の半導体集積回路評価方法においては、評価セルアレイ中の被評価トランジスタの閾値Vthの電圧が、閾値Vth電圧の正規分布曲線に対して、5σ(σは標準偏差)以内の分布から外れたものを選別する。そして、閾値Vthの電圧が5σ(σは標準偏差)以内の分布から外れた被評価トランジスタに対して、トランジスタ特性の測定を行う。

(もっと読む)

回路設計装置および回路設計プログラム

【課題】GUI機能を利用しスタティックノイズの改善を効率よく行なえるようにする。

【解決手段】ノイズチェック結果に基づき回路設計を行なうものであって、表示部30と、前記表示部30の制御を行なう表示制御部と、注目配線を指定する指定部と、前記指定部によって指定された前記注目配線のノイズチェック対象となる配線区間を有する全ての配線を、影響配線として、配線結果を保持するデータベースから抽出する影響配線抽出部とを有している。そして、前記表示制御部は、前記注目配線と前記影響配線抽出部によって抽出された前記影響配線とを前記表示部30で表示する制御を行なう。

(もっと読む)

回路設計支援装置、回路設計支援装置の制御方法及び回路設計支援プログラム

【課題】製造ばらつき及び環境変動等のパラメータの条件の変動に対して、耐性の強い信号パスの回路設計を支援すること。

【解決手段】本発明にかかる回路設計支援装置は、信号パスに配置される複数の回路の配置情報を決定するものであって、信号パスに配置される前段回路と後段回路の間を接続する配線の取り得る複数の配線長ごとに、複数のパラメータの所定の条件における信号パスの遅延時間から、複数のパラメータの個別の条件の変動が遅延時間に与える影響の度合いである影響度合を算出する算出手段と、算出された影響度合に基づいて信号パスの配置情報を決定する決定手段と、を備える。

(もっと読む)

半導体集積回路装置及びその設計方法

【課題】フリップチップ構造を有する半導体集積回路装置において、チップサイズを縮小して製造コストを削減できるようにする。

【解決手段】半導体集積回路装置は、複数の入出力セル105を有する半導体チップ100と、半導体チップの表面上に形成された複数のパッド101、102と、半導体チップ100の表面上に形成され、且つ複数の入出力セル105の少なくとも一部と複数のパッド101、102の少なくとも一部とを電気的に接続するパッド間配線103、104とを優している。複数のパッド101、102は、半導体チップ100の中央部おいて四角格子状に配置され、且つ、半導体チップ100の4つの隅部のうちの少なくとも一隅部において千鳥状に配置されている。

(もっと読む)

CAD装置、インダクタの巻き数求め方法、プログラム及び記憶媒体

【課題】本発明は、高速にインダクタの巻き数を求めることが出来るCAD装置、インダクタの巻き数求め方法、プログラム及び記憶媒体を提供することを課題とする。

【解決手段】CADデータ表示部22が表示したレイアウト表示上で、インダクタ位置指定部23によって、ユーザにインダクタの位置を指定させる。この頂点抽出部24は指定位置の範囲内の頂点の数を求め、巻き数計算部25はこの頂点の数からインダクタの巻き数を算出する。

(もっと読む)

設計支援装置、設計支援方法、および設計支援プログラム

【課題】タイミングドリブン配置された順序セルのタイミングを維持しながら消費電力の低減化を図ること。

【解決手段】まず、初期情報を取得する(S1801)。つぎに、順序セルがタイミングドリブン配置されたセル配置可能領域に、所定数のROW領域候補を設定する(S1802)。そして、ランキング処理を実行して(S1803)、ROW領域候補riの優先順位を付ける。このあと、実際にチップに使用するROW領域の必要個数Nを算出する(S1803)。ROW領域候補の中からROW領域を決定する(S1805)。そして、順序セルの整列化処理を実行する(S1806)。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】チップサイズが小さくなるように、半導体集積回路を設計できるレイアウト設計装置を提供する。

【解決手段】ネットリスト及び遅延情報に基づいて、タイミング解析を行うタイミング解析部103と、タイミング解析にタイミングエラーが生じる場合、タイミングエラーに関連している調整対象セルを抽出する調整対象抽出部104と、第1セル枠は調整対象セルの境界線であり、第2セル枠の外側に第1拡散領域を有する複数の補強フィルセルを格納する補強フィルセルライブラリ105と、第2セル枠は複数の補強フィルセルの各々の境界線であり、調整対象セルに隣接する通常フィルセルと同じ大きさの第1補強フィルセルを、複数の補強フィルセルから抽出し、第1セル枠と第2セル枠とが隣接配置するように通常フィルセルを第1補強フィルセルに置き換え、トランジスタと第1拡散領域とを接続するセル置換部106とを具備する。

(もっと読む)

レイアウト検証方法及びレイアウト検証装置

【課題】レイアウト検証の際に論理回路データを作成しなくとも、レイアウト設計データの不具合を容易に検証でき、また、バイアス条件等の測定条件設定を、短時間で行うことができるレイアウト検証方法及びレイアウト検証装置を提供する。

【解決手段】ネットリスト抽出部111は、レイアウト設計データ11から、トランジスタ、抵抗等の素子をネットリストとして認識、仮ネットリストの抽出を行う。また、ネットリスト生成部112は、仮ネットリストに縮退、フィルタ処理を行い、レイアウト設計データ11に対応する素子のネットリストを生成する。測定ピン番号抽出部113は、プローブ針座標データ13から電極パッドの座標とプローブ針番号を抽出する。また、出力ファイル生成部115は、ネットリストの素子端子名にプローブ針番号が割り当てられた出力データを生成し、出力処理部180は出力データを表示部190へ表示する。

(もっと読む)

回路設計方法、回路設計プログラム、回路設計装置および半導体装置

【課題】新たなパラメータを用いた論理設計を行うことにより、回路設計の精度を向上させることの可能な回路設計方法、回路設計プログラムおよび回路設計装置を提供する。

【解決手段】命令セット22に基づいて動作合成を行うことによりRTLデータ23が生成されたのち(S1)、RTLデータ23とライブラリ25とに基づいて論理合成を行うことによりネットリスト24が生成される(S2)。ネットリスト24に基づいて回路レイアウト26が生成されたのち(S3)、回路レイアウト26と各種テーブルとを対比して各種データが導出される(S4〜S7)。各種データとRTLデータ23とに基づいて新ネットリスト34Aが生成されたのち(S8)、新ネットリスト34Aに基づく論理回路シミュレータ上の動作が仕様を満たすか否かが検証される(S9)。その結果、仕様が満たされなかった場合には、検証結果に基づいてレイアウト設計がやり直される。

(もっと読む)

半導体装置

【課題】従来のプログラマブルな半導体装置であるFPGAやMPLDはコストパフォーマンスが悪く、かつ長い信号線に対する配慮が不充分であった。

【解決手段】メモリと、アドレス−データ対を有する複数のMLUTから構成されるMLUTブロックにフリップフロップを内蔵した。また隣接するMLUT間の近距離配線には交互配置配線を導入し、隣接していないMLUT間の配線には専用の離間配線、更にはトーラス配線網を設けた。

(もっと読む)

半導体集積回路装置

【課題】低電力制御が行われるエリアバンプ構造の半導体集積回路装置に最適化した電源供給を提供する。

【解決手段】論理ブロック領域2において、電源スイッチ部14は、論理ブロック領域2,3の両辺側にそれぞれレイアウトするのではなく、論理ブロック領域2の内側に分割して等間隔でレイアウトし、各々の基準電位VSS用のパッド11との距離が短くなるようにする。たとえば、論理ブロック領域2では、電源スイッチ部14が3つに分散されて配置されており、各々のパッド11と電源スイッチ部14との距離が短くなるようにしている。これにより、エリアバンプ構造の半導体集積回路装置における電源供給の電圧低下を大幅に低減することができる。

(もっと読む)

半導体集積回路のレイアウト装置、設計支援方法及び製造方法

【課題】低コストで半導体集積回路の製造が可能な半導体集積回路のレイアウト装置を提供する。

【解決手段】半導体集積回路内の回路部分の配置及び配線を行う半導体集積回路のレイアウト装置において、ライブラリ、デザインルール、レイアウト、ネットリストを読み込む入力部と、ライブラリ、デザインルール、レイアウト、ネットリストの情報をもとに、表示部にレイアウト表示を行うための処理を行い、また、操作部からの操作により制御が行われる本体部と、本体部を制御するための操作を行う操作部と、表示画面においてレイアウト表示するとともに、表示画面には表示されないものであって、レイアウト表示されている配線と電気的に接続される回路情報を表示するための表示部を有することを特徴とする半導体集積回路のレイアウト装置を提供することにより上記課題を解決する。

(もっと読む)

101 - 120 / 567

[ Back to top ]