Fターム[5F064EE08]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 配線長 (567)

Fターム[5F064EE08]に分類される特許

21 - 40 / 567

レイアウト設計方法及びレイアウト設計装置

【課題】チップ面積を小さくすることのできるレイアウト設計方法を提供する。

【解決手段】レイアウト設計方法は、所定のタイミング制約F1を満足させるように、セルを配置し、低抵抗配線が形成される第1配線層を使用してセル間のパスの接続配線を形成する処理(ステップS2〜S4)を有する。また、レイアウト設計方法は、タイミング制約F1を満足させたまま、パスの接続配線のうち、セル間に配置されるバッファ回路によって区切られる複数のステージ中の少なくとも一つのステージに対応する接続配線におけるレシーバ側からの一部を、第1配線層から該第1配線層よりも配線遅延が大きくなる第2配線層に置き換えて形成する配線置換処理(ステップS5)を有する。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置にダミーパタンを配線空隙に効率よく製造容易的に形成する。

【解決手段】多層配線構造の半導体装置において、狭い配線空隙(Area_S1)に、広い配線空隙(Area_S2)に形成されたダミーパタン(22,23)と異なる向きのダミーパタン(21)が形成されている。

(もっと読む)

半導体集積回路及びそのレイアウト方法

【課題】短時間でレイアウト構成を行うことができる半導体集積回路及びそのレイアウト方法を提供すること。

【解決手段】本発明の一態様である半導体集積回路100は、出力回路11、信号分岐用セル12、マスタ回路13及びチェッカ回路14を有する。出力回路11は、出力信号を出力する。信号分岐用セル12は、出力信号を分岐した第1及び第2の出力信号を出力する。第1及び第2の出力信号に分岐される前の出力信号が伝搬する共通線部である第1の配線16の長さは、制約値X以下である。マスタ回路13は、第1の出力信号を受ける。チェッカ回路14は、第2の出力信号を受け、マスタ回路13と冗長構成回路を構成する。

(もっと読む)

設計支援プログラム、該プログラムを記録した記録媒体、設計支援方法、および設計支援装置

【課題】半導体集積回路の長寿命化、および設計期間の短縮を同時に実現すること。

【解決手段】設計支援装置700は、検出部701により、レイアウト情報によって表現された設計対象回路から配線間を接続するビアを検出する。つぎに、決定部702により、配線間を接続しないダミービアの接続位置を、検出部701によって検出されたビアに接続された配線のうち、少なくとも一つの配線上の位置に決定する。そして、挿入部704により、決定部702によって決定された接続位置にダミービアを挿入する。

(もっと読む)

自動配置配線装置および自動配置配線方法

【課題】複数の電源電圧を有する半導体装置設計の自動化による作業工数の削減とレイアウト面積の省面積化を図ることが可能な自動配置配線装置を提供する。

【解決手段】処理部は、自動配置の結果から複数のセル間を接続する複数の配線経路であって、第1のパワードメイン中のセルから第2のパワードメイン中のセルへ接続される配線経路を抽出する(16)。処理部は、第1のパワードメインと第2のパワードメインとの各々の動作モード毎の電源活性情報を抽出し(17)、第1のパワードメインと第2のパワードメインとが活性状態であるときに活性状態である第3のパワードメインを抽出し(18)、特定セルの仕様項目違反を解消するために、第3のパワードメインに追加セルを挿入し(19)、かつ、第1のパワードメイン中の特定セルと第2のパワードメイン中の特定セルとの間を追加セルを経由して配線する(22)。

(もっと読む)

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

クロックツリー設計装置及びクロックツリー設計方法

【課題】クロックレイテンシを最小にする条件下において、クロックスキュー及びバッファ数を比較的少なくする。

【解決手段】実施形態のクロックツリー設計装置は、ターゲットシンクからのマンハッタン距離と最遠シンクからのマンハッタン距離とが等しくなる等距離点の集合を求める等距離点集合算出部と、クロックパスのパス長を最短のマンハッタン距離にするパス設定ブロック領域を設定するパス設定ブロック設定部と、等距離点の集合のうちパス設定ブロック領域内でクロックソースから最も遠い距離の点を分岐点とする分岐点設定部と、クロックソースから分岐点までのパス設定ブロック領域内にターゲットシンクと最遠シンクとの共有パスを設定すると共に、分岐点からターゲットシンクまでのクロックパス及び分岐点から最遠シンクまでのクロックパスをパス長が最短のマンハッタン距離となるように設定するパス設定部とを具備する。

(もっと読む)

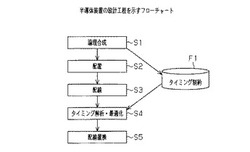

レイアウト設計方法、レイアウト設計プログラム及びレイアウト設計装置

【課題】被クリップセルとクリップセル間の配線引き回しを抑え、配線引き回しに起因した不具合を回避する。

【解決手段】レイアウト設計において、ネットリストを用い、被クリップセルと、その被クリップセルに接続されるクリップセルとを抽出し(ステップS1)、抽出された被クリップセルとクリップセルとを関連付けた関連付け情報を生成する(ステップS2)。そして、生成された関連付け情報に基づき、被クリップセルとクリップセルとを隣接させる等して一体で配置し(ステップS3)、配置された被クリップセルとクリップセルとを配線で接続する(ステップS4)。

(もっと読む)

信頼性を改良するための導電性層間のビア

【課題】ビアの信頼性を改良するための技術を提供する。

【解決手段】別の半導体デバイスが、複数の導電性配線(12−20)を含む第1層(21)および第2層(33)を含み、複数の非機能的ビアパッド(34)が、第2層または第1層と第2層との間に含まれる。複数のダングリングビア(40)は、第1層の特定の領域内に含まれる。ダングリングビアは、第1層の1つまたは複数の配線をビアパッドの対応する一つに接続する。

(もっと読む)

階層レイアウト設計装置、階層レイアウト設計方法およびプログラム

【課題】複数の下位階層ブロックに跨るセル同士を各下位階層ブロックに設けた端子を経由して相互に接続する場合に、セル間を結ぶ経路が迂回経路となること。

【解決手段】階層レイアウト設計装置は、第1の下位階層ブロックに含まれるセルから出力された信号を受信する出力端子を該セルの近傍に配置する出力端子配置部と、第2の下位階層ブロックに含まれる複数のセルへ前記出力端子から出力された信号を供給する入力端子を、該複数のセルを囲む最小の矩形領域の境界上であって、前記出力端子が配置された箇所からの距離が最短の箇所に配置する入力端子配置部と、を備えている。

(もっと読む)

半導体集積回路、半導体チップ、及び半導体集積回路の設計手法

【課題】容易な設計により、小規模な構成でクロックスキューを抑制させる半導体集積回路を提供する。

【解決手段】ラッチ回路31〜316のデータ入力端子とデータビットの供給元PDとの間に、クロック信号CLLの供給元PCD及びラッチ回路のクロック入力端子間のクロック信号経路中に含まれている論理素子の個数と同一数だけ当該論理素子を直列に接続してなる第1遅延部51,52と、クロック信号経路中の配線の配線長に対応した配線遅延時間と同一長の遅延時間を有する第2遅延部53と、を備える。

(もっと読む)

マクロ用レイアウト検証装置及び検証方法

【課題】マクロのレイアウト情報に基づいて、当該マクロが使用されるLSIのレイアウト設計時に発生する可能性がある設計規則違反を予め検出する。

【解決手段】マクロ用レイアウト検証装置は、マクロの端子にビアコンタクトを配置したと仮定する手段と、ビアコンタクトとマクロ内レイアウトとの関係が設計規則に違反するか否かを判定する手段と、を具備する。

(もっと読む)

チャージアップダメージの検証方法および検証装置

【課題】 配線と非配線とを分けて扱い、マクロ等にも半導体集積回路全体にも適用できるアンテナルールを用いるチャージアップダメージの検証方法等を提供できる。

【解決手段】 配線層毎のアンテナ比の上限値を、注目配線層の階層数と総配線層数とに基づいて設定する第1のステップS10、半導体集積回路のレイアウトデータに基づいて、配線層毎に所与のゲートにチャージアップダメージを与えるノードの面積を演算し、下位の配線層に含まれる同一のノードの面積との積算値を求める第2のステップS20、半導体集積回路のモジュール毎に、注目モジュールに含まれる所与のゲートにチャージアップダメージを与えるノードについて、注目モジュールの最上位配線層までの面積の積算値と所与のゲートの面積とに基づいてアンテナ比を求め、注目モジュールの最上位配線層におけるアンテナ比の上限値と比較する第3のステップS30を含む。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

配線経路作成プログラム及び配線経路作成方法

【課題】ひとつのドライバと複数のドライバを配線するための配線経路を作成するプログラムに関して、総配線長が最小になるような配線経路を、それが複数存在する場合は、その中でも最大DR間配線長が一番小さくなるような配線経路を自動的に求める。

【解決手段】ドライバから各レシーバに向かう複数のベクトルに関して、任意の二つのベクトルからなるベクトルペアについて重複長さを求め、それが最大のものを選択ベクトルペアとする。その選択ベクトルペアについて、途中までを共通化する3種類の結合点を作ってベクトルを共通化し、3種類のベクトルパターンを得る。このような作業を繰り返し、ベクトルの共通化が終了した時点で、各ベクトルパターンを結線候補とする。結線候補の中で総配線長が最小のものを最適配線経路とする。それが複数ある場合は、最大DR間配線長が一番小さいものを最適配線経路とする。

(もっと読む)

集積回路のレイアウト設計方法、レイアウト設計装置、及び設計プログラム

【課題】高駆動素子が含まれている論理素子経路に遅延素子を挿入してホールドタイム違反を解消する際に、セットアップタイム違反が新たに発生することを防止する。

【解決手段】レイアウト設計方法が、第1フリップフロップ101と、第2フリップフロップ102と、第1フリップフロップ101の出力と第2フリップフロップ102の入力の間の論理回路とを含む集積回路について配置及び配線を行うステップと、ホールドタイム違反を検出するステップと、遅延素子302をホールドタイム違反を解消するように挿入するステップとを備えている。遅延素子302を挿入するステップでは、第1フリップフロップ101と第2フリップフロップ102間の論理素子経路に高駆動素子105が配置されているかが確認され、高駆動素子105が配置されている場合、高駆動素子105の出力に直接に接続されないように遅延素子302が配置される。

(もっと読む)

半導体装置

【課題】 データ保持回路を備えた半導体装置において、回路面積の低減及び動作速度の向上を図ること。

【解決手段】 本半導体装置100は、少なくとも1以上の不揮発性のメモリセルFCと、メモリセルFCへの書き込みデータ又はメモリセルFCからの読み出しデータを格納するラッチ回路30とを含み、メモリセルFC及びラッチ回路30がアレイ状に配置された複数の不揮発性メモリ回路20と、複数の不揮発性メモリ回路20におけるラッチ回路30のそれぞれに接続され、データを一時的に保持する複数のデータ保持回路10と、を備える。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】半導体集積回路の遅延時間の変動を抑制すること。

【解決手段】回路設計支援装置1は、選択部1bと配置部1cとを有している。選択部1bは、設計対象の半導体集積回路モデルが備えるレジスタモデル2bにクロック信号を供給するクロック信号線の分岐点P1からレジスタモデル2bのクロック信号入力端子に至る第1の経路と、分岐点P1からレジスタモデル2bのデータ信号入力端子に至る第2の経路の、配線に関する物理パラメータの差分値に基づいて、物理パラメータが異なる配線負荷を有する複数の遅延回路モデルから遅延回路モデルBを選択する。配置部1cは、選択された遅延回路モデルBをデータ信号入力端子に接続されるデータ信号線に配置する。

(もっと読む)

21 - 40 / 567

[ Back to top ]