Fターム[5F064EE26]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699) | 上下位置関係 (479)

Fターム[5F064EE26]に分類される特許

161 - 180 / 479

半導体集積回路装置

【課題】マクロセル上を通過する比較的長い信号配線を形成した場合においてもクロストークノイズの影響を低減し、正常に動作可能な半導体集積回路装置を提供する。

【解決手段】本発明による半導体集積回路装置は、マクロセルが形成されている領域上を通過するように伸長している信号配線に、当該マクロセルとこれに近接する入出力回路との間に形成されたバッファリングセルが接続されている。

(もっと読む)

半導体集積回路、および、スイッチの配置配線方法

【課題】スイッチの配置配線を短時間で容易に行う。

【解決手段】第1電源線(例えば実VDD線)と内部電圧線間に回路セルを有する回路ブロックと、内部電圧線に接続される2本の電圧セル線23A,23Bと、第2電源線(例えば実VSS線)に接続される2本の電源セル線24A,24Bと、スイッチ制御線29に接続される制御セル線25と、トランジスタ(TR1,TR2)と、を有するスイッチセル20Nが、回路ブロック1の周囲の四方全てに配置される。各スイッチセル20Nにおいて、制御セル線25がセル中心を通り一方向に配置され、2本の電圧セル線23A,23Bと、2本の電源セル線24A店Bの各々が、制御セル線25と並行に、かつ、制御セル線25を挟んで制御セル線25から等距離の位置に互いに並行に配置されている。

(もっと読む)

集積回路装置のレイアウト方法、集積回路装置のレイアウトプログラム、集積回路装置のレイアウトシステム、集積回路装置及び電子機器

【課題】チップ面積の増加を伴わずに電源補強を実現することができる集積回路装置のレイアウト方法等を提供すること。

【解決手段】本発明の集積回路装置のレイアウト方法は、機能セルが配置されていない未配置領域を探索するステップ(ステップS12)と、未配置領域に、少なくとも一部が第1、第2のポリシリコン配線パターンによりそれぞれ形成された第1、第2の電源補強線を含む第1、第2の電源補強セルを配置するステップ(ステップS14)と、を含む。ステップS14において、第1、第2のポリシリコン配線パターンを第2、第1の電源供給線とそれぞれ交差させて、第2の方向に沿って、第1、第2の電源補強線を介してそれぞれ2つの第1の電源供給線及び2つの第2の電源供給線を接続する2つの配線パターンの少なくとも一方が形成されるように、少なくとも2つの第1、第2の電源補強セルの少なくとも一方を第2の方向に沿って並べて配置する。

(もっと読む)

集積回路装置のレイアウト方法、集積回路装置のレイアウトプログラム、集積回路装置のレイアウトシステム、集積回路装置及び電子機器

【課題】チップ面積の増加を伴わずに電源補強を実現することができる集積回路装置のレイアウト方法等を提供すること。

【解決手段】本発明の集積回路装置のレイアウト方法は、機能セルが配置されていない未配置領域を探索するステップ(ステップS14)と、未配置領域に、少なくとも一部が第1及び第2のポリシリコン配線パターンによりそれぞれ形成された第1及び第2の電源補強線と、を含む電源補強セルを配置するステップ(ステップS16)と、を含む。ステップS16において、第1及び第2のポリシリコン配線パターンを第2の電源供給線及び第1の電源供給線とそれぞれ交差させて、第2の方向に沿って、第1の電源補強線及び第2の電源補強線を介してそれぞれ2つの第1の電源供給線及び2つの第2の電源供給線を接続する2つの配線パターンの少なくとも一方が形成されるように、少なくとも2つの電源補強セルを第2の方向に沿って並べて配置する。

(もっと読む)

半導体集積回路装置の設計方法、設計装置および半導体集積回路装置

【課題】フリップチップスタイルのLSI設計において、LSI上に配置されたパッドからの応力による影響を考慮した設計方法ならびに半導体装置を提供する。

【解決手段】パッドからの応力の影響を考慮する方法として2種類の方法を提供する。1つは、応力の影響によるセルの遅延ばらつき値を求め、セルに付与することで応力の影響を考慮したタイミング解析などを行う。そしてこの解析結果を用いて、設計を行いパッドからの応力の影響をパッド下のビア、配線、セルなどに与えないようにするために、パッド下にはビアを配置しないなどの物理的構造を用いる。

(もっと読む)

半導体チップ

【課題】周辺部に外部接続用パッドが3列以上千鳥状配置された半導体チップにおいて、チップ面積を抑えつつ、電源またはグランドを安定供給する。

【解決手段】最外列に配置された外部接続用パッド11が、内部コア回路の電源用またはグランド用パッドとして用いられている。この外部接続用パッド11には、外側から2列目に配置された外部接続用パッド12がパッド用メタルと同層のメタル15で接続されている。内部コア回路への電源供給配線の抵抗は、パッド11からの抵抗R2とパッド12からの抵抗(R3’+R3”)との並列抵抗となり、その値は抵抗R2に比べて格段に小さくなる。これにより、内部コア回路の電源のIRドロップに起因する回路の誤動作を防止することができる。しかも、必要となるI/Oセル9a,9bは2個のみである。

(もっと読む)

半導体装置

【課題】ワイヤボンディングを採用する半導体装置において、製品展開に要する時間を短縮することのできる技術を提供する。

【解決手段】第1の方向に沿って一列に配置された複数のボンディングパッド4からなるボンディングパッドセット(第1の列L1)と第1の方向に沿って一列に配置された複数のボンディングパッド5からなるボンディングパッドセット(第2の列L2)とが、第1の方向と直交する第2の方向に沿って設けられており、第1の列L1を構成する各々のボンディングパッド4と第2の列L2を構成する各々のボンディングパッド5とは第2の方向と同一線上に並んで設けられており、第1の列L1を構成する複数のボンディングパッド4または第2の列L2を構成する複数のボンディングパッド5の全部または一部にボンディングワイヤを接続する。

(もっと読む)

半導体集積回路のレイアウト設計装置及びレイアウト設計方法

【課題】各層のメタルの疎密を解消することができるとともに、クロストークによる遅延変動を確実に防ぎ、遅延算出の精度を向上させることができるレイアウト設計装置及びレイアウト設計方法を提供する。

【解決手段】各層に所望の配線構造を形成するための配線前設計データ401に基づいて、各層の配線混雑度402を算出する算出処理部1と、n層6の選択領域における配線混雑度402が、n−1層7及びn+1層8よりも低い場合に、n−1層7の下層又はn+1層8の上層であって、電源を有する層を選択する選択処理部2と、当該電源とn−1層7又はn+1層8とを接続する設計データを配線前設計データ401に追加して追加後設計データを生成する追加処理部3と、を備え、追加後設計データに基づいて配線及びメタル生成を行うように構成した。

(もっと読む)

回路抽出装置及び方法

【課題】レイアウトデータから寄生素子を含む回路図を抽出する際に、シミュレーションのプローブポイントとして注目するノードを、抽出された回路図において容易に識別することのできる回路抽出装置を提供する。

【解決手段】回路抽出装置10は、擬似パターン配置部11、擬似素子配置部12、寄生素子抽出部13、出力部14を備える。擬似パターン配置部11は、レイアウトデータを入力し、1又は2以上の擬似パターンを配置する。擬似素子配置部12は、レイアウトデータに対する回路図を入力し、前記擬似パターンのそれぞれに対応する擬似素子を配置する。寄生素子抽出部13は、擬似パターンの配置されたレイアウトデータに基づいて寄生素子を抽出する。出力部14は、寄生素子を擬似素子の配置された回路図へ合成して出力する。

(もっと読む)

半導体集積回路のレイアウト作成装置及びレイアウト作成方法

【課題】多層構造の半導体装置を製造する製造プロセスに基づいて、複数層のレイアウトデータを検証するレイアウト検証処理のプロセスを適宜変更し、レイアウト検証処理の負担を軽減し、レイアウトデータの品質を向上させる半導体集積回路のレイアウト作成装置及びレイアウト作成方法を提供する。

【解決手段】半導体集積回路のレイアウト作成装置は、論理回路図設計部と、レイアウトデータ作成部と、論理接続検証部と、デザインルール検証部と、層間レイアウト検証部と、レイアウトデータを出力するデータ出力部と、多層構造の前記半導体集積回路をチップ化する際の製造プロセスに基づいて、前記論理接続検証部、前記デザインルール検証部、及び前記層間レイアウト検証部において実行される検証処理のプロセスを設定する検証プロセス設定部と、を備える。

(もっと読む)

半導体装置

【課題】 小さな占有面積でESD保護用のN型MOSトランジスタを形成し、できる限り多くの割合の静電気パルスを引き込みつつ内部回路素子には伝播させない、あるいは早く大きな静電気パルスを遅く小さな信号に変化させてから内部回路素子へ伝えるようにした、十分なESD保護機能を果たせるESD保護素子を有する半導体装置を得る。

【解決手段】 外部接続端子と内部回路領域との間にゲート電位をグランド電位に固定したESD保護用のN型MOSトランジスタを有する半導体装置において、外部接続端子はESD保護用のN型MOSトランジスタのドレイン領域上に形成し、ドレイン領域はチャネル領域を介してソース領域に囲まれるようにした。またドレイン領域の平面形状は角部分が丸められた形状とした。

(もっと読む)

半導体集積回路

【課題】 本発明は、櫛型容量の下方にその他のアナログ回路素子を配置することで、より小型化されたアナログ回路を搭載できる半導体集積回路を提供することを目的とする。

【解決手段】 本発明に係る半導体集積回路は、電極1及び電極2を有し、導線層5〜8から構成される櫛型容量3と、半導体基板11と、櫛型容量3の下方に配置される導線層9、10と、トランジスタ12、13と、抵抗素子14、15とを有し、導線層9、10によって、トランジスタ12、13及び抵抗素子14のいずれかの端子が、櫛型容量3の電極1又は電極2、櫛型容量3の下方に配置される他のアナログ回路素子、櫛型容量3の下方に配置されない抵抗素子15、電源23、グラウンド、または外部信号線24に接続されるようにした。これにより、櫛型容量3の下方にトランジスタ12、13及び抵抗素子14を配置することができる。

(もっと読む)

レイアウト設計方法、レイアウト設計プログラム、及びレイアウト設計装置

【課題】マクロブロック外側の外周部において、電源配線とマクロブロックとを共に含む領域の配線面積率が所定の制約条件を満足していない場合には、電源配線のレイアウトをやり直さなければならないという課題があった。

【解決手段】コンピュータを用いて半導体集積回路のレイアウトを行う方法によって解決することができる。この方法は、ハードブロックをレイアウトする工程と、電源配線をレイアウトする工程と、ハードブロックと電源配線とがメタル密度違反を生じさせていないかを検証する工程と、メタル密度違反が発見された場合には、レイアウトの修正を行って、メタル密度違反を解消する工程と、信号線をレイアウトする工程とを含む。信号線をレイアウトする工程を、電源配線によるメタル密度違反を解消する工程の後に行う。

(もっと読む)

半導体回路装置

【課題】 半導体回路装置の面積を増大させることなく、電源電圧安定化のための十分な容量を確保することができる半導体回路装置を実現する。

【解決手段】 トランジスタセル1の一方の端部は、グランド線6、絶縁層9、電源線7の順に半導体基板8の一の面に積層されてなるため、グランド線6および電源線7の配線方向の長さに対応した容量C1を形成することができるので、電源安定化に必要な十分な容量を確保することができる。また、グランド線6の上方に電源線7が積層されているため、容量を形成するための領域をトランジスタセル1間に確保する必要がない。さらに、グランド線6および電源線7を配置するために必要な面積を、グランド線6および電源線7を並列して配置する構造よりも小さくすることができる。

(もっと読む)

半導体集積回路装置

【課題】IOスロットを無駄にすることなく、内部回路に対して電源供給することが可能な半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、配線層を下から第1の共通配線層101a、カスタマイズ層102、第2の共通配線層101bの3層構造とした。第2の共通配線層101bには、外部から電源が供給される電源パッド1aと接続される内部電源ラインが形成されている。内部電源ラインは、電源パッド1aと同一層に形成されるとともに、汎用ロジックセルにより構成される内部回路領域10にまで延在している。

(もっと読む)

半導体装置の製造方法

【課題】歩留りが高く、且つ、配線間容量を十分に低減できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板上に絶縁膜を形成する工程と、絶縁膜の内部に複数の配線溝を形成する工程と、複数の配線溝の内部に複数の配線を形成する工程と、絶縁膜及び複数の配線の上に、複数の配線間の領域のうち選択的に領域を露出する開口部を有するレジストマスクを形成する工程と、レジストマスクを用いたエッチングにより、複数の配線間の領域のうち選択的に露出した領域の絶縁膜を除去してエアギャップ溝を形成する工程と、レジストマスクを除去した後に、複数の配線上を覆うように層間絶縁膜を堆積することによってエアギャップを形成する工程とを含む。

(もっと読む)

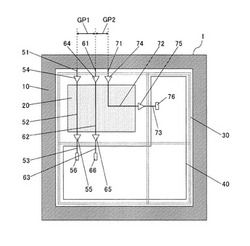

集積回路装置

【課題】内部の配線を流れる電流の大きさを測定することができる集積回路装置を提供する。

【解決手段】集積回路装置1において、基板11に3層の配線層を積層する。そして、最上層の配線層に、コ字形状の主配線31を形成し、その下の2層の配線層に、配線とビアによりコイル32、33を形成する。すなわち、コイル32、33は主配線31の下方に位置し、主配線31に対して固定されている。コイル32、33の形状及び巻き方向は、相互に同一である。コイル32は主配線31の部分31aの直下域に配置し、コイル33は部分31bの直下域に配置する。そして、(端子T3→配線35→コイル33→配線34→コイル32→配線36→端子T4)からなる電流経路を形成し、この電流経路に発生する起電力に基づいて、主配線31に流れる電流の大きさを測定する。

(もっと読む)

半導体チップ、及び半導体装置

【課題】半導体チップのサイズを拡大せずに、高機能化を実現可能な半導体チップを提供すること。

【解決手段】本発明の一態様に係る半導体チップは、半導体基板5上に多層配線、及びシールリング1構造を備える半導体チップ101であって、シールリング1より内側に区画される内部領域2のみならず、内部領域2より外側に区画される額縁領域3に、チップ内部回路として動作可能な信頼性が確保された半導体素子12が配設されている。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

集積回路の設計方法及び設計装置

【課題】好適な配線レイアウトを有する半導体集積回路を実現可能な新たな設計手法を提供する。

【解決手段】半導体集積回路の設計方法であって、前記集積回路のレイアウト設計用の設計データを保持し、前記集積回路を構成する配線のスイッチング確率の情報を保持し、前記配線の配置を、前記設計データと前記スイッチング確率とに基づいて決定することを特徴とする設計方法。

(もっと読む)

161 - 180 / 479

[ Back to top ]