Fターム[5F064EE48]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線(又は配線間)の物理的性質 (2,766) | 熱発生 (83)

Fターム[5F064EE48]に分類される特許

1 - 20 / 83

半導体装置

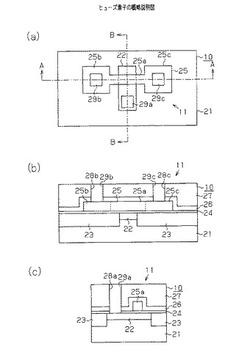

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

半導体集積回路の設計方法、設計プログラム

【課題】半導体集積回路の設計において、EM検証結果がNGとなる確率を低減する。

【解決手段】半導体集積回路の設計方法は、(A)設計対象回路のネットリスト中のネットに仮の寄生容量及び0個以上の仮の寄生抵抗が付加された寄生RC付きネットリストを作成するステップと、(B)寄生RC付きネットリストを用いて回路シミュレーションを行い、ネットにつながるそれぞれの素子端子の電流である素子端子電流及び仮の寄生容量の電流である寄生容量電流を算出するステップと、(C)寄生容量電流をそれぞれの素子端子に分配することによって、素子端子電流の値を変更するステップと、(D)変更後の素子端子電流に基づいて、ネットに関する配線幅制約を算出するステップと、を含む。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

半導体装置における電流による配線破壊箇所の予測方法

【課題】半導体装置の電流による配線破壊箇所の予測方法において、解析時間を短縮する。

【解決手段】下層配線14A,14Bをそれぞれ一つの直列抵抗で、第1の下層ビア15A,第2の下層ビア15Bを1個の抵抗で、第1の上層ビア17A、第2の上層ビア18Bを1個の抵抗で、第1及び第2の上層配線16A,16Bを抵抗ブリッジ回路で、パワートランジスタTRを直列抵抗で、それぞれモデリングしてなる解析モデルをモデリング用計算機により生成する。回路シミュレータ3により、解析モデルにおけるパワートランジスタTRに電流を供給し、解析モデルにおける各抵抗に流れる電流に基づいて、第1及び第2の下層配線14A,14B、第1及び第2の上層配線16A,16Bにおける各抵抗の電流密度を計算し、各抵抗の電流密度と、配線破壊を起こす電流密度閾値とを比較器4により比較することにより、配線破壊箇所を予測する。

(もっと読む)

半導体ウェハ、半導体装置、及び半導体装置の製造方法

【課題】ヒューズメモリを利用したトリミングを行う半導体ウェハにおける各半導体チップの回路面積を小さくする。

【解決手段】半導体ウェハ10におけるシリコン基板上は、複数個のチップ領域TARとこの領域TARを囲むスクライブ領域SARとに区画されている。チップ領域TARには、トリミング対象回路11と、ヒューズ素子Fm(m=1〜2M)と、ヒューズ素子Fm(m=1〜2M)が断線状態であるか否かを検出する検出回路としての役割を果たす定電流源IPm(m=1〜2M)及びインバータINm(m=1〜2M)とが形成されている。スクライブ領域SARには、制御信号に応じてON/OFFが切り換わり、ONとなることによりヒューズ素子Fm(m=1〜2M)を断線させる電流を発生するNチャネル電界効果トランジスタTSm(m=1〜2M)がある。

(もっと読む)

半導体装置の製造方法、半導体装置、設計方法、設計装置、及び、プログラム

【課題】集積度及び歩留まりの低下を抑制しつつ、アニール処理に起因した素子の特性ばらつきを軽減する。

【解決手段】半導体基板1上に素子2、3、5を形成する素子形成工程と、素子形成工程の後、半導体基板1上に、選択的に、半導体基板1よりも高い光吸収率を有するか、又は、半導体基板1への光の吸収率を向上させる機能を有する加熱安定化膜7を形成する加熱安定化膜形成工程と、加熱安定化膜7を有する面側から半導体基板1に光を照射し、半導体基板1に注入された不純物を活性化するアニール工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】電気ヒューズまたはアンチヒューズの保持特性を高める。

【解決手段】半導体装置100は、半導体基板と、該半導体基板の上部に設けられた電気ヒューズ200とを備える。電気ヒューズ200は、直列に接続された第1のヒューズリンク202および第2のヒューズリンク204と、第1のヒューズリンク202の一端および他端にそれぞれ設けられた第1の電流流入/流出端子(第1の端子206)および第2の電流流入/流出端子(第2の端子208)と、第2のヒューズリンク204の一端および他端にそれぞれ設けられた第3の電流流入/流出端子(第2の端子208)および第4の電流流入/流出端子(第3の端子210)とを含む。

(もっと読む)

半導体装置

【課題】本発明は、工程を増やすこと無く、ヒューズカット時間を短縮することができる半導体装置を提供する。

【解決手段】半導体装置は、ヒューズ配線(10)と、加熱用配線(21、22)とを具備し、ヒューズ配線(10)と加熱配線(21、22)とに電圧を印加してヒューズ配線の溶断部を切断する。ヒューズ配線(10)は、回路素子を形成する配線層と同じ層に形成され、電気的に切断されうる溶断部を備える。加熱用配線(21、22)は、回路素子を形成する配線層と同じ層のうちのヒューズ配線(10)より上層の配線層に絶縁層を介して溶断部を複数回横断するように形成され、溶断部の配線幅より広い配線幅を有して溶断部を加熱する。

(もっと読む)

半導体装置のシミュレーション方法及び装置

【課題】電気特性と熱特性の相互の影響を反映した電気-熱連携解析を短い計算時間で実行し、正確な解析結果を得る半導体装置のシミュレーション方法及び装置を提供する。

【解決手段】まず電気特性解析を実行する(ステップS1)。次に電流特性とチップ損失特性の平均化を実行する(ステップS2)。そしてモジュールの3次元形状モデルを作成し、第1の平均化式により得た平均化した電流値を3次元形状モデルの端面に設定してジュール損失解析を実行する(ステップS3)。そして上記ジュール損失解析と第2の平均化式で算出したチップ損失の平均値とを用いて発熱量が等しく時間ステップの長い熱解析特性データを得る(ステップS4)。温度変化が一定値以上に達した時点で電気特性解析のジャンクション温度を再設定し(ステップS5)、以降、電気特性解析から平均化、熱解析までの解析フローを繰り返して装置動作時の温度特性を得る(ステップS11〜S15)。

(もっと読む)

半導体装置

【課題】電源配線と接地配線とを有する半導体装置において、配線の一部における電圧ドロップや、電圧ドロップに伴うマイグレーションの発生を抑制することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面に沿うように層状に広がる電源シート状配線PPWRと、主表面に沿うように、主表面に交差する方向に関して電源シート状配線と一定の距離を隔てて層状に広がる接地シート状配線PGNDと、上記主表面上に形成され、主表面内の一の方向に延在する電源配線PWRと、主表面上に形成され、一の方向に沿う方向に延在し、電源配線PPWRと一定の距離を隔てて形成された接地配線GNDとを備える。上記電源シート状配線PPWRは、電源配線PWRと電気的に接続されており、接地シート状配線PGNDは、接地配線GNDと電気的に接続されている。

(もっと読む)

半導体装置

【課題】面積の増加を抑えつつ、ヒューズ構造体のデータの保持量を増加する。

【解決手段】半導体装置100は、基板(不図示)上に形成されたヒューズ構造体120を含む。ヒューズ構造体120は、第1の配線(122)および第2の配線(124)と、これらを接続するビア123とから構成された電気ヒューズ121と、一端がビア123の側方にビア123に接続して形成された抵抗配線128と、を含む。電気ヒューズ121のビア123は、基板の積層方向において、第1の配線(122)との接続箇所から抵抗配線128との接続箇所までの間に、面内方向の断面積が第2の配線(124)との接続箇所から抵抗配線128との接続箇所までの面内方向の断面積よりも小さい箇所を有する。

(もっと読む)

半導体集積回路

【課題】セル内のメタル配線幅を、設計上許容すべき最大駆動容量Cmax未満の配線幅に設定して、セル内の容量を削減し、セル相互間距離が非常に近い回路などにおいて伝播遅延を所定時間以下に設計することができるようにする。

【解決手段】配線幅以外は全て同一のレイアウトパターンを備えた2種類のスタンダードセル101、151が用意される。一方のスタンダードセル101は、セル内部のメタル配線108、110の配線幅Ws1、Wd1は太く、他方のスタンダードセル151では、セル内部のメタル配線158、160の配線幅Ws2、Wd2は、前記一方のスタンダードセル101の配線幅Ws1、Wd1よりも細く設定される(Ws2<Ws1、Wd2<Wd1)。配線幅の細いセルライブラリ151は、駆動負荷の小さい回路に限定して適用される。

(もっと読む)

半導体装置

【課題】 配線に対するエレクトロマイグレーションの影響を排除する点で、従来の構造は十分とはいえない。

【解決手段】 半導体基板の上に第1の配線が配置されている。半導体基板の上であって、第1の配線とは異なる高さに第2の配線が配置されている。第1のビアが、第1の配線と第2の配線とを高さ方向に接続する。第2のビアが、高さ方向に関して第1のビアとは反対側において第1の配線に接続される。第1の配線は、第1のビアとの接続点から基板面内の第1の方向に延在し、第2のビアは、第1のビアよりも第1の方向にずれた位置に配置されており、第2のビアは、高さ方向に電流を流す電流路として作用しない。

(もっと読む)

プログラマブル論理回路装置及び画像処理装置

【課題】 節電効率を向上させることができるプログラマブル論理回路装置及び画像処理装置を提供する。

【解決手段】 本発明のプログラマブル論理回路装置100は、素子間の接続の変更により再構成される回路を備える複数の再構成領域R0、R1、R2、R3及びR4と、複数の再構成領域R1、R2、R3及びR4の各々に対して、実行させる処理を割り当てて、複数の再構成領域R1、R2、R3及びR4の各々が実行する処理の状態に基づいて、複数の再構成領域R1、R2、R3及びR4を選択的に再構成して節電状態にする管理領域である再構成領域R0と、を有する。

(もっと読む)

試験条件調整装置および試験条件調整方法

【課題】チップ規模の増大を防止すること。

【解決手段】比較部2は、設計対象の半導体回路の第1の動作条件での電圧降下と、第2の動作条件での電圧降下とを例えば、シミュレーションを行って比較する。ここで、第1の動作条件は、例えば、半導体回路完成後の実動作時の動作条件であり、第2の動作条件は、例えば、半導体回路完成後の出荷試験を行うとき(試験時)の動作条件である。調整部3は、第2の動作条件での電圧降下が、第1の動作条件での電圧降下よりも大きい場合、半導体回路の遅延特性に基づいて、第2の動作条件を調整する。

(もっと読む)

1 - 20 / 83

[ Back to top ]