Fターム[5F064HH02]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ハードウェア関係 (668) | ホスト、端末構成 (321)

Fターム[5F064HH02]に分類される特許

1 - 20 / 321

閾値テーブルの作成方法、クロストーク解析の悲観性削減方法、クロストーク解析方法、及びクロストーク解析プログラム

設計支援装置

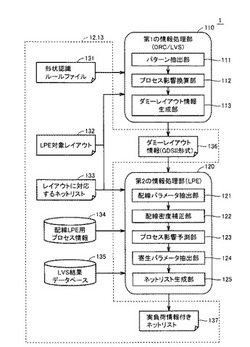

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

配線設計装置、配線設計方法、及びプログラム

【課題】半導体集積回路に対し、ダミーパターン配置後に、ダミーパターンを使用したECO(Engineering Change Order)配線設計を行う。

【解決手段】配線設計装置は、半導体集積回路にダミーパターンを配置し、ダミーパターンをECO配線に変更し、ダミーパターンの再配置及び電気的ショートを発生することなくECO配線を行う。これにより、ECO配線を行う時に、ダミーパターン再挿入や、既存配線とのショートを発生せずに、設計TAT(Turn Around Time)増を抑制することを可能とする。

(もっと読む)

半導体装置の設計方法、半導体装置の設計プログラム、半導体装置の設計装置

【課題】IRドロップの制約を満たしつつチップレイアウトを小型化できる半導体装置の設計方法、半導体装置の設計プログラム、半導体装置の設計装置を提供すること。

【解決手段】本発明の一態様である半導体装置の設計方法は、複数の電源用パッド及び信号用パッドを、半導体チップ上のチップコアの周囲に配置する。そして、複数の電源用パッド及び信号用パッドの数から決まるチップサイズSpと、チップコアの大きさから決まるチップサイズScと、を比較する。その後、Sp≧Scであれば、IRドロップが制約値を満たす限り、配置した複数の電源用パッドのうちの1又は2以上の電源用パッドを削除する。

(もっと読む)

高耐圧MOSFETの回路シミュレーション用モデルの作成方法と装置並びにプログラム

【課題】高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーションの精度を向上させる。

【解決手段】ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、ソース領域のソース拡散層の幅とウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFET1、2と、第2のMOSFET2のソースに一端が接続された第1の可変抵抗素子3を備え、第2のMOSFET2のソースと第1の可変抵抗素子3の他端との接続点をソース端子Sとし、第1及び第2のMOSFETの共通接続したドレイン、共通接続したゲート、共通接続したバックゲートをそれぞれドレイン端子D、ゲート端子G、バックゲート端子Bとするモデルを作成し、モデリング対象の高耐圧MOSFETの電気特性データに基づき、第1の可変抵抗素子3の抵抗値を調整する。

(もっと読む)

シミュレーション装置およびシミュレーション方法

【課題】ESD保護素子を有する半導体回路の回路シミュレーションを高速かつ精度よく行うことができるシミュレーション装置を提供する。

【解決手段】ESD保護素子を有する半導体回路の動作検証を行うシミュレーション装置は、ESD保護素子の等価回路のパラメータファイルを作成する第1のパラメータファイル作成部と、半導体回路内のESD保護素子以外の内部回路のパラメータファイルを作成する第2のパラメータファイル作成部と、作成したパラメータファイルを記憶するパラメータファイル記憶部と、記憶したパラメータファイルを選択するパラメータファイル選択部と、選択したパラメータファイルを利用して半導体回路のネットリストを作成するネットリスト作成部と、ネットリストに基づいて半導体回路の動作検証を行うシミュレーション実行部とを備える。

(もっと読む)

半導体集積回路の設計装置、及び半導体集積回路の設計方法

【課題】チップサイズを縮小することができる、半導体集積回路の設計装置、及び半導体集積回路の設計方法を提供する

【解決手段】下位階層の機能ブロック4に配置された複数のセル間を接続する第一の配線を設計する下位階層配線設計部311と、上位階層の機能ブロック間を接続する第二の配線を設計する上位階層配線設計部312とを備えており、下位階層配線設計部311は、機能ブロック4を複数の小領域4aに分割し、小領域4aごとに機能ブロック4内配線に必要となる必要配線層数Lnを算出して、最下部の配線層から必要配線層数Ln枚の配線層を配線可能領域として同領域内に第一の配線を配置し、上位階層配線設計部312は、第一の配線における配線可能領域以外の機能ブロック4の配線層に第二の配線を配置する。

(もっと読む)

回路設計装置、デカップリング容量効果最適化方法、及びプログラム

【課題】 本発明の課題は、デカップリング容量効果を最適化した回路設計を行うことを目的とする。

【解決手段】 上記課題は、回路を構成する複数のセル間のネット毎の高電位電源側及び低電位電源側の配線容量と、各入力ピンの該高電位電源側及び該低電位電源側の容量とを記憶する記憶部と、前記記憶部に記憶された前記各ネットの配線容量と、前記各入力ピンの容量とを参照して、前記構成における非動作パスに対して、セルの置換前の該セルの組み合せと、セルを置換する際の制約に従った置換後のセルの組み合せのうち、該非動作パスの信号値の遷移状態に応じた、各ネット及び各入力ピンの前記高電位電源側又は前記低電位電源側の容量を加算した総容量に基づいて、該総容量が最大となるセルに置換することによって、デカップリング容量効果を最適化する最適化処理部と、を有する回路設計装置により達成される。

(もっと読む)

半導体集積回路のレイアウト設計装置、方法、及びプログラム

【課題】アナログ回路において最適な配線効率を実現するためのレイアウト設計を可能にする。

【解決手段】機能ブロックを構成する素子をその種類毎にグループ化する。機能ブロック内の素子の配置を各素子の接続関係に基づいて決定する。この時、グループを構成する素子の分割数を考慮してもよい。機能ブロックの配置順序を面積又は幅が大きい順に配置されるように決定する。また、配置順序はユーザの指定により調整できることが好ましい。配置順序と回路全体の接続情報とに基づいて各機能ブロックの配置位置を決定する。

(もっと読む)

半導体集積回路のレイアウト方法、レイアウト装置およびプログラム

【課題】複数の階層ブロックが互いに重なり合うことを許容しつつレイアウト設計を行う際に、設計期間の長期化を防ぐこと。

【解決手段】複数の内部要素をそれぞれ含む複数の階層ブロックを、内部要素を割り当て可能な内部要素リソースが配置された実装領域に対してレイアウトする場合に、第1の階層ブロックと第2の階層ブロックとが重複領域において重なり合うとき、第1の階層ブロックの内部要素のうちの重複領域に含まれる第1の内部要素の個数と、第2の階層ブロックの内部要素のうちの重複領域に含まれる第2の内部要素の個数との合計が、重複領域に含まれる内部要素リソースの個数以下となるように、第1の階層ブロックおよび第2の階層ブロックを配置し、第1の内部要素の個数と第2の内部要素の個数との比に応じて、重複領域に含まれる内部要素リソースを、第1の階層ブロックと第2の階層ブロックに割り当てる。

(もっと読む)

配置配線装置

【課題】効率的にIR−Dropを防止することが可能な配置配線装置を提供すること。

【解決手段】複数のセルを配置した後、セル間の隙間が所定の大きさよりも小さい場合にはセル間の隙間が所定の大きさ以上となるようにセルの配置を変更する(S17)。そして、配置された複数のセルの間に容量セルを挿入し(S15)、配置された複数のセルの配線を行なう(S14,S16)。したがって、効率的にIR−Dropを防止することが可能となる。

(もっと読む)

遅延時間計算プログラム、装置及び方法

【課題】遅延時間計算プログラム、装置及び方法において、回路におけるネットの遅延時間を高精度に計算することを目的とする。

【解決手段】回路内のネットの遅延時間を計算する遅延時間計算処理は、ネットが第1の条件を満たす場合にネットの遅延時間を計算するための第1の遅延計算手順を選択する第1の手順と、第1の手順で第1の遅延計算手順が選択されない場合、第2の条件をネットが満たすか否かに応じて、第1の遅延計算手順及びネットの遅延時間を計算するための第2の遅延計算手順のいずれか一方を選択する第2の手順と、第1の手順或いは第2の手順のいずれかで選択された遅延計算手順によりネットの遅延時間を計算する第3の手順を含むように構成する。

(もっと読む)

クロック設計方法、クロック設計プログラム

【課題】半導体集積回路のクロック設計において、異なる2種類のクロック間の「セル遅延と配線遅延の比率α」の差を抑制する。

【解決手段】半導体集積回路は、第1クロック(CLK1)が供給される第1素子群と、第1クロック(CLK1)と異なる第2クロック(CLK2)が供給される第2素子群と、を備える。クロック設計方法は、第1クロック(CLK1)に関するクロックツリーシンセシスを実施することによって、第1クロックツリー構造10を作成するステップと、第1クロックツリー構造10の少なくとも一部を流用することによって、第2素子群に第2クロック(CLK2)を供給する第2クロックツリー構造20を作成するステップと、を含む。

(もっと読む)

回路のレイアウト装置,処理方法およびプログラム

【課題】 回路のレイアウト装置で,EOEの発生しやすい箇所を推定することを目的とする。

【解決手段】 回路レイアウト装置1は,被研磨対象となる回路の配線パターンを含む回路情報を取得する回路情報取得部11,回路を任意の単位領域でメッシュ状に区切り,各メッシュ領域について,メッシュ領域の配線密度とメッシュ領域の各辺に隣接する周辺領域の各々における配線密度とを示すメッシュ情報を生成するメッシュ情報生成部12,各メッシュ領域について,メッシュ領域と各周辺領域の密度の関係がEOEの発生条件に該当するメッシュ領域を抽出し,そのエラー情報を生成するエラー抽出部13を備える。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラム

【課題】マクロの全端子で配線が引き出し可能かを判定できるレイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラムを提供する。

【解決手段】記憶部11は内部にマクロを含んだ多層回路の階層レイアウトの設計データを記憶する。チャネル数算出部13は設計データに基づいて、マクロの各端子から所定の配線層まで配線を引き出すために使用可能なチャネル数を端子毎に算出する。経路算出部15は算出したチャネル数の少ない端子から順に、端子から所定の配線層まで配線を引き出すための経路を算出する。経路判定部16はマクロの全ての端子について引き出し経路を算出できたか否かを判定する。

(もっと読む)

ノイズ解析装置及びノイズ解析方法

【課題】半導体集積回路で発生するノイズの伝搬を精度よく解析する。

【解決手段】位置特定部2が、解析対象の半導体集積回路のレイアウト情報d1から、高耐圧素子部において、可変容量として設定する、異なる導電型の領域間の接合部の位置を特定し、モデル作成部3が、レイアウト情報d1及び半導体集積回路の製造条件(プロセスパラメータd2)をもとに、ノイズ伝搬路となる配線または基板を、抵抗及び容量を用いてモデル化し、特定された接合部の位置には可変容量を設定する。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

レイアウト検証装置、レイアウト検証方法、及びプログラム

【課題】半導体集積回路のレイアウト検証であって、検証済のレイアウトパタンデータへ部分的に変更を加えた後で行うDRC検証において、検証の対象とならない箇所に対するDRC検証の時間を省略し、アンテナ比のようなDRC検証の時間を短縮する。

【解決手段】検証済のレイアウトパタンデータへ部分的に変更を加えた後で行うDRC検証において、変更箇所から等電位追跡を用いてDRC検証の検証対象箇所を特定する。具体的には、変更前後のレイアウトパタンデータの差分図形を抽出して該差分図形から変更ノードを抽出する。また、変更後のレイアウトパタンデータに対して等電位番号を付与して該等電位番号を参照して該変更ノードと同じ等電位番号を持つ検証対象箇所を抽出する。更に、前抽出された記検証対象箇所に対して、アンテナ比のDRC検証を実行する。

(もっと読む)

1 - 20 / 321

[ Back to top ]