Fターム[5F067EA04]の内容

IC用リードフレーム (9,412) | リードフレーム材料 (399) | 銅(Cu)を主成分とする合金 (256)

Fターム[5F067EA04]に分類される特許

1 - 20 / 256

半導体装置

回路部材、回路部材の製造方法、半導体装置、及び回路部材の表面積層構造

半導体装置およびその製造方法

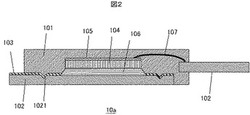

【課題】

半導体素子と基板がはんだで接合され、樹脂でモールドされる半導体装置の信頼性を高めることを目的とする。

【解決手段】

はんだ材106に易揮発金属(Zn、Mg、Sb)を含むはんだを用い、半導体素子104とリードフレーム102を接合し、ワイヤボンディングを実施した後、真空加熱処理を加え、はんだ中の易揮発金属を揮発させ、基板表面に付着してリードフレームとの合金103を形成させることで、基板表面を粗化し、封止樹脂101と基板の密着力を向上させる。

(もっと読む)

半導体装置

【課題】ボンディング面と接続部材との密着性を高くするとともにボンディング面と樹脂封止のための樹脂との密着性を高くし、従来の半導体装置よりも高い信頼性を有する半導体装置を提供する。

【解決手段】半導体チップ110と、半導体チップ110を搭載するための第1リードフレーム120と、ボンディング面132を有する第2リードフレーム130,140とを備え、第2リードフレーム130,140におけるボンディング面132,142は、接続部材150を介して半導体チップ110と電気的に接続され、半導体チップ110、第1リードフレーム120及び第2リードフレーム130,140が樹脂封止により一体化された半導体装置であって、ボンディング面132,142は、第1の粗化処理が施された第1の粗化面であり、めっきを介することなく接続部材150と接続されていることを特徴とする半導体装置。

(もっと読む)

リードフレーム固定材、リードフレーム及び半導体装置

【課題】本発明の目的は、リードフレーム固定材で固定したリードフレームを使用した半導体装置において、リードフレーム固定材に無機フィラーを高充填率で充填しなくても、半田リフロー過程で内部剥離を生じることなく、かつ固定材として高接着性を有するリードフレーム固定材等を提供することである。

【解決手段】本発明のリードフレーム固定材は、1分子中に3個以上のエポキシ基を有するエポキシ樹脂(A)とナフタレン型エポキシ樹脂(B)とを含有し、硬化物とした際のガラス転移温度が178℃以上である。

(もっと読む)

はんだ接続用通電部材、配線用基板及びめっき皮膜の形成方法

【課題】CuまたはCu合金からなる通電部材(電極端子)に、Cu成分を含有しないはんだを使用しても、通電部材側とはんだとが十分な接合強度を発現するはんだ接続用通電部材、配線用基板及びめっき皮膜の形成方法を提供する。

【解決手段】CuあるいはCu合金を含む通電部材1上に、ピンホール7を有する置換Snめっき皮膜5と、電解Niめっき皮膜4と、電解Pdめっき皮膜3と、電解Auめっき皮膜2と、がこの順に積層されているはんだ接続用通電部材である。

(もっと読む)

半導体装置及びその製造方法

【課題】組立性を向上させることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、ダイパッドと、前記ダイパッドに接合された半導体チップと、前記半導体チップを封止する封止部と、前記半導体チップの電極と電気的に接続された第1の面と、前記封止部から露出し前記第1の面と平行な第2の面と、前記封止部から露出し前記第1の面と交差する第3の面と、を有するリードと、を備えている。そして、前記リードは、前記第3の面の平面視において、凹部を有している。

(もっと読む)

半導体装置の製造方法

【課題】パッケージダイシングにおける切削バリの発生を抑制する。

【解決手段】パッケージダイシング工程で、第1段階の切削として、軟らかいレジンブレード11でリード2aを含む封止体4hの一部分を切削することで、切削バリの発生を抑制することができ、その後、第2段階の切削として、硬い電鋳ブレード12を用いて切断残存部4fである樹脂部のみを切断することでブレード本体の摩耗の進展も遅いため、切り残しの発生も低減でき、その結果、半導体装置の信頼性の向上を図れる。

(もっと読む)

光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、および光半導体装置

【課題】本発明は、リードフレーム表面に、樹脂との密着性を向上させるための凹部を形成する場合であっても、ダイシング時のカットストレスによるリードフレームの塑性変形を防止することが可能な、光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、および光半導体装置を提供することを目的とするものである。

【解決手段】リードフレーム表面の前記連結部の近傍以外の領域に前記凹部を形成し、前記連結部の近傍領域には前記凹部を形成しないようにして、前記連結部の近傍領域のリードフレームの厚みを、前記凹部が形成された領域の厚みよりも厚く保つことにより、上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】ボンディングワイヤ長を長くすることなく、ワイヤ流れの発生を抑制することのできる半導体装置の製造方法を提供する。

【解決手段】リードフレーム材1の表面側に形成した金属めっき層3,4をレジストマスクとして表面側からリードフレーム材1に所定深さのハーフエッチング加工を行い、外枠の一部又は全部と導体端子6及び中継端子7とを突出させ、リードフレーム材1に半導体素子8を搭載した後、半導体素子8とそれぞれ対応する導体端子6との間を直接、または中継端子7を中継してボンディングワイヤ9によって接続し、半導体素子8、導体端子6、中継端子7、及びボンディングワイヤ9を含むリードフレーム材1の表面側を樹脂封止し、リードフレーム材1の裏面側に、裏面側に形成された金属めっき層3をレジストマスクとしてエッチング加工を行って、外部接続端子部13を突出させて独立させる半導体装置の製造方法。

(もっと読む)

半導体装置、並びに異形断面条及びその製造方法

【課題】熱放散性や製造容易性に優れ、かつ水分等の異物の侵入を抑えたCSP構造の半導体装置、並びにその半導体装置を構成するリードフレームを形成するための異形断面条及びその製造方法を提供する。

【解決手段】本発明の一態様において、突起3が形成された部分であるアウターリードとしての2つの厚肉部2A、及び2つの厚肉部2Aの間のインナーリードとしての薄肉部2Bを有するリードフレーム5Aと、ボンディングワイヤ12を介して薄肉部2Bに電気的に接続される半導体チップ11と、リードフレーム5A及び半導体チップ11を封止する樹脂パッケージ14と、を含み、リードフレーム5Aの上面及び下面の樹脂パッケージ14に接触する部分に、突起3に平行な線状の微小溝4A、4Bが形成され、微小溝4A、4Bの深さは前記突起の高さよりも小さく、2つの厚肉部2Aの一部が樹脂パッケージ14の底面及び側面に露出する半導体装置を提供する。

(もっと読む)

光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、光半導体装置、および、光半導体装置用リードフレームの製造方法

【課題】本発明は、金属基板の表面側に内部端子と裏面側に外部端子を一体的に有する端子部を、一平面内に複数個、それぞれ互いに電気的に独立して配置し、前記端子部の内部端子と光半導体素子の端子とを電気的に接続し、前記端子部の裏面を外部に露出させるように全体を樹脂封止した樹脂封止型の光半導体装置に用いられる光半導体装置用リードフレームにおいて、垂直方向に対する剥離力に対して樹脂の脱離を防止することが可能な光半導体装置用リードフレーム、樹脂付き光半導体装置用リードフレーム、光半導体装置、および、光半導体装置用リードフレームの製造方法を提供することを目的とするものである。

【解決手段】光半導体装置用リードフレームの表面側に、樹脂との密着性を向上させるための凹部を形成し、前記凹部の内部を、その開口よりも広く形成することにより、上記課題を解決する。

(もっと読む)

リードフレームおよびその製造方法

【課題】ダイパッドの側面およびダイパッドの裏面に半田が流れてしまう不具合を防止することが可能なリードフレームおよびその製造方法を提供する。

【解決手段】リードフレーム10は、金属製のダイパッド11と、ダイパッド11の周囲に設けられたリード部12とを備えている。ダイパッド11は、半導体素子21が搭載される搭載領域15と、搭載領域15を帯状に囲む半田流出防止用の半田流出防止領域16とを含んでいる。半田流出防止領域16は、搭載領域15に対して粗面化されているので、半田部22の流れを半田流出防止領域16で止めることができる。

(もっと読む)

半導体装置の製造方法

【課題】樹脂封止型の半導体パッケージにおいて、半導体チップ搭載用のダイボンディング材のクラックを防止する。

【解決手段】半導体チップCP1を、ダイボンディング材DB1を介してダイパッドDP1の上面f1に搭載し、絶縁性樹脂IR1によって封止する。前記絶縁性樹脂IR1と接触するダイパッドDP1の上面f1を粗面化し、ダイパッドDP1の裏面f2およびアウターリード部OL1は粗面化しない。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リードフレームへ導電性リボンや太線ワイヤなどの接続体をボンディングする際に、高い超音波出力を用いる。その際、インナーリードの超音波振動方向への振動を規制し、高品質で且つ信頼性が高いボンディングを実現できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】インナーリード7aを有するリードフレーム4と、リードフレーム4に搭載された、電極パッド3aを有する半導体素子2と、電極パッド3aとインナーリード7aとを接続する導電性の接続体8とを有し、インナーリード7aにおける、接続体8が接合される接合領域11の近傍に、凹部12を配置された半導体装置を提供する。

(もっと読む)

半導体装置

【課題】ノイズの影響を抑制することができる半導体装置を提供する。

【解決手段】モールド樹脂50を樹脂50aに磁性材料50bを混入して構成する領域を有しるものとする。または、隣接するリード30の間に配置されるモールド樹脂50を、樹脂50aに誘電性材料50cを混入して構成する。これによれば、半導体装置のインダクタンスまたは容量を大きくすることができ、共振周波数を低くすることができる。したがって、増幅されるノイズの周波数を低くすることができ、当該ノイズが増幅されたとしても半導体チップ20に対する影響を抑制することができる。

(もっと読む)

テープキャリア付半導体実装用導電基材の表面処理方法、ならびにこの処理方法を用いてなるテープキャリア付半導体実装用導電基材および半導体パッケージ

【課題】信頼性及び封止材との接着性を向上できるテープキャリア付き半導体実装用導電基材の表面処理方法、この処理方法を用いてなるテープキャリア付き半導体実装用導電基材、およびこれらを用いた半導体パッケージを提供することを目的とする。

【解決手段】テープキャリア付き半導体実装用導電基材に腐食抑制剤を含有する第1の化学粗化液を接触させて半導体実装用導電基材の表面に粗化形状を形成する第1粗化工程を有する、テープキャリア付き半導体実装用導電基材の表面処理方法。第1粗化工程の後に、さらに腐食抑制剤を含有する第2の化学粗化液に接触させる第2粗化工程を有する、前記のテープキャリア付き半導体実装用導電基材の表面処理方法、この表面処理を用いてなるテープキャリア付き半導体実装用導電基材、およびこれらを用いた半導体パッケージ。

(もっと読む)

半導体装置

【課題】パワーMOSFETなどが封止された小型面実装パッケージの低オン抵抗化を実現する。

【解決手段】シリコンチップ3は、ドレインリードを構成するリード4と一体に形成されたダイパッド部4Dの上に搭載されており、その主面にはソースパッド7とゲートパッド8が形成されている。シリコンチップ3の裏面は、パワーMOSFETのドレインを構成しており、Agペーストを介してダイパッド部4Dの上面に接合されている。ソースリードを構成するリード4とソースパッド7は、Alリボン10によって電気的に接続されており、ゲートリードを構成するリード4とゲートパッド8は、Auワイヤ11によって電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のオン状態における素子全体にわたる抵抗成分のうち、半導体基板に起因する抵抗成分を低減することができ且つ半導体基板の裏面側からの放熱効果を向上できるようにする。

【解決手段】半導体装置は、半導体素子が形成された第1の主面と、該第1の主面の反対側の面である第2の主面とを有する半導体基板と、該半導体基板の第2の主面に固着されたリードフレーム114とを備えている。第2の主面を構成するコレクタ層8には、少なくとも1つの凹部8aが形成されている。リードフレーム114における第2の主面と固着される面には、コレクタ層8に形成された各凹部8aと嵌合する凸部114aが形成されている。

(もっと読む)

磁気メモリチップを有する半導体装置の製造方法

【課題】アセンブリ段階において外部磁場から磁気メモリチップを保護する。

【解決手段】主面に磁気メモリ素子および複数のワイヤボンドパッドが形成された磁気メモリチップを準備する。シリコンより高透磁率を有する第1の磁気シールド板を磁気メモリチップの主面に搭載する。磁気メモリチップをリードフレームのダイパッド上に搭載しダイアタッチフィルムにより接着する。磁気メモリチップのワイヤボンドパッドとリードフレームのリードとをワイヤで電気的に接続する。磁気メモリチップ、磁気シールド板、ワイヤ及びリードの一部を樹脂により封止する。複数の磁気メモリチップを有するシリコンウェハを準備し、シリコンウェハの裏面を研削することによりシリコンウェハを所定の厚さまで薄くしてダイアタッチフィルムを張り付けた後にシリコンウェハをダイシングして各々がダイアタッチフィルムをその裏面に有する複数の磁気メモリチップを形成する。

(もっと読む)

1 - 20 / 256

[ Back to top ]