Fターム[5F083AD31]の内容

Fターム[5F083AD31]に分類される特許

101 - 109 / 109

半導体装置およびその製造方法

【課題】DRAM混載半導体装置において、寄生容量の増大等の不具合を伴うことなくDRAM領域とロジック領域の間における層間絶縁膜の段差の発生を抑制することと共に、プレートコンタクトの深さをより正確に調整する。

【解決手段】本発明の半導体装置の製造方法では、第2の層間絶縁膜15内に溝42を形成した後、溝42の底面および側面を覆うストレージ電極16を形成する。ストレージ電極16の上に容量絶縁膜17を形成し、容量絶縁膜17の上に、400度以下の低温のCVD法とアンモニアを用いたアニールとを繰り返すことにより、TiOxNy膜19を形成する。TiOxNy膜19の上に、TiN膜20を形成し、TiOxNy膜19をマスクとしてTiN膜20のエッチングを行う。その後、露出するTiOxNy膜19を除去することにより、TiOxNy膜19およびTiN膜20からなるプレート電極を形成する。

(もっと読む)

半導体装置の製造方法、湿式エッチングに対する耐性を有するエッチング阻止層の形成方法、及び半導体装置

【課題】多様なエッチング溶液に対して優れた耐性を有するエッチング阻止層を含む半導体装置の製造方法及びその半導体装置と、多様なエッチング溶液に対して優れた耐性を有することで、湿式エッチング工程の間、下部構造物を効果的に保護することができるエッチング阻止層の形成方法とを提供する。

【解決手段】第1構造物上に金属酸化物115を蒸着し、その蒸着された金属酸化物115をアニーリングし、第1構造物上にエッチング阻止層115を形成する。エッチング阻止層115上には第2構造物120を形成し、エッチング阻止層115を用いて第2構造物をエッチングする。金属酸化物はハウニウム及びアルミニウムのうち少なくとも一つを含むことが好ましい。

(もっと読む)

半導体記憶装置

【課題】ビット線交差方式を採用して隣接ビット線間の容量を低減する効果を維持しつつも、ダミーメモリセルを無くしてメモリセルアレイの面積の増大を回避し得る半導体記憶装置を得る。

【解決手段】第2配線層内には、交差配線18a,18bとシャント配線SL0〜SL2,SL7〜SL9とが形成されている。交差領域TR3,TR4は、第X3〜X6行に属している。シャント配線SL0〜SL2,SL7〜SL9は、交差領域TR3,TR4が属さない第X0〜X2,X7〜X9行にそれぞれ属している。第4配線層内には、シャント配線SL3〜SL6が形成されている。シャント配線SL3〜SL6は、交差領域TR3,TR4が属する第X3〜X6行にそれぞれ属している。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】キャパシタ容量およびデータ保持特性をさらに向上させることができる半導体記憶装置とその製造方法を提供する。

【解決手段】半導体基板と、半導体基板に形成されたトランジスタTrと、半導体基板に形成されたトレンチに形成され、トランジスタの一方のノードに接続する第1記憶ノード電極を有する第1メモリキャパシタCtと、トランジスタを被覆して形成された層間絶縁膜と、層間絶縁膜上に形成され、一方のノードに接続する第2記憶ノード電極を有する第2メモリキャパシタCsと、層間絶縁膜を貫通して形成され、第1記憶ノード電極と第2記憶ノード電極を接続する記憶ノードコンタクトプラグとを有し、第1メモリキャパシタ、第2メモリキャパシタおよびトランジスタを有するメモリセルが複数個配置されている構成とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】基板の上に設けられた強誘電体又は高誘電体を容量絶縁膜とする凹型の立体構造を有する容量素子においてそれぞれの高さが異なっている場合においても、それぞれの容量素子の容量を等しくすることにより、動作が安定な信頼性が高い半導体記憶装置を実現できるようにする。

【解決手段】第1の開口部27aの高さh1と第2の開口部27bの高さh2との差を考慮して、第1の容量素子23aの鍔部32aの表面積を、第2の容量素子23bの鍔部32bの表面積と比べて大きくすることにより、第1の下部電極20aの表面積と第2の下部電極20bの表面積とが等しくなるように補正する。これにより第1の容量素子23aと第2の容量素子23bとの容量を等しくすることができる。

(もっと読む)

半導体装置

【課題】 強誘電体膜の段差被覆性に優れた半導体装置を提供する。

【解決手段】 半導体装置は、基板上に形成された、表面に凹部又は凸部を有する電極9と、電極9の上に形成されたSr,Bi,Ta又は、Bi,La,Tiを含む強誘電体膜10とを備える。凹部又は凸部に存在する段差における強誘電体膜の段差被覆率が80%以上であり、強誘電体膜を構成する金属元素の組成比のばらつきが±15%以下である。チャンバー内に原料ガス祖構成する、各々が有機金属化合物を含む複数種類のソースガスを導入するとともに、複数種類のソースガスの主成分同士を反応律速で化学反応させることにより、電極の表面に強誘電体膜を堆積する。

(もっと読む)

半導体装置及びその製造方法

【課題】 下部電極の上端近傍で酸化タンタル膜が薄膜化するのを防ぎ、この部分での下部電極と上部電極の間のリークを防ぐことができる半導体装置及びその製造方法を得る。

【解決手段】 本発明に係る半導体装置は、凹部を有するシリコン酸化膜と、凹部内に形成された下部電極と、下部電極の上端近傍に設けられたシリコン窒化膜と、下部電極を覆うように形成された酸化タンタル膜と、酸化タンタル膜上に形成された上部電極とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 CMOSロジック部と、用途の異なる複数のDRAM部とを同一半導体基板上に混載したDRAM混載デバイスにおいて、十分な信号保持特性を確保しながら低消費電力及び高速性能を同時に満足できるようにする。

【解決手段】 動作速度が大きい第1のDRAM部102を構成するメモリセルの容量を、動作速度が小さい第2のDRAM部103を構成するメモリセルの容量よりも大きくする。

(もっと読む)

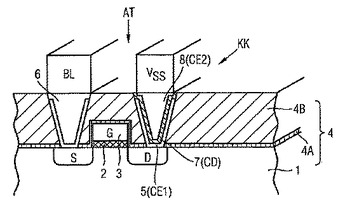

半導体メモリセルおよびその製造方法

本発明は、ストレージキャパシタが選択トランジスタ(AT)に接続されている半導体メモリセル、および、その製造方法に関するものである。本発明では、ストレージキャパシタは、ソース領域Sまたはドレイン領域Dのための少なくとも1つのコンタクトホールにおいて、コンタクトホールキャパシタ(KK)として形成されている。このような半導体メモリセルは、特にコスト効率よく製造することができ、かつ高集積度を達成できる。  (もっと読む)

(もっと読む)

101 - 109 / 109

[ Back to top ]