Fターム[5F083AD31]の内容

Fターム[5F083AD31]に分類される特許

21 - 40 / 109

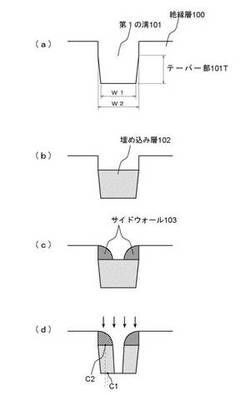

半導体装置及びその製造方法

【課題】本発明ではフォトリソグラフィー技術解像限界付近のパターン形成を安定して形成すると共に、コンタクトプラグなどの構造物における目合わせずれや接触面積の縮小による接触電気抵抗の増大や接続不良を解決する。

【解決手段】半導体基板上に形成された絶縁材料層100に、第1の方向に延在し、底部の幅W1より上部の幅W2が広い第1の溝101を形成する工程と、第1の溝101内に、溝の上端より低い位置まで埋め込み層102を形成する工程と、埋め込み層102上に露出している第1の溝101の側壁を覆うサイドウォール103を形成する工程と、サイドウォール103をマスクとして埋め込み層102をエッチングして第1の方向に分離する工程と、

を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ガードリングの広がりを防止し、セルマット端でのシリンダ倒れに起因するキャパシタ下部電極同士のショートあるいはキャパシタ下部電極の底面の下部導電体との接触面積減少による高抵抗化を抑制する。

【解決手段】キャパシタの下部電極となるシリンダ状電極を形成し、サポート膜をシリンダ状電極内に充填した後、シリンダ状電極の型材となるシリンダコア絶縁膜を選択的にウェットエッチングにて除去する工程を備え、エッチング液がキャパシタ形成領域外へ浸透するのを阻止するガードリングがキャパシタ形成領域外周に設けられ、このガードリング内にサポート膜がシームを有して充填されており、ウエットエッチング時にシームとエッチング液との接触を防止する膜を形成するか、シリンダコア絶縁膜を焼き締めておくことで、ガードリングの広がりを防止する。

(もっと読む)

キャパシタおよびその製造方法、半導体装置

【課題】比誘電率が高く、リーク耐圧に優れた容量絶縁膜を用いたキャパシタを提供する。

【解決手段】下部電極1と、下部電極1上の容量絶縁膜2と、容量絶縁膜2上の上部電極3とを備えるキャパシタにおいて、容量絶縁膜2として、TiO2膜にZr又はAlが(Zr又はAl)/((Zr又はAl)+Ti)で表される原子数比で40%以下の濃度で均等に分布して添加された膜を使用する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】絶縁膜の比誘電率を容易かつ十分に低下させる。

【解決手段】半導体装置の製造方法では、それぞれ環状SiO構造を主骨格とし互いに構造が異なる2種類以上の有機シロキサン化合物原料を混合した後で気化する。又は、それら2種類以上の有機シロキサン化合物原料の混合と気化とを一度に行うことによって、気化ガスを生成する。そして、その気化ガスをキャリアガスとともに反応炉に輸送する。そして、反応炉にてその気化ガスを用いたプラズマCVD法又はプラズマ重合法によって多孔質絶縁膜を成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接する埋め込みビット線が短絡(ショート)することを防止した半導体装置を提供する。

【解決手段】半導体基板2の面内に枠状に形成された第1の溝部3と、第1の溝部3に絶縁膜4を埋め込むことによって形成された素子分離領域5と、素子分離領域5の内側に形成された素子形成領域6と、素子形成領域6において第1の方向Yに延在し、且つ、格子状に複数並んで形成された第2の溝部7と、第2の溝部7の両側面に不純物を拡散させることによって形成された埋め込みビット線10とを備え、第2の溝部7の両端が素子分離領域5に至るまで第1の方向Yに延在して設けられている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】所望の等価酸化膜厚(EOT)及びリーク電流特性を有するキャパシタを備えた半導体記憶装置を提供する。

【解決手段】第1の電極と容量絶縁膜と第2の電極からなるキャパシタを備えた半導体記憶装置において、この容量絶縁膜は、金属酸化物結晶化膜からなる第1の誘電体膜と、第1の誘電体膜上の窒素含有アモルファス金属酸化物からなる第2の誘電体膜と、第2の誘電体膜上の金属酸化物結晶化膜からなる第3の誘電体膜を含む。

(もっと読む)

半導体素子及びその形成方法

【課題】格納電極コンタクトおよび格納電極の形成方法を提供する。

【解決手段】半導体素子は、活性領域104上に備えられる多数の導電プラグ116と、前記多数の導電プラグ116のうち、前記活性領域104の中央部に位置する導電プラグ116に接続され、前記活性領域104の上部を通るビットライン123と、前記多数の導電プラグ116のうち、前記活性領域104の両端部に位置する導電プラグ116と接続する格納電極130とを含み、ビットライン123が活性領域104の上部に形成されることにより、活性領域104とビットライン123を電気的に連結させるビットラインコンタクトを別に形成せずとも良く、格納電極130はランディングプラグと直接接続するので、格納電極コンタクトを別に形成せずとも良い。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

キャパシタ用容量絶縁膜の製造方法

【課題】キャパシタ用容量絶縁膜として、比較的低温で容易に、ルチル結晶構造のTiO2膜を形成する方法を提供する。

【解決手段】半導体基板1上に酸化シリコン膜2を形成し、スパッタ法を用い、基板温度を300℃、チャンバー内をAr雰囲気で圧力0.5Paに保持した状態でTiターゲットのスパッタリングを行ってTi膜3を成膜し、該Ti膜3を酸素ガスを供給する熱処理炉を用いたファーネスアニールによって、アニール酸化を行い、ルチル結晶構造を有するTiO2膜4とする。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】絶縁層として高い誘電率を有する材料が用いられ、容量の増加および微細化が可能でリーク電流を抑制できるキャパシタ素子を備えた半導体装置を提供する。

【解決手段】キャパシタ素子に蓄積される電荷の有無によってメモリ情報の記憶動作を行う半導体装置であって、キャパシタ素子が、高い誘電率を有する金属の酸化物を含む絶縁層と、絶縁層の第1面に接して設けられ、貴金属またはその化合物からなる貴金属材料で形成された第1電極aと、絶縁層の第2面に接して設けられ、貴金属を除く金属またはその化合物からなる第1電極aよりも仕事関数の小さい材料で形成された第2電極bとを有するものであり、第1電極aの電位が、第2電極bの電位以下とされている半導体装置とする。

(もっと読む)

システムオンチップアプリケーション用二重誘電体MIMコンデンサ

【課題】システムオンチップアプリケーション用の二重誘電体MIMコンデンサを提供する。

【解決手段】集積回路構造は、第1領域と第2領域とを有するチップを含む。第1金属‐絶縁体‐金属(MIM)コンデンサは、第1領域に形成される。第1MIMコンデンサは、第1下部電極と、第1下部電極の上の第1上部電極と、第1下部電極と第1上部電極との間に位置および隣接する第1キャパシタ絶縁体とを有する。第2MIMコンデンサは、第2領域に位置し、第1MIMコンデンサと実質的に同じレベルに位置する。第2MIMコンデンサは、第2下部電極と、第2下部電極の上の第2上部電極と、第2下部電極と第2上部電極との間に位置および隣接する第2キャパシタ絶縁体を有する。第2キャパシタ絶縁体は第1キャパシタ絶縁体と異なる。第1上部電極および第1下部電極は、それぞれ第2上部電極および第2下部電極と同時に形成されることができる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】導電性酸素バリア膜をドライエッチングする際に、上部電極と下部電極とがショートしてキャパシタリークによる特性劣化を防止する。

【解決手段】半導体基板101の上に酸素バリア膜201及び第2の層間膜202を順次形成し、第2の層間膜202に、酸素バリア膜201を露出するキャパシタ用開口部215を形成し、その底面上及び側壁上を含み、第2の層間膜202の上に第1の導電膜203、容量絶縁膜204及び第2の導電膜205を順次形成する。次に、キャパシタ用開口部215を埋め込むと共に、その上方においてキャパシタ用開口部215の径よりも大きい径を持つレジストマスク206を形成し、これを用いて、第2の導電膜205、容量絶縁膜204、第1の導電膜203及び第2の層間膜202をエッチングする。次に、キャパシタ用開口部215の周辺の上に残存する第2の導電膜205、容量絶縁膜204及び第1の導電膜203を除去する。

(もっと読む)

半導体装置

【課題】隣接するゲート電極間がショートすることを防止して、半導体装置の製造歩留まりを向上させる。

【解決手段】メモリセル領域に溝型ゲート電極構造のMOS型トランジスタ、周辺回路領域にはプレーナー型ゲート電極構造又は溝型ゲート電極構造のMOS型トランジスタが形成されるDRAMにおいて、ダミートランジスタ及び電界効果型トランジスタを第2の方向21に配列して、ダミートランジスタは第2の方向21に関して少なくとも一方の端に配置し、ダミートランジスタのゲート電極の埋設部36が電界効果トランジスタのゲート電極の埋設部36よりも第2方向21の幅が短い。

(もっと読む)

半導体記憶装置

【課題】COB構造を備えた半導体記憶装置において、容量絶縁膜の水素による劣化を防止するとともに、ビット線のエッチングでの薄膜化を防止する。

【解決手段】半導体記憶装置は、MOSトランジスタ320と、メモリ領域310の上方に設けられ、不純物拡散層203bに電気的に接続されたビット線207と、強誘電体または高誘電体を含む容量絶縁膜213とを有し、ビット線207よりも高い位置に設けられたキャパシタ215と、キャパシタ215の下方を覆う下部水素バリア膜210と、キャパシタ215の側方及び上方を覆う上部水素バリア膜218と、周辺回路領域300の上方に形成された配線221と、ビット線207よりも低い位置に形成され、上方から見た場合にメモリ領域310から周辺回路領域300へと延伸し、ビット線207と配線221とを電気的に接続させる導電層203aとを備える。

(もっと読む)

半導体装置の製造方法

【課題】固定電荷等の影響がなく電気的特性の優れた良質なSOD単層膜を備えた、微細LSIプロセス用の素子分離領域を備えた半導体装置を提供する。

【解決手段】半導体基板内のトレンチの内壁上に酸化膜およびライナー膜を形成する膜形成工程と、トレンチ内にSOD膜を埋設して熱処理を行う工程と、SOD膜と接するライナー膜の一部を除去してSOD膜の一部を露出させる除去工程と、SOD膜に対して熱処理を行う熱処理工程と、トレンチ内に絶縁膜を埋設させることにより素子分離領域を形成する埋設工程と、を有する半導体装置の製造方法。

(もっと読む)

キャパシタ用絶縁膜及びその形成方法、並びにキャパシタ及び半導体装置

【課題】大きな誘電率とリーク電流の抑制の両立が可能なキャパシタ用絶縁膜を提供する。

【解決手段】電極1、2の間に絶縁膜3が挟まれた構造からなるキャパシタ素子において、キャパシタ用絶縁膜3は酸化アルミニウム膜と二酸化チタン膜が交互に積層された積層構造を有し、前記二酸化チタン膜は、ルチル結晶構造を有し、前記酸化アルミニウム膜は、そのトータルの膜厚の比率が、前記積層構造の総膜厚に対して3〜8%である、キャパシタ用絶縁膜。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高アスペクト比の孔または溝を穿孔する。

【解決手段】酸化シリコンからなる絶縁膜1に対して、C5F8、O2およびArのエッチングガスを用いプラズマエッチング処理を施し、絶縁膜1を選択的にエッチングすることにより、絶縁膜1に孔3を穿孔する際に、最初は、ポリマー層のデポジション性が弱い条件でエッチング処理を行い、続いてポリマー層のデポジション性が強い条件に切り換えてエッチング処理を行うようにした。

(もっと読む)

半導体装置およびその製造方法

【課題】一定のキャパシタ容量を確保しつつ、高集積化が可能で、高い信頼性を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法であって、以下の工程を含む。半導体基板1を準備する。シリコン窒化膜58を形成する。シリコン窒化膜58の上面に接する第1の絶縁膜86を形成する。第1の絶縁膜の上面に接する第2の絶縁膜85を形成する。シリコン窒化膜58、第1の絶縁膜86及び第2の絶縁膜85を貫通して導電体を露出する開口部を形成する。第1の絶縁膜のエッチングレートが第2の絶縁膜及びシリコン窒化膜より高くなるエッチング条件で開口部61a内にエッチング処理を施す。キャパシタの下部電極170aを、第2の絶縁膜の上面に接することなく開口部の内部表面に沿って形成する。キャパシタの上部電極151を形成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンケイブ型の立体型スタック構造を採る容量素子において、下部電極における開口部の底面の隅部に生じるマイクロボイド(ボイド)の発生を抑止して、下部電極の断線を防止できるようにする。

【解決手段】半導体記憶装置は、半導体基板50の上に選択的に形成された導電性密着層11と、半導体基板50の上に導電性密着層11を覆うように形成され、該導電性密着層11の中央部分を露出するホール開口部20aを有する第2の層間絶縁膜20と、ホール開口部20aの底面及び壁面に沿って形成された下部電極25、該下部電極25の上に順次形成された容量絶縁膜30及び上部電極35からなる容量素子とを有している。導電性密着層11は、第2の層間絶縁膜20におけるホール開口部20aの底面と壁面とが接する隅部を含む該底面でのみ下部電極25と接している。

(もっと読む)

半導体装置及び半導体装置の製造方法並びにデータ処理システム

【課題】動作特性の制御が容易で微細化に有利なトランジスタを有する半導体装置およびその製造方法並びにデータ処理システムを提供する。

【解決手段】活性領域K内に設けられたトレンチ100と、トレンチ100と第1素子分離領域S1との間の活性領域Kに形成されたフィン型チャネル領域185と、第1素子分離領域S1に埋設され、第1ゲート絶縁膜141を介してフィン型チャネル185と接する第1ゲート電極151と、トレンチ100に埋設され、第2ゲート絶縁膜191を介してフィン型チャネル185と接する第2ゲート電極225と、フィン型チャネル185と接続され、活性領域K内において第2ゲート電極225を挟んでトレンチ100の両側に位置するソース/ドレイン拡散領域241とを具備してなるトレンチゲート型MOSトランジスタTrを有する半導体装置1を採用する。

(もっと読む)

21 - 40 / 109

[ Back to top ]