Fターム[5F083AD31]の内容

Fターム[5F083AD31]に分類される特許

81 - 100 / 109

半導体記憶装置

【課題】半導体記憶装置におけるMOSトランジスタのソース・ドレイン間のリーク電流を低減する。

【解決手段】DRAMをSOI基板上に形成する。DRAMのセンスアンプ20、プリチャージ回路23、ビット線選択回路26A,26B、メモリセル27、ダミーセル28およびコラム選択回路29におけるトランジスタQn1,Qn2,Qp1,Qp2,Qpc,Qe,Qb,Qd,Qm,Qioのボディ領域を電気的に固定した。

(もっと読む)

酸化物のエッチング、荒れの削減、およびコンデンサ構造の作製の方法

本発明は、少なくとも1X10-6の水性酸解離定数を持つ一種以上のカルボン酸成分が、酸化物(二酸化ケイ素もしくはドープした二酸化ケイ素など)のエッチングの間に利用される方法を含む。二種以上のカルボン酸も利用できる。カルボン酸の例としては、トリクロロ酢酸、マレイン酸、クエン酸を含む。 (もっと読む)

半導体集積回路装置の製造方法

【課題】MISFETの微細化を推進する。

【解決手段】窒化シリコン膜14とサイドウォールスペーサ16とをマスクにしたドライエッチングによって、素子分離領域の基板1に溝2aを形成した後、窒化シリコン膜14の側壁のサイドウォールスペーサ16を除去し、次いで、基板1を熱酸化することによって、活性領域の周辺部の基板1の表面をラウンド加工し、凸状の丸みが付いた断面形状とする。これにより、活性領域の寸法を減少させることなく、その周辺部をラウンド加工することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 記憶保持特性が良好なダイナミック型メモリセルを有する半導体装置およびその製造方法を提供する。

【解決手段】 第1導電型の半導体基板11と、電荷蓄積領域を有するトレンチキャパシタ12と、半導体基板11上にゲート絶縁膜13を介して設けられたゲート電極15と、第2導電型のドレイン領域16およびソース領域17と、トレンチキャパシタ12に隣接して電荷蓄積領域の上面を覆うように半導体基板11に設けられた素子分離領域18と、電荷蓄積領域の上部をソース領域17と電気的に接続するように設けられた第2導電型の埋め込みストラップ領域19と、ドレイン領域16およびゲート電極15の一部の下にあって、素子分離領域18の最深底部aより上方の半導体基板11中に設けられ、半導体基板11より高いキャリア濃度を有する第1導電型のウェル領域20と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】 コンタクトホールがボーイング形状となるのを防止し、かつコンタクトホールの下部の開口径を大きくすることができる半導体装置の製造方法を得る。

【解決手段】 絶縁膜を所定深さまでドライエッチングしてコンタクトホールを形成する工程と、コンタクトホールの側壁に側壁保護膜を形成する工程と、側壁保護膜をマスクとしてコンタクトホールの底部から絶縁膜をドライエッチングしてコンタクトホールを更に掘り込む工程と、側壁保護膜をマスクとしてコンタクトホールの下部の側面にある絶縁膜をウェットエッチングすることにより、コンタクトホールの下部と上部の境界において、下部の開口径を上部の開口径以上にする工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 キャパシタ形成後のコンタクトプラグ形成時又は配線層形成時等に容量絶縁膜に加わるプラズマダメージを低減することにより、容量絶縁膜の劣化を抑制してキャパシタリーク電流の増大を防止する。

【解決手段】 半導体基板100上の第1の層間絶縁膜106の上に形成され第2の層間絶縁膜109に、キャパシタ領域となる凹部110が形成されている。凹部110内に下部電極(第2のポリシリコン膜412及びHSG膜413)が形成されていると共に該下部電極上に容量絶縁膜となる酸化タンタル膜115及び上部電極となる第1の窒化チタン膜が形成されている。当該上部電極及び上層配線124のそれぞれと接続するプレートコンタクト120が、第1の層間絶縁膜106中に形成されたプラグ107Cを介して、半導体基板100の表面部のN型不純物拡散層105と電気的に接続されている。

(もっと読む)

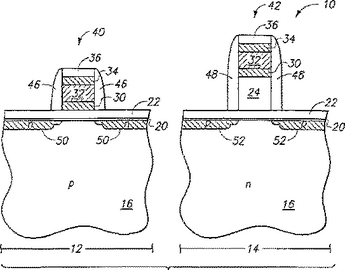

半導体記憶装置及びその製造方法

【課題】 工程の追加なしに又は少ない工程を追加するだけで、信頼性の高いメモリセルを有する半導体記憶装置を形成する。

【解決手段】 ワード線となるゲート電極20と、下部電極12A、容量絶縁膜13及び上部電極14からなるキャパシタとによってメモリセルが構成されている。ダミーワード線となるダミーゲート電極21と、ダミー下部電極12B、容量絶縁膜13及び上部電極14からなるキャパシタとによってダミーセルが構成されている。ダミー下部電極12Bの短辺寸法が下部電極12Aの短辺寸法よりも小さく設定されている。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMキャパシタにおいて、上部電極内に発生する応力を低減することにより、容量絶縁膜の劣化を抑制する。

【解決手段】本発明の半導体装置は、第1の層間絶縁膜11内に設けられた複数の溝部12の表面を覆う下部電極13と、下部電極13の上を覆う容量絶縁膜14と、容量絶縁膜14を挟んで複数の下部電極の上方を覆う上部電極15とを備えている。上部電極15には、クラック17a、溝17bまたは凹部17cといった応力緩衝部17が設けられている。

(もっと読む)

半導体メモリ装置の製造方法

【課題】エッチング停止絶縁膜のエッチング時に生じるキャパシタの漏れ電流ソースの発生を防止できる半導体メモリ装置の製造方法を提供すること。

【解決手段】半導体基板(31)上に層間絶縁膜(32)を形成するステップと、コンタクトホール(33)の側壁にストレージノードコンタクトスペーサ(34)を形成するステップと、コンタクトホール(33)の内部にストレージノードコンタクトプラグ(35)を形成するステップと、層間絶縁膜(32)をリセスするステップと、全面にエッチング停止絶縁膜(36)及びストレージノード用絶縁膜(37)を積層するステップと、絶縁膜(37)及びエッチング停止絶縁膜(36)をドライエッチングし、コンタクトプラグ(35)及びコンタクトスペーサ(34)を開放させる開放部(38)を形成するステップと、下部電極(40)、誘電膜(41)及び上部電極(42)を形成するステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 MIM構造の容量素子の形成にあたり、表面が凹凸を有する下部電極の形成に際して高温の熱処理を必要としない半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、下部電極20を形成する工程が、容量素子収容孔18の表面に400℃の基板温度でスパッタ法によってCoを堆積し、表面に凹凸を有するCo膜19を形成する工程と、Co膜19を覆って窒化チタンから成る下部電極20を形成する工程とを有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】絶縁膜に形成した溝の内部に導電層を形成する方法を提供する。

【解決手段】酸化シリコン膜24に形成した溝25の内部にアモルファスシリコン膜26Aを堆積し、続いてアモルファスシリコン膜26Aの上部にフォトレジスト膜30をスピン塗布する。次に、フォトレジスト膜30の全面に露光光を照射して溝25の外部のフォトレジスト膜30を露光する。このとき、溝25の内部のフォトレジスト膜30は、露光量が不足するので露光されない。次に、フォトレジスト膜30を現像して露光部である溝25の外部のフォトレジスト膜30を除去した後、溝25の内部に残った未露光のフォトレジスト膜30をマスクにしたドライエッチングで溝25の外部のアモルファスシリコン膜26Aを除去する。

(もっと読む)

半導体記憶装置とその製造方法

【課題】DRAMのメモリセルを構成するトランジスタとして良好な特性を持ち、且つ微細化にも好適な構成の半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体基板11と、この半導体基板11上に形成された素子分離領域28と、この素子分離領域28の間の前記半導体基板上に形成され凸部を有する素子形成領域30と、この素子形成領域30の凸部に形成されたチャネル部を有するトランジスタTraと、このトランジスタTraに接続されて前記半導体基板内または半導体基板上に形成されたキャパシタCt、Csとを具備し、前記素子形成領域30の凸部は前記トランジスタTraのチャネル幅方向に沿って互いに対面する第1、第2斜面とこの第1、第2斜面間に形成された上面とを有し、この上面のチャネル幅方向の幅が60nm以下で、かつ前記第1、第2斜面の延長で作られる頂角が鋭角であることを特徴とする半導体記憶装置。

(もっと読む)

誘電体膜の形成方法、及びこれを用いる半導体素子のキャパシタの形成方法

誘電特性及び漏れ電流特性を向上させることのできる半導体素子の誘電体膜の形成方法が提供される。本発明の実施形態によれば、誘電体膜の形成方法は、ウェーハ上に、連続的に形成されない厚さに酸化亜鉛(ZrO2)膜を形成するステップと、前記ZrO2膜が形成されていない前記ウェーハ上に、連続的に形成されない厚さに酸化アルミニウム(Al2O3)膜を形成するステップとを含む。 (もっと読む)

半導体装置及びその製造方法

【課題】 シリンダ型コンデンサにおいては、シリンダの垂直方向下側の対向する側壁間は狭く、HSGが接触し、シリンダが途中で閉塞される。閉塞された部分より下側領域においてはコンデンサが形成されず所望の容量値が得られないため半導体装置は動作不良となる。シリンダの閉塞を防止できるシリンダ型コンデンサの製造方法及びそれらを備えた半導体装置を提供する。

【解決手段】 シリンダ型コンデンサの下部電極となるアモルファスシリコンを高濃度不純物層と低濃度不純物層の2層構造とし、シリンダ下側領域の低濃度不純物層をエッチングし、下側領域に形成されるHSGの結晶粒径を小さくすることでシリンダの閉塞を防止する。

(もっと読む)

半導体素子の格納電極形成方法

【課題】ハードマスク層パターンを利用して格納電極領域の表面積を増加させ、格納電極用の酸化膜の損傷、及びコンタクト間のブリッジ現象を防止する。

【解決手段】本発明は半導体素子の格納電極形成方法に関し、特にハードマスク層パターンを利用して格納電極領域の表面積を増加させ、格納電極用は酸化膜の損傷、及びコンタクト間のブリッジ現象を防止することができる技術である。

(もっと読む)

半導体装置及びその製造方法

【課題】複雑な工程を追加することなく下部電極表面に凹凸を形成することにより、限られたセル面積の中で十分な容量を確保することができるMIM構造のキャパシタを提供する。

【解決手段】本発明の半導体装置の製造方法では、第2のホール15の表面に、キャパシタの下部電極となる窒化チタン膜16aを形成する。窒化チタン膜16aの形成は、化学気相成長法と、アンモニア雰囲気下でのアニールとを16回繰り返すことにより行う。この化学気相成長法を、低温、高圧力、原料ガスであるアンモニアに対する四塩化チタンの流量比を従来よりも高くした条件で行うことにより、窒化チタン膜16aの表面の凹凸を高くすることができる。一方、アンモニア雰囲気下でのアニールを行うことにより、窒化チタン膜16aが低抵抗化される。

(もっと読む)

半導体MOS装置及びCMOS装置、コンデンサ、及び製造方法

回路装置の作製方法を提供する。導電性にドープされたシリコンと誘電材との間に厚さ20Å以下(または70以下のALDサイクルで生じた厚さ)の金属含有材を形成する。導電性にドープされたシリコンとしてn型を用いることができ、誘電材は高k誘電材を用いることができる。金属含有材は誘電層上へ直接形成でき、導電性にドープされたシリコンは金属含有材上へ直接形成できる。回路装置はコンデンサ構造体あるいはトランジスタ構造体とすることができる。回路装置がトランジスタ構造体である場合はCMOS装置中へ組み入れることができる。本発明による種々装置はメモリ構造体中へ組み入れられる他、電子システムへも組み入れることができる。  (もっと読む)

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化を実現しつつリーク電流を抑制することができ、かつ、多くの容量を保持することができるDRAM混載半導体装置を提供する。

【解決手段】本発明の半導体記憶装置のキャパシタは、ストレージノードホール9の底面を覆い、側面を第2の層間絶縁膜8の上面の高さよりも低い高さまで覆う下部電極10と、下部電極の上を覆う容量絶縁膜11と、容量絶縁膜11の上を覆う上部電極12とを備える。この構造では、ビット線コンタクト14を形成するための開口17がずれてキャパシタにまで達しても、容量が蓄積される部分の容量絶縁膜が露出することがない。そのため、リーク電流の発生を抑制することができる。また、ストレージノードホール9と開口17との間にマージンを設ける必要がないので、微細化を実現することができると共に、メモリセルサイズが一定のままで保持できる容量を多くすることができる。

(もっと読む)

半導体装置の製造方法

【課題】 プラズマドーピングと活性化アニールを同時に実施する場合にも、不純物の外方拡散によるシリコン基板表面、またはポリシリコン電極表面の濃度低下を防止する。

【解決手段】 被処理基板であるシリコン基板、または被処理基板に形成されているポリシリコン膜の表面に窒化膜14を形成する工程と、前記被処理基板を700℃以上に加熱して燐元素を含むガスによりプラズマ放電して前記窒化膜を突き抜けて前記シリコン基板、または前記ポリシリコン膜に燐ドーピング処理を行う工程を実行する。

(もっと読む)

半導体装置及びその製造方法

【課題】 深孔の壁面におけるボーイングが抑制されたスタック型キャパシタを備える半導体装置を提供する。

【解決手段】 半導体装置100は、シリコン基板101の主面上部に形成された第三の層間絶縁膜123と、第三の層間絶縁膜123内に形成され上部に開口を有する筒状の下部電極125と、下部電極125の表面を覆って形成された筒状の誘電体膜126と、誘電体膜126上に形成され誘電体膜126を介して下部電極125と対向する上部電極127とを備えるキャパシタと、下部電極125の底部に金属シリサイド124を介して接続されるコンタクトプラグ122とを備える。下部電極125は、開口に隣接する上部電極部分が2層の多結晶シリコン膜153,154で構成され、金属シリサイド124に隣接する底部電極部分が2層の多結晶シリコン膜153,154の内で最上層の多結晶シリコン膜154で構成される。

(もっと読む)

81 - 100 / 109

[ Back to top ]