Fターム[5F083EP54]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | CG・FG間絶縁膜 (2,372) | 構造(多層構造) (1,331) | 2層 (115)

Fターム[5F083EP54]に分類される特許

1 - 20 / 115

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、半導体層として機能する酸化物半導体膜と、酸化物半導体膜上のシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有し、少なくともゲート電極と重畳する酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%以下の濃度で分布する領域を有する構造とする。

(もっと読む)

半導体装置、メモリカード、データ処理システムおよび半導体装置の製造方法

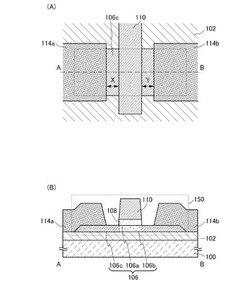

【課題】歩留まりや信頼性の低下を招くことなく、隣接セルのフローティング・ゲート間の結合容量を小さくすることができ、隣接セルの書き込み情報の影響を小さくした状態でフローティング・ゲートの電位を制御することが可能なNAND型フラッシュメモリを提供する。

【解決手段】一導電型の半導体材料層表面のチャネル領域上方に第2の絶縁膜12を介して形成されたゲート電極部と、ゲート電極部の上方に前記ゲート電極部と一体形成されたキャパシタ電極部と含むフローティング・ゲート13と、キャパシタ電極部の側面を囲むように第1の絶縁膜12を介して形成されたコントロールゲート10となる第1の電極と、を有する。

(もっと読む)

酸化膜の形成方法

【課題】シリコン表面のプラズマ酸化により、界面準位密度が低くリーク電流の少ない高品質な酸化膜をシリコン表面上に形成する。

【解決手段】

酸化膜の形成方法は、KrとO2の混合ガス中にプラズマを形成することにより原子状酸素O*を発生させ、前記原子状酸素O*によりシリコン表面をプラズマ酸化するプラズマ酸化工程を含み、前記プラズマ酸化工程は、800〜1200mTorrの圧力範囲において実行される。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体素子の製造方法

【課題】400℃以上の温度で原子層蒸着法により蒸着が可能な前駆体を用いて高密度を有する非晶質の高誘電絶縁膜形成を通じてキャパシタンス等価厚及び漏洩電流特性を向上させることができる半導体素子の製造方法を提供する。

【解決手段】半導体基板100上にZr[C5H4(CH3)]2(CH3)2、Zr[C5H4(CH3)]2(OCH3)CH3及びZr[C5H4(CH2CH3)][N(CH3)(CH2CH3)]3の何れか一つの前駆体を用いて400℃〜500℃の温度で形成されたジルコニウム酸化膜(ZrO2)140を含む高誘電絶縁膜を形成することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または

、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶

縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と

、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁

層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)

粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層

表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路。特に、短時間の電源停止により消費電力を抑えることができる信号処理回路。

【解決手段】制御装置と、演算装置と、緩衝記憶装置とを有し、緩衝記憶装置は、主記憶装置から、或いは演算装置から送られてきたデータを、制御装置からの命令に従って記憶し、緩衝記憶装置は複数のメモリセルを有し、メモリセルは、チャネル形成領域に酸化物半導体を含むトランジスタと、トランジスタを介してデータの値に従った量の電荷が供給される記憶素子とを有する信号処理回路。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極は、高い不純物濃度領域と低い不純物濃度領域とからなり、高い不純物濃度領域は、コントロールゲート絶縁膜と接する部分に配置し、低い不純物濃度領域はトンネル絶縁膜と接する領域に配置し、フローティングゲート電極のコントロールゲート絶縁膜と接する表面部分には微細凹凸を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域のエッジ近傍のトンネル絶縁膜上には、トンネル絶縁膜とは異なる材質の絶縁膜からなる電界緩和層を配置した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域とフローティングゲート電極との間には、膜厚の異なる複数のトンネル絶縁膜を形成した。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

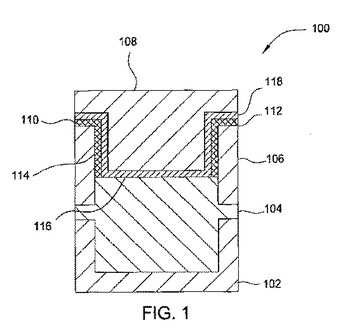

半導体記憶装置およびその製造方法

【課題】書き込み特性の向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板10上に、トンネル絶縁膜11を形成し、前記トンネル絶縁膜上に、導電体で構成される電荷蓄積層12を形成し、前記電荷蓄積層、前記トンネル絶縁膜、および前記基板を加工して、前記基板内に、前記電荷蓄積層および前記トンネル絶縁膜を分離する素子分離溝22を形成し、前記素子分離溝内に、上面が前記電荷蓄積層の下面より高く上面より低くなるように素子分離絶縁膜13を埋め込み、前記電荷蓄積層の表面に形成された自然酸化膜30を除去し、前記素子分離絶縁膜および前記電荷蓄積層の表面に、絶縁膜14を形成し、前記自然酸化膜の除去から前記絶縁膜の形成までが、その内部の酸素濃度がコントロールされた製造装置内で行われる。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、電荷蓄積層内に蓄積された電荷の第2のゲート絶縁膜を介した制御ゲート電極へのリークを低減することを目的とする。

【解決手段】1つの実施形態によれば、半導体基板内で素子分離部により画定された素子領域と、素子領域を覆う第1のゲート絶縁膜と、第1のゲート絶縁膜を覆う電荷蓄積層と、半導体基板の素子領域が確定された面側を上とした場合において、電荷蓄積層の上面を覆う第1の部分と電荷蓄積層の側面を覆う第2の部分とを有する第2のゲート絶縁膜と、第2のゲート絶縁膜を介して電荷蓄積層の上面及び側面を覆う制御ゲート電極とを備え、第1の部分の耐圧は、前記第2の部分の耐圧より高い半導体記憶装置が提供される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】隣接セルとの容量を抑制することが可能な半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態の半導体記憶装置は、第1の方向および前記第1の方向と直交する第2の方向に配置される複数のメモリセルトランジスタを備える。前記メモリセルトランジスタのそれぞれは、半導体基板上に形成される第1の絶縁膜と、前記第1の絶縁膜上に形成される浮遊ゲート電極と、前記浮遊ゲート電極上に形成される第2の絶縁膜と、前記第2の絶縁膜上に形成される制御ゲート電極と、を有する。前記第1および第2の方向に隣接する2つの前記メモリセルトランジスタの前記浮遊ゲート電極は、前記隣接する方向の側面に括れた領域を有する。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

半導体装置

【課題】キャパシタを形成する領域の占有面積を縮小する。

【解決手段】本実施形態の半導体装置は、半導体基板10内に設けられた半導体領域AACと、半導体領域AAC内に設けられる複数のキャパシタCm,Cnを含むキャパシタ群と、を具備し、キャパシタCm,Cnのそれぞれは、半導体領域AAC上のキャパシタ絶縁膜42Aと、キャパシタ絶縁膜42A上のキャパシタ電極34Am,34Amと、キャパシタ電極34Am,34Amに隣接する拡散層32Aとを有し、を有し、キャパシタ電極34Am,34Anに接続される配線29m,29nのそれぞれは、キャパシタCm,Cn毎に電気的に分離され、キャパシタ電極Cm,Cnのそれぞれに異なる電位Vm,Vnが印加されている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

単一ステップによる選択的窒化の方法および装置

半導体基板を選択的に1ステップで窒化するための方法および装置が提供される。窒素は、選択的窒化プロセスを利用することにより、シリコン領域および酸化ケイ素領域を有する半導体基板のシリコン領域中に選択的に組み込まれる。窒素含有プラズマを形成し、このプラズマからイオンをフィルタリングまたは除去することにより、基板に窒素含有ラジカルが向けられてもよく、または、選択前駆体を使用する熱窒化プロセスを実施してもよい。遠隔プラズマジェネレータが、1つまたは複数のイオンフィルタ、シャワーヘッド、およびラジカル分配器を任意に備える処理チャンバに結合されてもよく、または、in situプラズマが生成され、1つまたは複数のイオンフィルタもしくはイオンシールドが、チャンバ内においてプラズマ発生ゾーンと基板支持体との間に配設されてもよい。  (もっと読む)

(もっと読む)

1 - 20 / 115

[ Back to top ]