Fターム[5F083GA17]の内容

Fターム[5F083GA17]に分類される特許

1 - 20 / 41

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

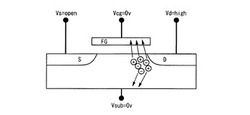

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置法を提供する。

【解決手段】制御回路は、消去動作時、選択セルユニットに接続された第1配線の電圧を、選択セルユニットに含まれる第1トランジスタのゲートの電圧よりも第1電圧だけ大きくする。制御回路は、消去動作時、非選択セルユニットに接続された第1配線の電圧と、非選択セルユニットに含まれる第1トランジスタのゲートの電圧との間の電圧差を第1電圧と異なる第2電圧とする。また、制御回路は、消去動作時、選択セルユニット及び非選択セルユニットにおいて、ダミーメモリストリング中の少なくとも1つのダミーメモリトランジスタのゲートに第3電圧を印加し、ダミーメモリストリング中の別のダミーメモリトランジスタのゲートに第3電圧よりも低い第4電圧を印加する。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】過消去ビットの発生を抑制してエンデュランス特性等を向上させることができる不揮発性記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え及び消去可能な複数の不揮発性メモリーセルM11〜M44を有するメモリーセルアレイと、複数の不揮発性メモリーセルのうちの消去対象メモリーセルに対する消去動作の制御を行う消去制御回路ERCNとを含む。消去制御回路ERCNは、消去対象メモリーセルが多い場合には、消去対象メモリーセルに対応するビット線BL1〜BL4がフローティング状態に設定される第1の消去動作制御を行う。消去対象メモリーセルが少ない場合には、消去対象メモリーセルに対応するビット線BL1〜BL4が低電位電源電圧VSSに設定される第2の消去動作制御を行う。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高速なアクセスが可能で、かつ、高集積化が可能なスプリットゲート型不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板101の主表面の溝に第1、第2のスプリット型不揮発性メモリセルを形成した不揮発性半導体記憶装置100であって、溝内部の対向する第1、第2の側壁102a,102bの表面にそれぞれ第1、第2のスプリット型不揮発性メモリセルの選択ゲート121とコントロールゲート122とが形成され、第1、第2のスプリット型不揮発性メモリセルの選択ゲート121とコントロールゲート122とには、それぞれ異なる電圧を印加することが可能である。

(もっと読む)

不揮発性半導体メモリデバイス

【課題】ダイナミック放電読み出しでセンスタイミングのずれを是正する。

【解決手段】センスアンプ7Bは、メモリセル抵抗Rcellの一方の電極が接続されたビット線BLの放電電位を参照電位Vrと比較して情報を読み出す。セット容量スイッチ18S、リセット容量スイッチ18Rおよび追加容量Coffsetとその制御手段によって、センスノード(電位Vo)の負荷容量、または、センスノードと参照電位Vrを入力する参照ノードの負荷容量との両方を、メモリセル抵抗Rcellの読み出す情報の論理(通常読み出し、書き込みまたは消去のヴェリファイ読み出しの相違)に応じて変化させる。

(もっと読む)

半導体記憶装置及び半導体記憶装置の製造方法

【課題】フローティングゲートとコントロールゲートとのオーバーラップ量のバラツキを抑制する。

【解決手段】基板(1)と、ゲート絶縁膜(2)を介してその基板(1)の上に設けたれたフローティングゲート(20)と、トンネル絶縁膜(30)を介してそのフローティングゲート(20)の隣に設けられたコントロールゲート(50)と、そのフローティングゲート(20)の上に設けられたスペーサー絶縁膜(9)と、そのスペーサー絶縁膜(9)とそのコントロールゲート(50)との間に設けられた保護膜(7)とを具備する半導体記憶装置(MC)を構成する。そのような半導体記憶装置(MC)において、その保護膜(7)は、スペーサー絶縁膜(9)以外の部分をエッチングするときに、スペーサー絶縁膜(9)の側面のストッパーとして機能している。

(もっと読む)

半導体装置およびその製造方法

【課題】コントロールゲート電極とメモリゲート電極間に発生する電界強度を緩和してリーク電流を低減できる、コントロールゲート電極とメモリゲート電極が近接するスプリットゲート型不揮発性メモリを提供する。

【解決手段】半導体基板1S上にゲート絶縁膜GOXが形成され、このゲート絶縁膜GOX上にコントロールゲート電極CGが形成されている。そして、コントロールゲート電極CGの右側の側壁には、積層絶縁膜を介してメモリゲート電極MGが形成されている。このとき、コントロールゲート電極CGの上端部にバーズビークBVが形成されている。この結果、コントロールゲート電極CGの上端部と、メモリゲート電極MGの上端部が、バーズビークBV分だけ離れるので電界強度の緩和を図ることができ、コントロールゲート電極CGとメモリゲート電極MG間を流れるリーク電流を低減できる。

(もっと読む)

ページ消去を有する不揮発性半導体メモリ

【課題】完全なフルブロックよりも小さい1つもしくはそれ以上のページを消去することができる不揮発性メモリを提供する。

【解決手段】選択電圧は、パストランジスタを介して複数の選択されたワードラインの各々に印加され、非選択電圧は、パストランジスタを介して選択されたブロックの複数の非選択ワードラインの各々に印加される。基板電圧は、選択されたブロックの基板に印加される。共通選択電圧は、各選択されたワードラインに印加され、共通非選択電圧は、各非選択されたワードラインに印加される。選択および非選択電圧は、選択されたブロックのいずれかのワードラインに印加することができる。ページ消去ベリファイ動作は、複数の消去されたページと複数の消去されていないページをもつブロックに適用される。

(もっと読む)

不揮発性半導体記憶装置及びその作製方法

【課題】書き込みや消去を繰り返し行った場合であっても、読み出し不良を抑制することを目的の一とする。又は、メモリトランジスタの面積の増大を抑制しつつ、書き込み電圧、消去電圧を低減することを目的の一とする。

【解決手段】基板上に設けられた書き込み動作及び消去動作に用いる第1の半導体層及び読み出し動作に用いる第2の半導体層上に、絶縁膜を介してフローティングゲートとコントロールゲートを設け、第1の半導体層を用いてフローティングゲートへの電子の注入・放出を行い、第2の半導体層を用いて読み出しを行う。

(もっと読む)

半導体記憶装置

【課題】プログラム動作やリード動作を高速化でき,セルトランジスタが過消去状態になってもリード動作を正常に行う半導体記憶装置を提供する。

【解決手段】選択トランジスタとそれに接続されコントロールゲートを有する記憶トランジスタとを有する複数のメモリセルと,複数のメモリセルの選択トランジスタのゲートに接続される複数の選択ゲート線と,複数のメモリセルの記憶トランジスタのコントロールゲートに接続される複数のコントロールゲート線と,複数のメモリセルの記憶トランジスタのソースに接続される複数のソース線と,選択ゲート線に交差し複数のメモリセルの選択トランジスタに接続される複数のビット線とを有し,プログラム動作では記憶トランジスタにソース線からドレイン電流を流し,リード動作では記憶トランジスタにソース線にドレイン電流を流す。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】消去ゲートとフローティングゲートとのカップリング容量を低下し、高速な消去動作を可能にするスプリットゲート型の不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板10のチャネル領域上に第1絶縁層12を介して設けられたフローティングゲート20と、フローティングゲート20上に第2絶縁層13、14を介して設けられた消去ゲート40と、フローティングゲート20及び消去ゲート40の側方に第3絶縁層を介して設けられたコントロールゲートとを具備する。フローティングゲート20はU字型であるため、フローティングゲート20を極めて小さい面積の端部で薄い第2絶縁層14を介して消去ゲート40と対向させることが出来る。そのため、フローティングゲート20と消去ゲート40との間のカップリング容量を小さくすることができ、消去動作での消去電圧を小さく抑えることが可能となる。

(もっと読む)

半導体記憶装置及びその製造方法と駆動方法

【課題】寄生抵抗の増大なく、ホットキャリアによる特性劣化を抑制できる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】ガラス基板1上に形成した半導体層3と、半導体層3上に形成したONO膜による電荷保持膜21と、電荷保持膜21上に設けたゲート電極22とを備える。更に半導体層3にゲーート電極22とオーバーラップするように設けられたニッケルシリサイド等の半導体と金属の化合物からなるソース・ドレイン領域23を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】消去ゲートと拡散層に接続されるプラグとの間のシリサイド・ショートの発生確率を低減させる。

【解決手段】不揮発性半導体記憶装置は、半導体基板上に形成されたフローティングゲートと、フローティングゲート上に形成された消去ゲートと、半導体基板表層のチャネル領域上にフローティングゲートと並設され、フローティングゲート及び消去ゲートの一方の側面に形成されたコントロールゲートと、フローティングゲート及び消去ゲートの他方の側面に対応する位置の半導体基板内に形成された第1拡散層と、第1拡散層に接続され、フローティングゲート及び消去ゲートの側方に位置するように第1拡散層上に形成されたプラグと、消去ゲートの上面に形成された第1シリサイド膜と、プラグの上面に形成された第2シリサイド膜と、を備え、プラグの上面の高さは、消去ゲートの上面の高さと同じ若しくはそれよりも下方に位置することを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】微細化が可能な消去ゲートを備える不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板1上に形成されたフローティングゲート3と、フローティングゲート3上に形成された消去ゲート10と、半導体基板1表層のチャネル領域上にフローティングゲート3と並設され、フローティングゲート3及び消去ゲート10の一方の側面に形成されたコントロールゲート22と、フローティングゲート3及び消去ゲート10の他方の側面に対応する位置の半導体基板1内に形成された第1拡散層15と、第1拡散層15に接続され、フローティングゲート3及び消去ゲート10の側方に位置するように第1拡散層15上に形成されたプラグ17と、コントロールゲート22に隣接する位置の半導体基板1内に形成された第2拡散層23と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】消去ゲートとコントロールゲートとの間のシリサイド・ショートの発生確率を低減させる消去ゲートを備えた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板1上に形成されたフローティングゲート3と、フローティングゲート3上に形成された消去ゲート10と、半導体基板表層のチャネル領域上にフローティングゲート3と並設され、フローティングゲート3及び消去ゲート10の一方の側面に形成されたコントロールゲート22と、消去ゲート10の上面に形成された第1シリサイド膜27と、コントロールゲート22の上面に形成された第2シリサイド膜26と、を備え、コントロールゲート22の上面の高さは、消去ゲート10の上面の高さと同じ若しくはそれよりも下方に位置することを特徴とする。

(もっと読む)

不揮発性メモリ装置のソフトプログラム方法

【課題】消去されたセルのしきい値電圧分布を改善させるためにソフトプログラム段階を行う不揮発性メモリ装置のソフトプログラム方法を提供する。

【解決手段】不揮発性メモリ装置のソフトプログラム方法は、消去動作が実施されたメモリセルのしきい値電圧を一定レベルに上昇させるソフトプログラム段階と、各セルストリング別にしきい値電圧以上にプログラムされたセルがあるかを判断する検証段階と、上記検証結果、全体のセルストリングがしきい値電圧以上にプログラムされたセルを一つ以上含むまで上記ソフトプログラムを反復する段階を含む。

(もっと読む)

不揮発性メモリトランジスタ

【課題】書き換え可能な不揮発性メモリトランジスタであって、書き換えの繰り返しによる閾値電圧特性の変化が抑制された信頼性の高い不揮発性メモリトランジスタを提供する。

【解決手段】第1導電型の半導体基板31の表層部に、第2導電型のソース領域32とドレイン領域33が形成され、トンネル酸化膜41を介して、半導体基板31上でドレイン領域33に部分的に重なるようにして、浮遊ゲート電極51が設けられてなる書き換え可能な不揮発性メモリトランジスタ100であって、ソース領域32とドレイン領域33を最短距離で結ぶ断面において、ドレイン領域33と浮遊ゲート電極51の重なり寸法Lが、0.15μm以上、0.5μm以下、である不揮発性メモリトランジスタ100とする。

(もっと読む)

半導体メモリの閾値設定方法

【課題】選択ゲートを持つセルアレイに関し、高密度セル配置を実現する。

【解決手段】本発明の例に係る半導体メモリの閾値設定方法は、絶縁体からなる電荷蓄積層を有する選択スイッチング素子及び絶縁体からなる電荷蓄積層を有するメモリセルから構成されるセルユニットを複数個有する半導体メモリを対象とし、選択スイッチング素子は、セレクトゲート電極と、セレクトゲート電極と電荷蓄積層との間に配置される第2の絶縁膜とを有し、選択スイッチング素子に対する消去時に、第2の絶縁膜に電子による電流が流れることにより、消去閾値が飽和することを特徴とする。

(もっと読む)

1 - 20 / 41

[ Back to top ]