Fターム[5F083LA03]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | センスアンプ (769)

Fターム[5F083LA03]に分類される特許

761 - 769 / 769

フラッシュ/ダイナミックランダムアクセスメモリフィールドプログラマブルゲートアレイ

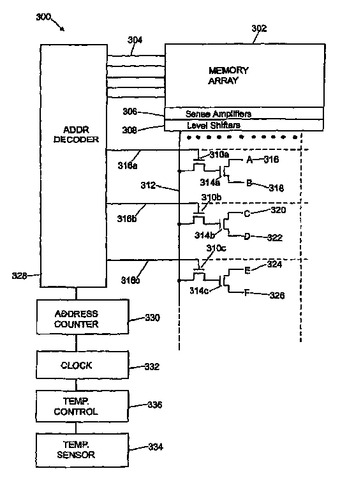

集積回路デバイスにおいて2つのノードを選択的に相互接続するための回路は、複数のワード線及び複数のビット線を有するメモリアレイを含む。リフレッシュトランジスタは複数のビット線のうち一本に接続されたソース、ダイナミックランダムアクセスメモリワード線に接続された制御ゲート、及びドレインを有する。スイッチトランジスタはリフレッシュトランジスタのドレインに接続されたゲート、一番目のノードに接続されたソース、及び二番目のノードに接続されたドレインを有する。アドレスデコーダはワード線とダイナミックランダムアクセスメモリワード線に周期信号を供給する。  (もっと読む)

(もっと読む)

SRAMセル構造及び回路

デバイスの漏れ電流の低減及び/又は速度の増大のためのSRAM回路構造に関する。

様々な形式のSRAMデバイスがシングルポート及びデュアルポートRAMデバイスのような技術を用いて製造されうる。一例として、SRAM構造は、別個の書き込み及び読み込みラインを使用し、回路を異なる閾値レベルを有することで利点を有しうる部分に分け、第一の端子及びソーストランジスタに接続された仮想ノードへの接続のための読み込み経路トランジスタを分けることを実現することができる。構造は、NMOS又はPMOSの組合せ又はNMOSのみでトランジスタを形成するのに特に良く適する。メモリ配列は、本発明により、基準読み込み経路及び検知ブロックが共有又は専用であると共に、多様な分割又は統合を成された配置で編成されても良い。  (もっと読む)

(もっと読む)

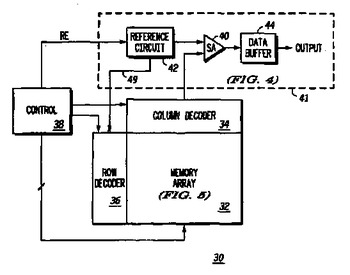

不揮発性メモリにおける基準トランジスタ用可変ゲート・バイアス

不揮発性メモリ(30)はナノクリスタルメモリセル(50、51、53)を備える。メモリセルトランジスタ(50、51、53)のプログラム及び消去閾値電圧は、プログラム/消去動作の回数の関数として上昇する。読み出し動作の間、基準トランジスタ(46)がセル電流と比較するための基準電流を供給する。基準トランジスタ(46)がナノクリスタルを含まないことを除いて、基準トランジスタ(46)は、メモリセルトランジスタ(50、51、53)を製造する際に用いるのと同様のプロセスで製造される。同様のプロセスを用いて基準トランジスタ(46)及びメモリセルトランジスタ(50、51、53)双方を製造することにより、基準トランジスタ(46)の閾値電圧は、メモリセルトランジスタ(50、51、53)の閾値電圧のずれに追従する。基準トランジスタ(46)のゲートにバイアスをかけるために、読み出し制御回路(42)が設けられている。読み出し制御回路(42)は、基準トランジスタ(46)のドレイン電流を検知し、基準電流をセル電流に対して実質的に一定値に維持するように、ゲートバイアス電圧を調節する。  (もっと読む)

(もっと読む)

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

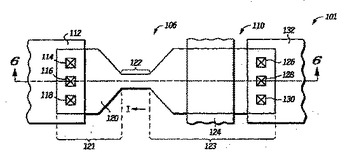

フューズ及びその形成方法

アクティブフューズはアクティブフューズ構造(120)を備え、この構造を使用して可変抵抗体(106)及び選択トランジスタ(110)の双方を形成する。一の実施形態では、アクティブフューズ構造は、半導体基板(140)の活性領域(160)の一部に形成され、選択ゲート(124)はアクティブフューズ構造の一方の端部(123)の上に配置されてアクティブフューズへの書き込みに使用する一体型選択トランジスタ(110)を形成する。共有型のアクティブフューズ構造を活性領域の内部に使用することによって、面積要件を縮小し、かつ検出マージンを大きくすることができる。  (もっと読む)

(もっと読む)

強誘電体膜およびその製造方法ならびに半導体装置

【課題】 低温の結晶化により良好な特性を有するBi層状ペロブスカイト構造を有する強誘電体膜の製造方法を提供する。

【解決手段】 本発明の強誘電体膜の製造方法は、第1の原料液と、第2の原料液とを含む強誘電体の原料液を結晶化することにより、強誘電体膜を形成する工程を含み、前記第1の原料液と前記第2の原料液とは、種類が異なる関係にあり、前記第1の原料液は、Bi系層状ペロブスカイト構造を有する強誘電体を生成するための原料液であり、前記第2の原料液は、AサイトがPbであるABO3系酸化物を生成するための原料液である。

(もっと読む)

半導体記憶装置

【課題】 多ビットのデータを入出力可能であって、動作速度の遅延や消費電力の増大を抑えたDRAMを提供する。

【解決手段】 このDRAMでは、多数のグローバル入出力線対GIOがサブワードドライバ領域24間のメモリセルアレイ上を走る。ローカル入出力線対LIOはメモリサブブロック26ごとに複数に分割される。グローバル入出力線対GIOとローカル入出力線対LIOを接続するスイッチング素子30はセンスアンプ領域22上に分散して配置される。1つのローカル入出力線対LIOには複数のビット線対が共通に接続される。

(もっと読む)

不揮発性半導体記憶装置

【課題】NANDセル型EEPROMのデータ消去後に、ビット線コンタクト部とセルPウエルとの接合の順方向電流によるラッチアップを防止する。

【解決手段】NANDセル型EEPROMにおいて、浮遊ゲートおよび制御ゲートを有する不揮発性のメモリセルを少なくとも1つ含むメモリセルユニットと、メモリセルユニットが形成されるメモリセルウエルCPWELL、CNWELLと、メモリセルユニットの一端に接続された第1の信号線BLi と、メモリセルユニットの他端に接続された第2の信号線CELSRCと、メモリセルの記憶データを消去する際、メモリセルウエルに消去電圧を所定期間印加して消去動作を行わせた後、第1の信号線および第2の信号線をフローティング状態にして、メモリセルウエルの消去電圧を放電させるように制御する制御回路を具備する。

(もっと読む)

半導体メモリーセル

【課題】 データに応じた電荷が、ランダムアクセス等に起因する干渉によってリークしないようする。

【解決手段】 書込ワード線WWrdの指示によって書込ビット線WBitのレベルに対応して電荷を蓄積する一方、読出ワード線RWrdの指示によって蓄積した電荷に応じて読出ビット線RBitのレベルを遷移させる半導体メモリーセルにおいて、書込ワード線WWrdを、接地線GNDと読出ワード線RWrdとの間に配列させる。

(もっと読む)

761 - 769 / 769

[ Back to top ]